REV. D–14–

AD7713

DIGITAL FILTERING

The AD7713’s digital filter behaves like a similar analog filter,

with a few minor differences.

First, since digital filtering occurs after the A-to-D conversion

process, it can remove noise injected during the conversion

process. Analog filtering cannot do this.

On the other hand, analog filtering can remove noise superimposed

on the analog signal before it reaches the ADC. Digital filtering

cannot do this, and noise peaks riding on signals near full scale

have the potential to saturate the analog modulator and digital

filter, even though the average value of the signal is within limits.

To alleviate this problem, the AD7713 has overrange headroom

built into the ⌺-⌬ modulator and digital filter, which allows over-

range excursions of 5% above the analog input range. If noise

signals are larger than this, consideration should be given to analog

input filtering or to reducing the input channel voltage so that its

full scale is half that of the analog input channel full scale. This will

provide an overrange capability greater than 100% at the expense

of reducing the dynamic range by 1 bit (50%).

Filter Characteristics

The cutoff frequency of the digital filter is determined by the value

loaded to Bits FS0 to FS11 in the control register. At the maxi-

mum clock frequency of 2 MHz, the minimum cutoff frequency of

the filter is 0.52 Hz, while the maximum programmable cutoff

frequency is 53.9 Hz.

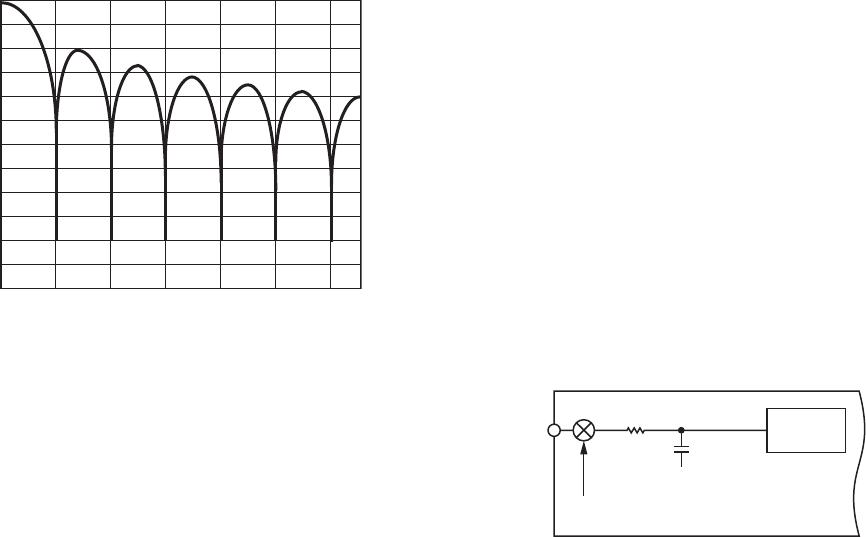

Figure 6 shows the filter frequency response for a cutoff frequency

of 0.52 Hz, which corresponds to a first filter notch frequency of

2 Hz. This is a (sinx/x)

3

response (also called sinc

3

) that provides

>100 dB of 50 Hz and 60 Hz rejection. Programming a differ-

ent cutoff frequency via FS0 to FS11 does not alter the profile

of the filter response; it changes the frequency of the notches as

outlined in the Control Register section.

–240

–180

–200

–220

–60

–80

–100

–120

–140

–160

0

–20

–40

024681012

FREQUENCY (Hz)

GAIN (dB)

Figure 6. Frequency Response of AD7713 Filter

Since the AD7713 contains this on-chip, low-pass filtering,

there is a settling time associated with step function inputs, and

data on the output will be invalid after a step change until the

settling time has elapsed. The settling time depends upon the

notch frequency chosen for the filter. The output data rate

equates to this filter notch frequency, and the settling time of

the filter to a full-scale step input is four times the output data

period. In applications using both input channels, the settling

time of the filter must be allowed to elapse before data from the

second channel is accessed.

Post Filtering

The on-chip modulator provides samples at a 3.9 kHz output

rate. The on-chip digital filter decimates these samples to

provide data at an output rate that corresponds to the pro-

grammed first notch frequency of the filter. Since the output

data rate exceeds the Nyquist criterion, the output rate for a

given bandwidth will satisfy most application requirements.

However, there may be some applications that require a higher

data rate for a given bandwidth and noise performance. Appli-

cations that need this higher data rate will require some post

filtering following the digital filter of the AD7713.

For example, if the required bandwidth is 1.57 Hz but the required

update rate is 20 Hz, the data can be taken from the AD7713 at

the 20 Hz rate giving a –3 dB bandwidth of 5.24 Hz. Post filtering

can be applied to this to reduce the bandwidth and output noise,

to the 1.57 Hz bandwidth level, while maintaining an output rate

of 20 Hz.

Post filtering can also be used to reduce the output noise from

the device for bandwidths below 0.52 Hz. At a gain of 128, the

output rms noise is 250 nV. This is essentially device noise or

white noise, and since the input is chopped, the noise has a flat

frequency response. By reducing the bandwidth below 0.52 Hz,

the noise in the resultant pass band can be reduced. A reduction

in bandwidth by a factor of 2 results in a √2 reduction in the

output rms noise. This additional filtering will result in a longer

settling time.

Antialias Considerations

The digital filter does not provide any rejection at integer

multiples of the modulator sample frequency (n ⫻ 3.9 kHz,

where n = 1, 2, 3...). This means that there are frequency

bands, ±f

3

dB wide (f

3

dB is cutoff frequency selected by FS0

to FS11), where noise passes unattenuated to the output.

However, due to the AD7713’s high oversampling ratio, these

bands occupy only a small fraction of the spectrum, and most

broadband noise is filtered. In any case, because of the high

oversampling ratio, a simple, RC, single-pole filter is generally

sufficient to attenuate the signals in these bands on the analog

input and thus provide adequate antialiasing filtering.

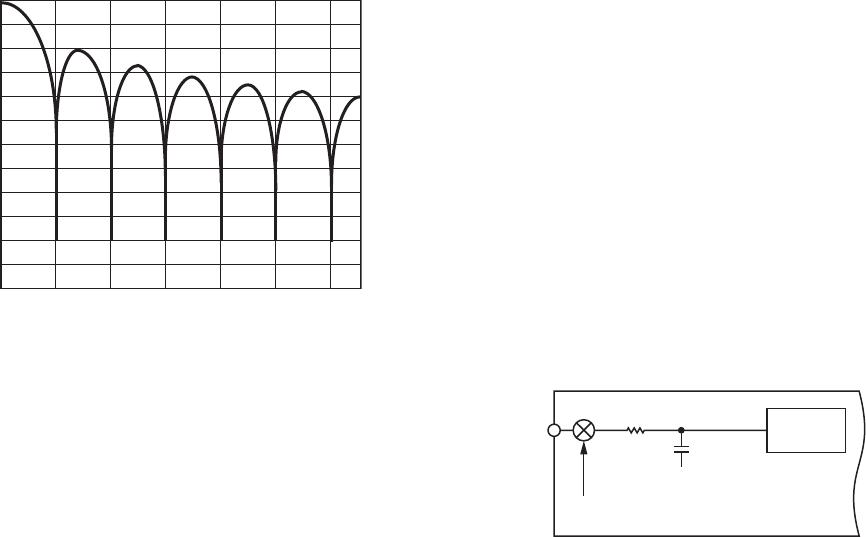

If passive components are placed in front of the AIN1 and

AIN2 inputs of the AD7713, care must be taken to ensure that

the source impedance is low enough so as not to introduce

gain errors in the system. The dc input impedance for the

AIN1 and AIN2 inputs is over 1 GΩ. The input appears as a

dynamic load that varies with the clock frequency and with the

selected gain (see Figure 7). The input sample rate, as shown

in Table III, determines the time allowed for the analog input

capacitor, C

IN

, to be charged. External impedances result in a

longer charge time for this capacitor, which result in gain er-

rors being introduced on the analog inputs. Both inputs of the

differential input channels look into similar input circuitry.

AIN

HIGH

IMPEDANCE

> 1G

⍀

R

INT

(7k⍀ TYP)

C

INT

(11.5pF TYP)

SWITCHING FREQUENCY DEPENDS ON

f

CLKIN

AND SELECTED GAIN

V

BIAS

Figure 7. AIN1, AIN2 Input Impedance