2 µs

clk0

clk1

sel

outn

1

0

ZL40221 Data Sheet

7

Microsemi Corporation

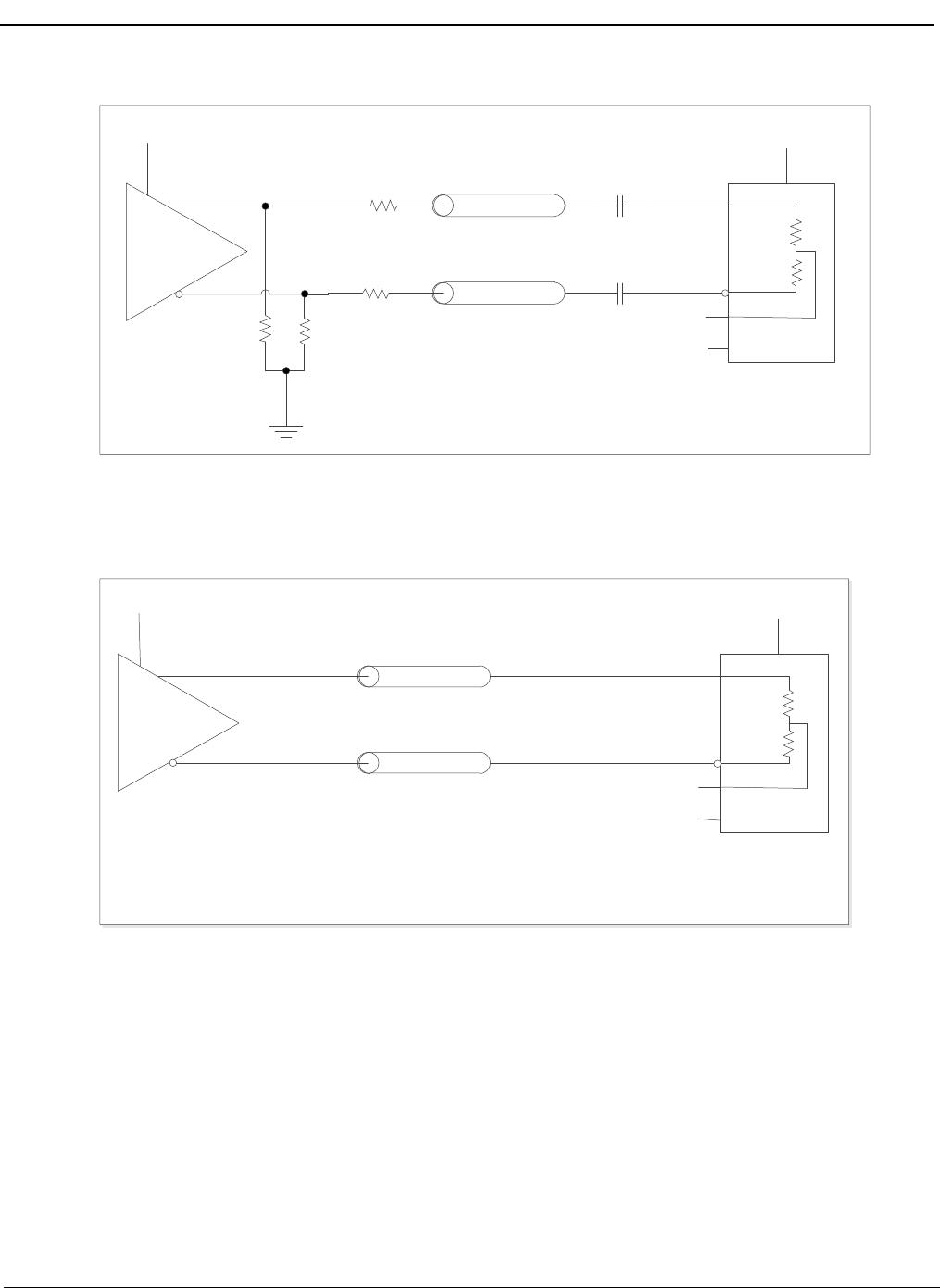

Figure 4 - Output During Clock Switch - Both Clocks Running

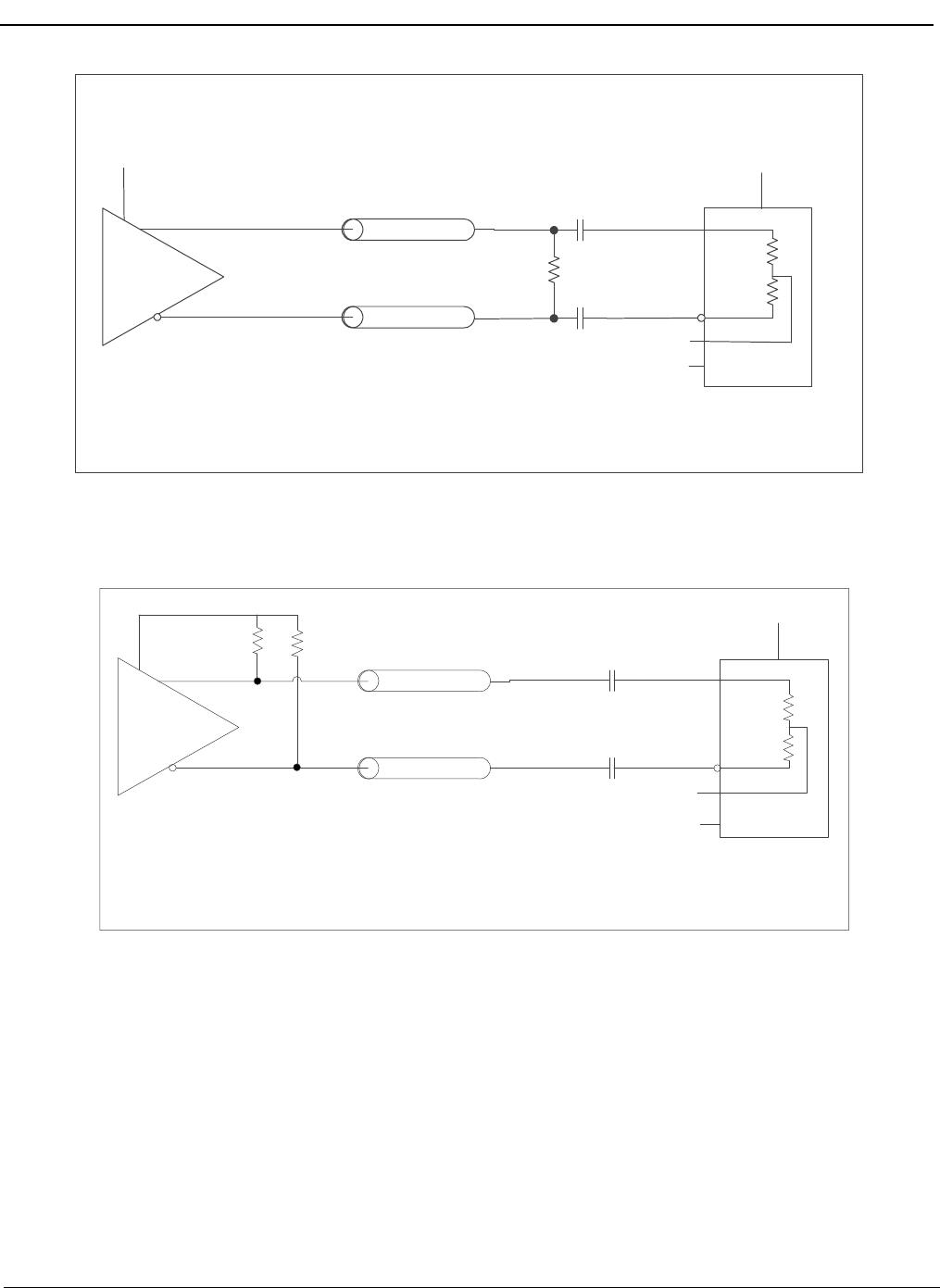

3.1.2 Clock Input Terminations

This following figures give the components values and configuration for the various circuits compatible with the

input stage and the use of the Vt and ctrl pins in each case.

In the following diagrams were the ct

rl pin is ’1’ and the Vt pin is not connected, the Vt pin can be instead connected

to V

DD

with a capacitor. A capacitor can also help in Figure 5 between Vt and V

DD

. This capacitor will minimize the

noise at the point between the two internal termination resistor

s and improve the overall performance of the device.

LVPECL

Driver

R

VDD_driver

VDD

Z

o

= 50 Ohms

Z

o

= 50 Ohms

k

t

clk_p

clk_n

Vt

Ctrl

“0”

For 3.3 V: R= 50 Ohms

For 2.5 V: R= 22 Ohms

22 Ohms

22 Ohms

Figure 5 - Clock Input - LVPECL - DC Coupled