© 2008 Microchip Technology Inc. DS21073K-page 11

24AA65/24LC65/24C65

7.0 PAGE CACHE AND ARRAY

MAPPING

The cache is a 64-byte (8 pages x 8 bytes) FIFO buffer.

The cache allows the loading of up to 64 bytes of data

before the write cycle is actually begun, effectively

providing a 64-byte burst write at the maximum bus

rate. Whenever a Write command is initiated, the cache

starts loading and will continue to load until a Stop bit is

received to start the internal write cycle. The total

length of the write cycle will depend on how many

pages are loaded into the cache before the Stop bit is

given. Maximum cycle time for each page is 5 ms. Even

if a page is only partially loaded, it will still require the

same cycle time as a full page. If more than 64 bytes of

data are loaded before the Stop bit is given, the

Address Pointer will ‘wrap around’ to the beginning of

cache page 0 and existing bytes in the cache will be

overwritten. The device will not respond to any

commands while the write cycle is in progress.

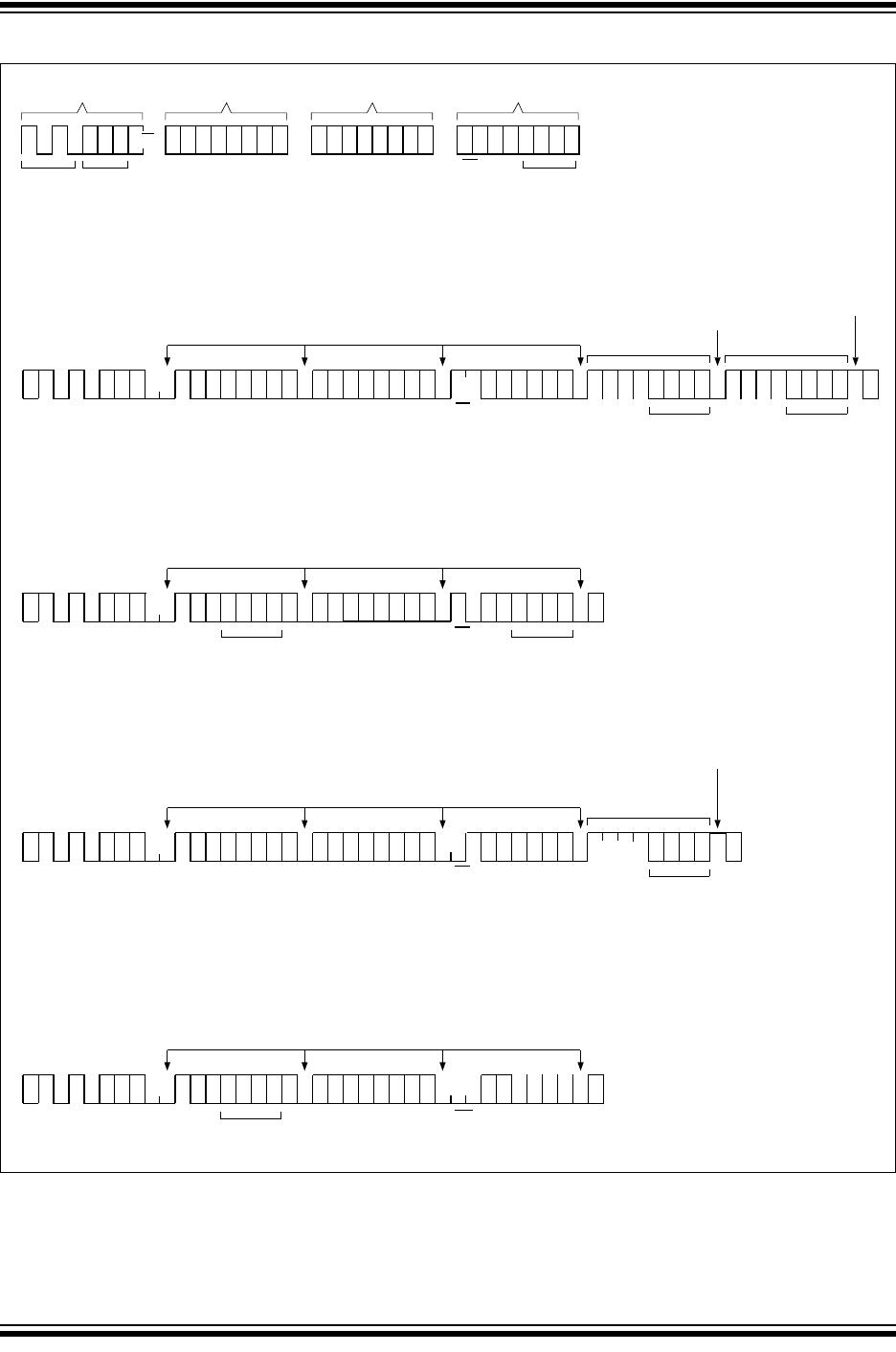

7.1 Cache Write Starting at a Page

Boundary

If a Write command begins at a page boundary

(address bits A2, A1 and A0 are zero), then all data

loaded into the cache will be written to the array in

sequential addresses. This includes writing across a

4K block boundary. In the example shown below,

(Figure 8-2) a Write command is initiated starting at

byte 0 of page 3 with a fully loaded cache (64 bytes).

The first byte in the cache is written to byte 0 of page 3

(of the array), with the remaining pages in the cache

written to sequential pages in the array. A write cycle is

executed after each page is written. Since the write

begins at page 3 and 8 pages are loaded into the

cache, the last 3 pages of the cache are written to the

next row in the array.

7.2 Cache Write Starting at a

Non-Page Boundary

When a Write command is initiated that does not begin

at a page boundary (i.e., address bits A2, A1 and A0

are not all zero), it is important to note how the data is

loaded into the cache, and how the data in the cache is

written to the array. When a Write command begins, the

first byte loaded into the cache is always loaded into

page 0. The byte within page 0 of the cache where the

load begins is determined by the three Least Significant

Address bits (A2, A1, A0) that were sent as part of the

Write command. If the Write command does not start at

byte 0 of a page and the cache is fully loaded, then the

last byte(s) loaded into the cache will roll around to

page 0 of the cache and fill the remaining empty bytes.

If more than 64 bytes of data are loaded into the cache,

data already loaded will be overwritten. In the example

shown in Figure 8-3, a Write command has been

initiated starting at byte 2 of page 3 in the array with a

fully loaded cache of 64 bytes. Since the cache started

loading at byte 2, the last two bytes loaded into the

cache will ‘roll over' and be loaded into the first two

bytes of page 0 (of the cache). When the Stop bit is

sent, page 0 of the cache is written to page 3 of the

array. The remaining pages in the cache are then

loaded sequentially to the array. A write cycle is

executed after each page is written. If a partially loaded

page in the cache remains when the Stop bit is sent,

only the bytes that have been loaded will be written to

the array.

7.3 Power Management

The design incorporates a power Standby mode when

not in use and automatically powers off after the normal

termination of any operation when a Stop bit is received

and all internal functions are complete. This includes

any error conditions (i.e., not receiving an Acknowl-

edge or Stop condition per the two-wire bus specifica-

tion). The device also incorporates V

DD monitor

circuitry to prevent inadvertent writes (data corruption)

during low voltage conditions. The VDD monitor circuitry

is powered off when the device is in Standby mode in

order to further reduce power consumption.

8.0 PIN DESCRIPTIONS

8.1 A0, A1, A2 Chip Address Inputs

The A0..A2 inputs are used by the 24XX65 for multiple

device operation and conform to the two-wire bus

standard. The levels applied to these pins define the

address block occupied by the device in the address

map. A particular device is selected by transmitting the

corresponding bits (A2, A1, A0) in the control byte

(Figure 3-2 and Figure 8-1).

8.2 SDA Serial Address/Data Input/

Output

This is a bidirectional pin used to transfer addresses

and data into and data out of the device. It is an open

drain terminal, therefore the SDA bus requires a pull-up

resistor to V

CC (typical 10 KΩ for 100 kHz, 2 KΩ for 400

kHz).

For normal data transfer SDA is allowed to change only

during SCL low. Changes during SCL high are

reserved for indicating the Start and Stop conditions.

8.3 SCL Serial Clock

This input is used to synchronize the data transfer from

and to the device.