ZL30100 Data Sheet

6

Zarlink Semiconductor Inc.

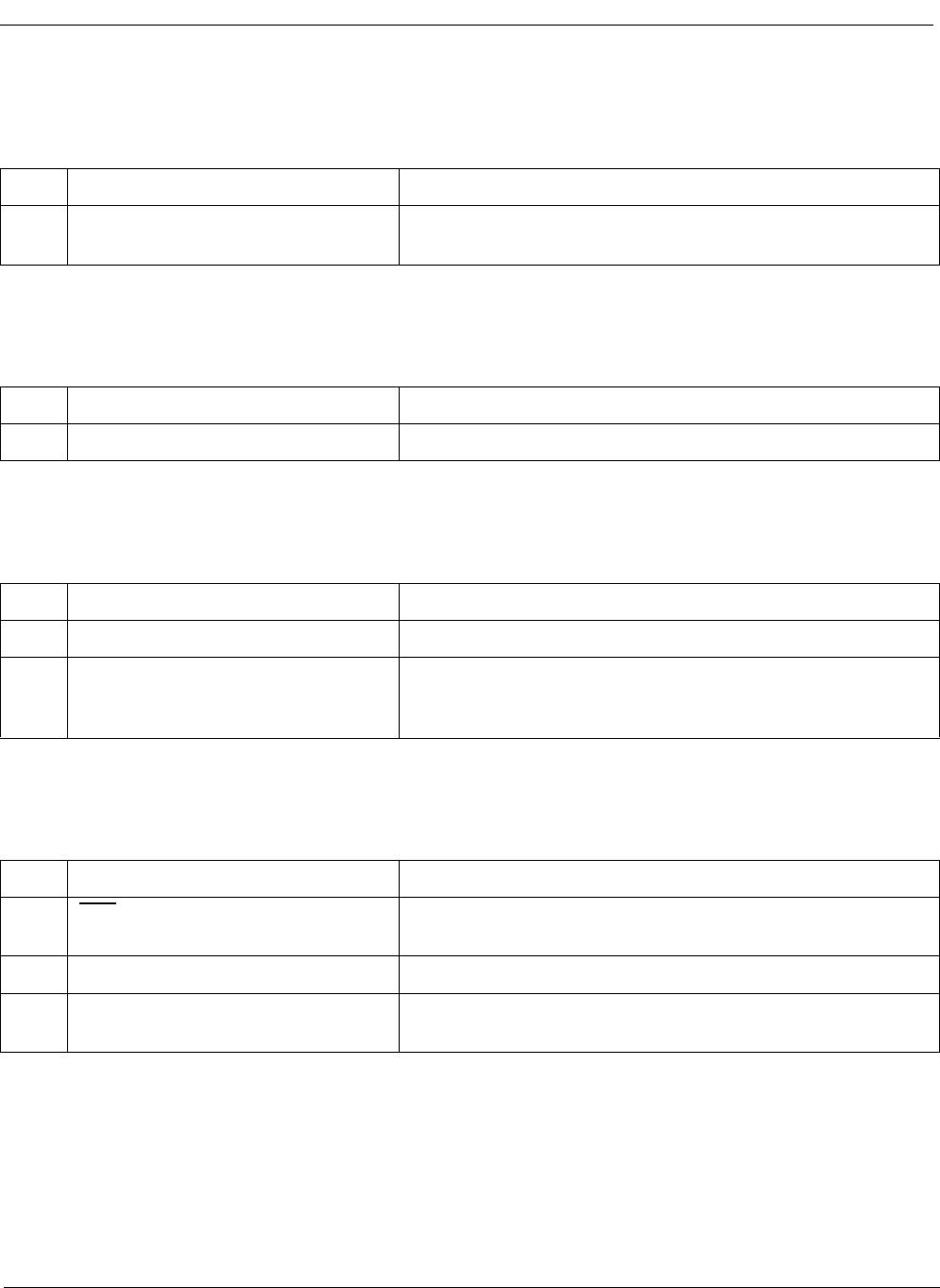

Changes from June 2004 Issue to September 2004 Issue. Page, section, figure and table numbers refer to this

current issue.

Page Item Change

1 Text Jitter changed to 0.6 ns from 0.5 ns

7 Figure 2 Added note specifying not e-Pad

8 Table “Pin Description“ Added information about Schmitt trigger feedback paths to

C1.5o, C2o, C16o

, and F8/F32o

11 Section 3.2 Added text about input pulse width restriction

16 Section 3.4 Added details to "Lock Indicator" on LOCK pin behaviour

20 Section 4.5 Added text and Figure 11 explaining LOCK pin behaviour

21 Section 5.0 Added Jitter definition

27 Table “Absolute Maximum Ratings*“ Corrected package power rating

28 Table “DC Electrical Characteristics*“ Corrected current consumption

Corrected input voltage characteristics to reflect Schmitt trigger

Corrected input leakage current to reflect internal pull-ups

Corrected output voltage note to reflect two pad strengths

29 Table “AC Electrical Characteristics* -

Input timing for REF0 and REF1

references (see Figure 16)“

Added explanatory note

34 Table “Performance Characteristics*:

Output Jitter Generation - ANSI

T1.403 Conformance“

Changed jitter numbers

34 Table “Performance Characteristics*:

Output Jitter Generation - ITU-T

G.812 Conformance“

Changed jitter number

34 Table “Performance Characteristics* -

Unfiltered Intrinsic Jitter“

Changed jitter numbers, removed UI column