DS564F2 15

CS5341

Confidential Draft

3/11/08

4. APPLICATIONS

4.1 Single-, Double-, and Quad-Speed Modes

The CS5341 can support output sample rates from 2 kHz to 200 kHz. The proper speed mode can be de-

termined by the desired output sample rate and the external MCLK/LRCK ratio, as shown in Table 1.

Table 1. Speed Modes and the Associated Output Sample Rates (Fs)

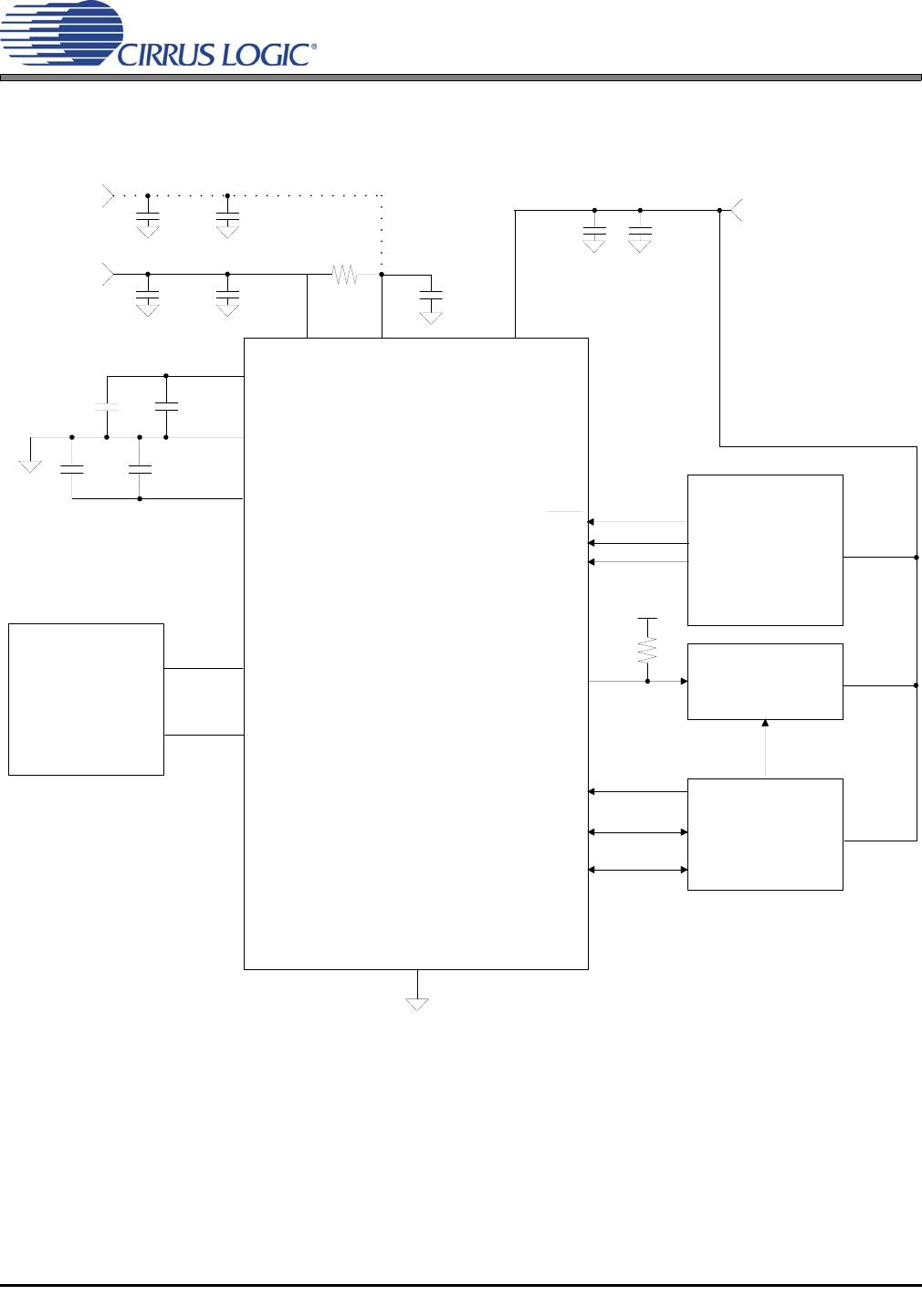

4.2 Operation as Either a Clock Master or Slave

The CS5341 supports operation as either a clock master or slave. As a clock master, the LRCK and SCLK

pins are outputs with the left/right and serial clocks synchronously generated on-chip. As a clock slave, the

LRCK and SCLK pins are inputs and require the left/right and serial clocks to be externally generated. The

selection of clock master or slave is made via the Mode pins as shown in Table 2.

Speed Mode

MCLK/LRCK

Ratio

Output Sample Rate Range (kHz)

Single-Speed Mode

512x 43 - 50

256x 2 - 50

Double-Speed Mode

256x 86 - 100

128x 4 - 100

Quad-Speed Mode

128x 172 - 200

64x* 100 - 200

* Quad-Speed Mode, 64x only available in Master Mode.

M1 (Pin 16) M0 (Pin 1) MODE

00

Clock Master, Single-Speed Mode

01

Clock Master, Double-Speed Mode

10

Clock Master, Quad-Speed Mode

11

Clock Slave, All Speed Modes

Table 2. CS5341 Mode Control