18 DS564F2

CS5341

Confidential Draft

3/11/08

4.4 Power-Up Sequence

Reliable power-up can be accomplished by keeping the device in reset until the power supplies, clocks and

configuration pins are stable. It is also recommended that reset be enabled if the analog or digital supplies

drop below the minimum specified operating voltages to prevent power-glitch-related issues.

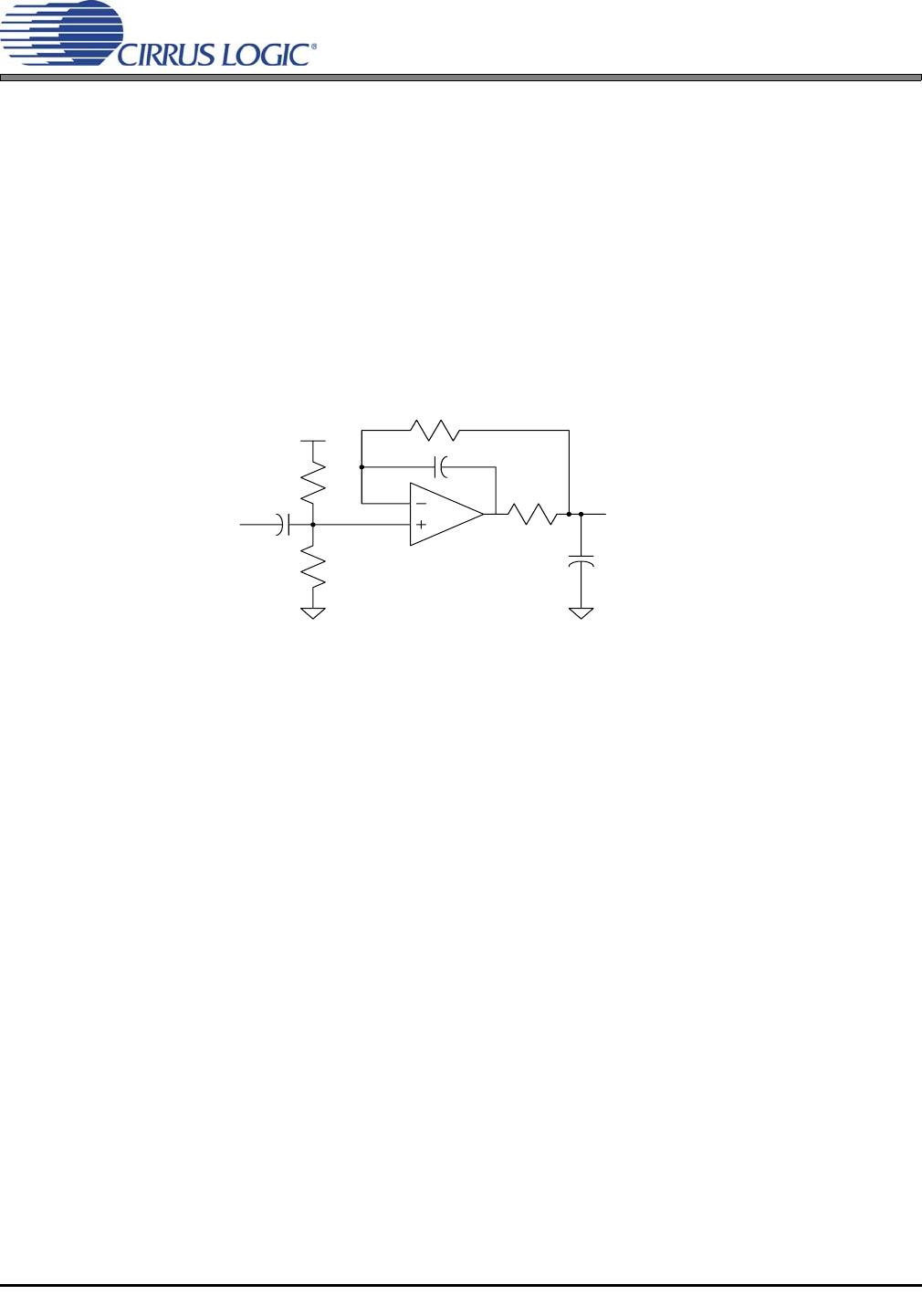

4.5 Analog Connections

The analog modulator samples the input at half of the MCLK frequency, or nominally 6.144 MHz. The digital

filter will reject signals within the stopband of the filter. However, there is no rejection for input signals which

are multiples of the input sampling frequency (n

× 6.144 MHz), where n=0,1,2,... Refer to Figure 21, which

shows the suggested filter that will attenuate any noise energy at 6.144 MHz in addition to providing the op-

timum source impedance for the modulators. The use of capacitors that have a large voltage coefficient

(such as general-purpose ceramics) must be avoided since these can degrade signal linearity.

4.6 Grounding and Power Supply Decoupling

As with any high resolution converter, achieving optimal performance from the CS5341 requires careful at-

tention to power supply and grounding arrangements. Figure 17 shows the recommended power arrange-

ments, with VA and VL connected to clean supplies. VD, which powers the digital filter, may be run from the

system logic supply or may be powered from the analog supply via a resistor. In this case, no additional

devices should be powered from VD. Decoupling capacitors should be as near to the ADC as possible, with

the low-value ceramic capacitor being the nearest. All signals, especially clocks, should be kept away from

the FILT+ and VQ pins in order to avoid unwanted coupling into the modulators. The FILT+ and VQ decou-

pling capacitors, particularly the 0.01 µF, must be positioned to minimize the electrical path from FILT+ and

REF_GND. Furthermore, all ground pins on CS5341 should be referenced to the same ground reference.

The CDB5341 evaluation board demonstrates the optimum layout and power supply arrangements. To min-

imize digital noise, connect the ADC digital outputs only to CMOS inputs.

4.7 Synchronization of Multiple Devices

In systems where multiple ADCs are required, the user can achieve simultaneous sampling if the MCLK and

LRCK signals are the same for all of the CS5341’s in the system. If only one master clock source is needed,

one solution is to place one CS5341 in Master Mode, and slave all of the other CS5341’s to the one master.

If multiple master clock sources are needed, a possible solution would be to supply all clocks from the same

external source and time the CS5341 reset with the inactive (falling) edge of MCLK. This will ensure that all

converters begin sampling on the same clock edge.

VA

4.7 µF

470 pF

C0G

2700 pF

CS5341 AINx

AINx

100 kΩ

100 kΩ

634 Ω

91 Ω

Figure 21. CS5341 Recommended Analog Input Buffer