L9954 / L9954XP Functional description of the SPI

Doc ID 14279 Rev 4 25/37

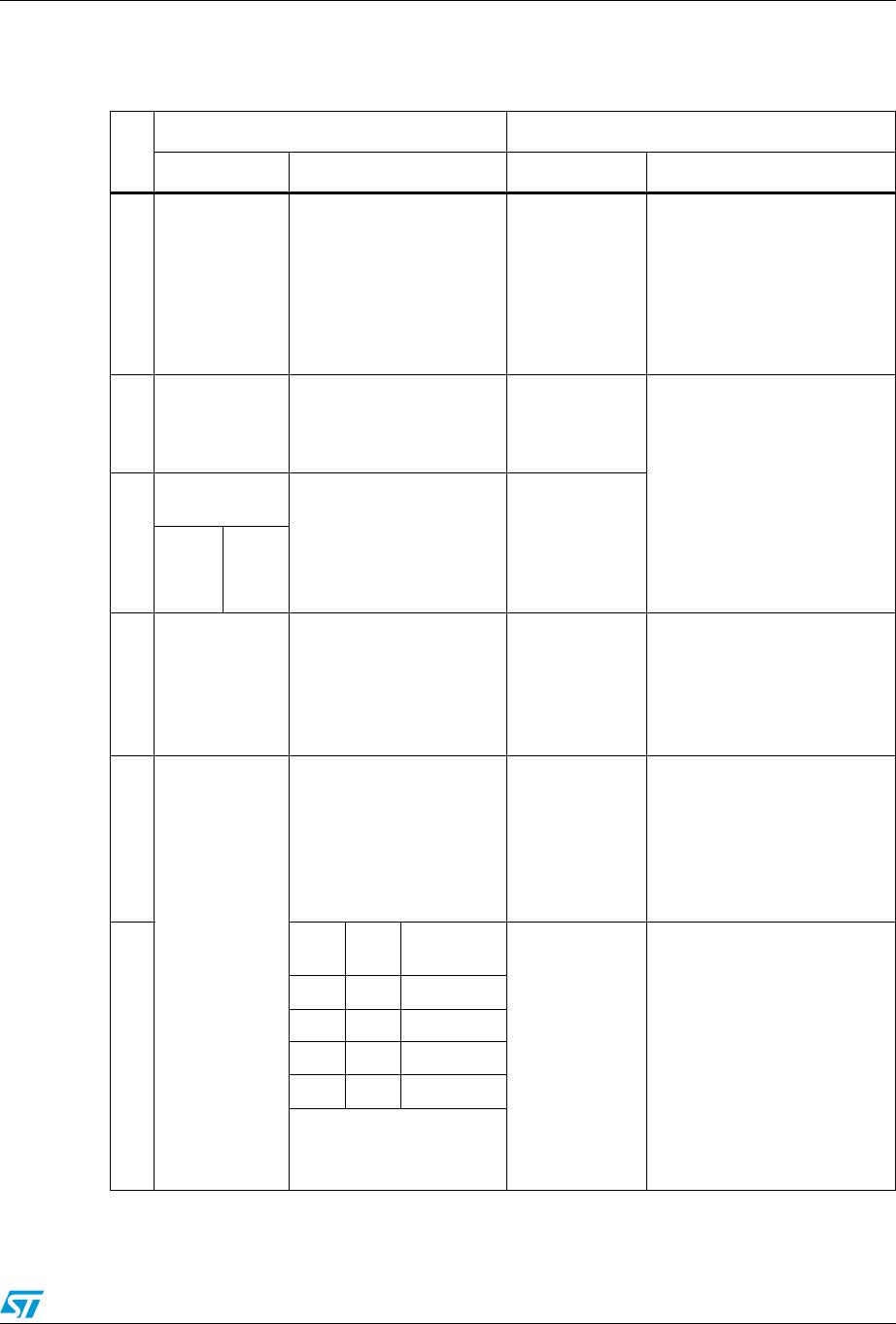

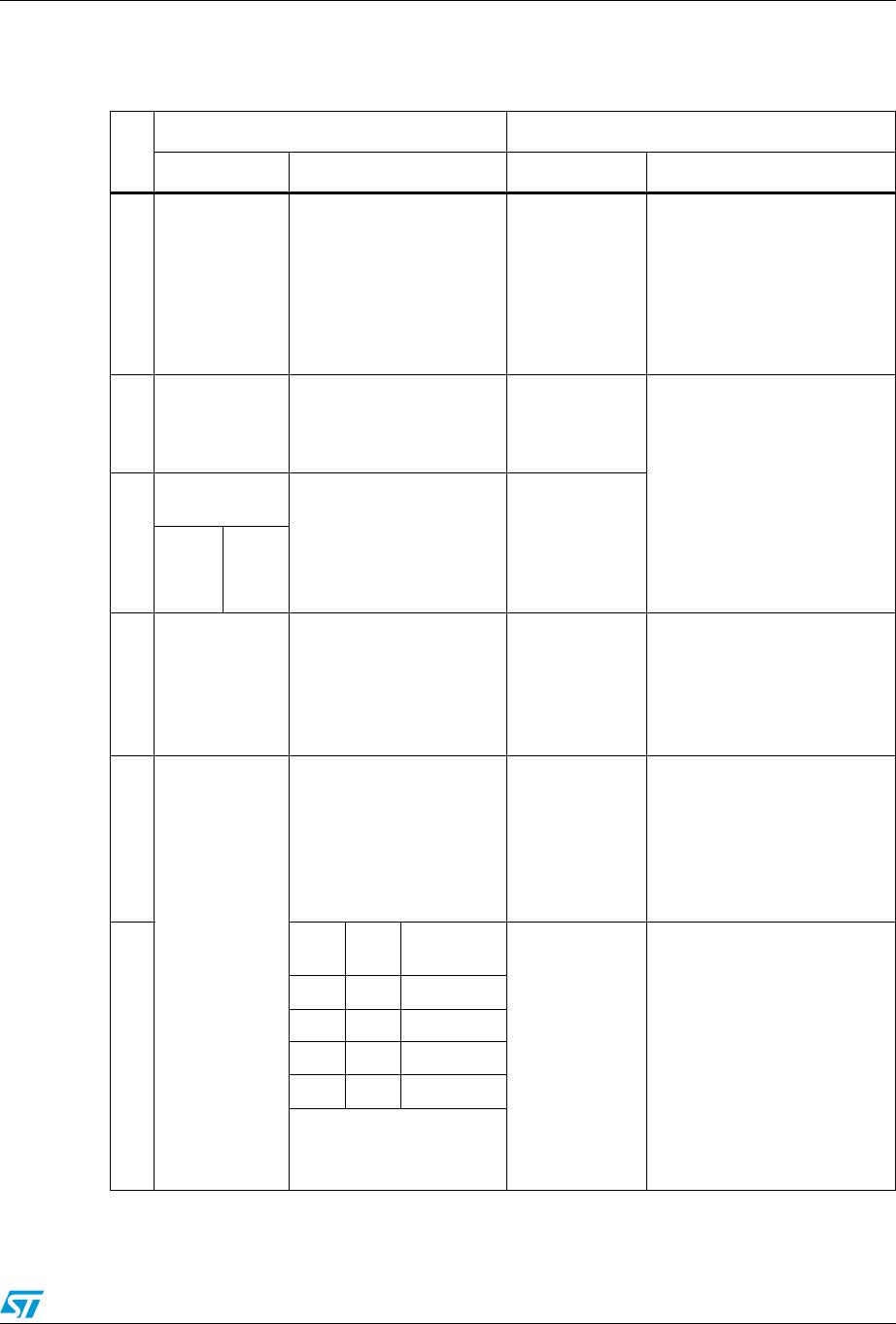

4.8 SPI - Input data and status registers

Table 18. SPI - input data and status registers 0

Bit

Input register 0 (write) Status register 0 (read)

Name Comment Name Comment

23 Enable bit

If Enable Bit is set the

device switches in active

mode. If Enable Bit is

cleared the device goes

into standby mode and all

bits are cleared. After

power-on reset device

starts in standby mode.

Always 1

A broken VCC-or SPI-

connection of the L9954 can

be detected by the

microcontroller, because all 24

bits low or high is not a valid

frame.

22 Reset bit

If Reset Bit is set both

status registers will be

cleared after rising edge of

CSN input.

V

S

overvoltage

In case of an overvoltage or

undervoltage event the

corresponding bit is set and

the outputs are deactivated. If

VS voltage recovers to normal

operating conditions outputs

are reactivated automatically

(if Bit 20 of status register 0 is

not set).

21

OC recovery

duty cycle

This bit defines in

combination with the over-

current recovery bit (Input

Register 1) the duty cycle

in over-current condition of

an activated driver.

V

S

undervoltage

0: 12% 1: 25%

20

Overvoltage/

Undervoltage

recovery

disable

If this bit is set the

microcontroller has to

clear the status register

after undervoltage /

overvoltage event to

enable the outputs.

Thermal

shutdown

In case of a thermal shutdown

all outputs are switched off.

The microcontroller has to

clear the TSD bit by setting the

Reset Bit to reactivate the

outputs.

19

Current monitor

select bits

Depending on

combination of bit 18 and

19 the current image

(1/10.000) of the selected

HS-output will be

multiplexed to the CM

output:

Temperature

warning

The TW bit can be used for

thermal management

by the microcontroller to avoid

a thermal shutdown. The

microcontroller has to clear the

TW bit.

18

Bit

19

Bit

18

Output

Not ready bit

After switching the device from

standby mode to active mode

an internal timer is started to

allow chargepump to settle

before the outputs can be

activated. This bit is cleared

automatically after start up

time has finished. Since this bit

is controlled by internal clock it

can be used for synchronizing

testing events (e.g. measuring

filter times).

00 OUT6

10 OUT1

01 OUT4

11 OUT5