13

LTC1419

1419fb

APPLICATIONS INFORMATION

WUU

U

applied to the –A

IN

input. For zero offset error, apply

–152µV (i.e., – 0.5LSB) at +A

IN

and adjust the offset at the

–A

IN

input until the output code flickers between 0000

0000 0000 00 and 1111 1111 1111 11. For full-scale

adjustment, an input voltage of 2.499544V (FS/2 – 1.5LSBs)

is applied to +A

IN

and R2 is adjusted until

the output code flickers between 0111 1111 1111 10 and

0111 1111 1111 11.

BOARD LAYOUT AND GROUNDING

Wire wrap boards are not recommended for high resolu-

tion or high speed A/D converters. To obtain the best

performance from the LTC1419, a printed circuit board

with ground plane is required. Layout should ensure that

digital and analog signal lines are separated as much as

possible. Particular care should be taken not to run any

digital track alongside an analog signal track or under-

neath the ADC.The analog input should be screened by

AGND.

An analog ground plane separate from the logic system

ground should be established under and around the ADC.

Pin 5 (AGND), Pin 14 and Pin 19 (ADC’s DGND) and all

other analog grounds should be connected to this single

analog ground point. The REFCOMP bypass capacitor and

the DV

DD

bypass capacitor should also be connected to

this analog ground plane. No other digital grounds should

be connected to this analog ground plane. Low impedance

analog and digital power supply common returns are

essential to low noise operation of the ADC and the foil

width for these tracks should be as wide as possible. In

applications where the ADC data outputs and control

signals are connected to a continuously active micropro-

cessor bus, it is possible to get errors in the conversion

results. These errors are due to feedthrough from the

microprocessor to the successive approximation com-

parator. The problem can be eliminated by forcing the

microprocessor into a WAIT state during conversion or by

using three-state buffers to isolate the ADC data bus. The

traces connecting the pins and bypass capacitors must be

kept short and should be made as wide as possible.

The LTC1419 has differential inputs to minimize noise

coupling. Common mode noise on the +A

IN

and –A

IN

leads will be rejected by the input CMRR. The –A

IN

input

can be used as a ground sense for the +A

IN

input; the

LTC1419 will hold and convert the difference voltage

between +A

IN

and – A

IN

. The leads to + A

IN

(Pin 1) and – A

IN

(Pin 2) should be kept as short as possible. In applications

where this is not possible, the + A

IN

and – A

IN

traces should

be run side by side to equalize coupling.

SUPPLY BYPASSING

High quality, low series resistance ceramic, 10µF bypass

capacitors should be used at the V

DD

and REFCOMP pins

as shown in the Typical Application on the fist page of this

data sheet. Surface mount ceramic capacitors such as

Murata GRM235Y5V106Z016 provide excellent bypass-

ing in a small board space. Alternatively, 10µF tantalum

capacitors in parallel with 0.1µF ceramic capacitors can be

used. Bypass capacitors must be located as close to the

pins as possible. The traces connecting the pins and the

bypass capacitors must be kept short and should be made

as wide as possible.

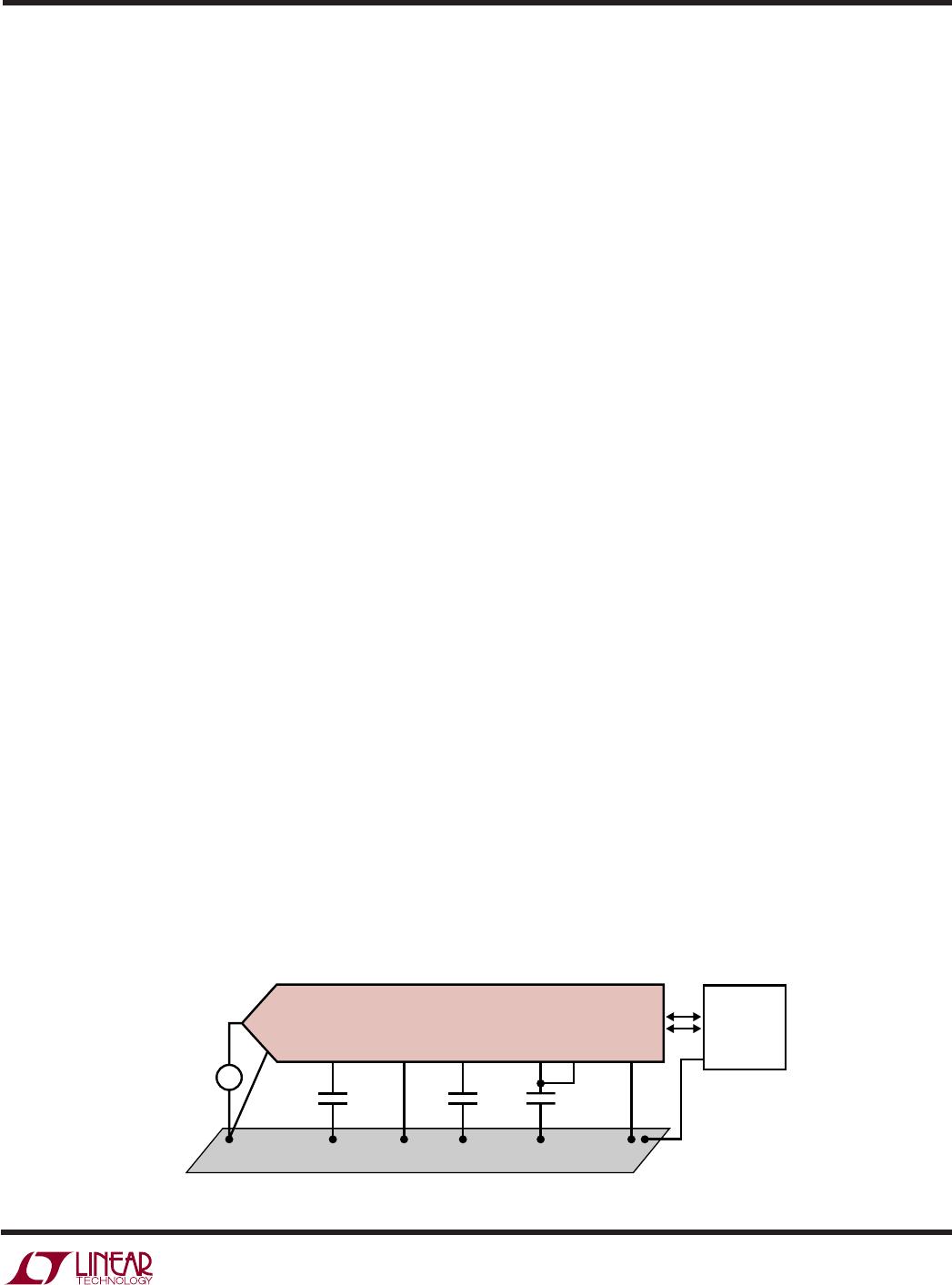

Example Layout

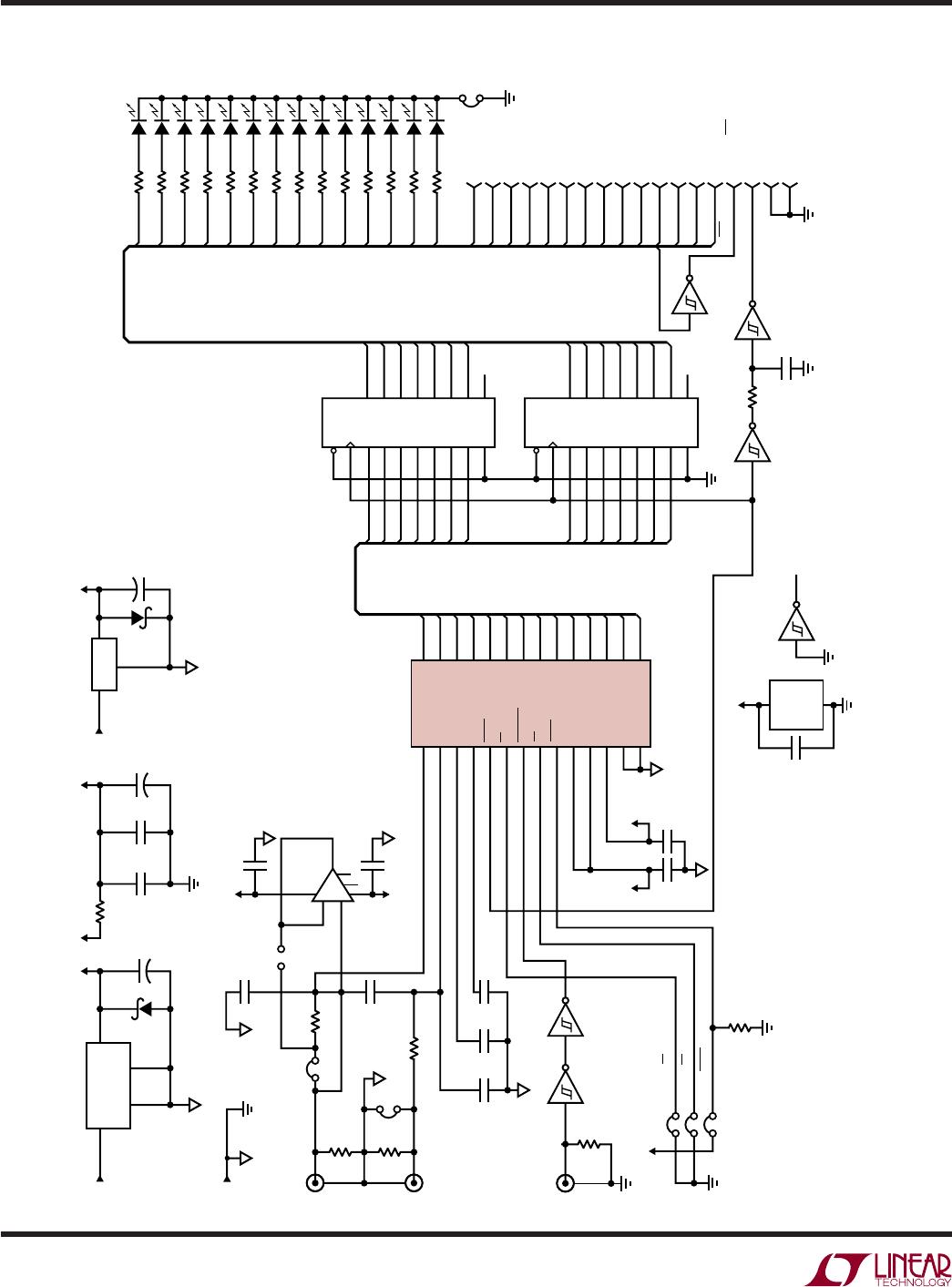

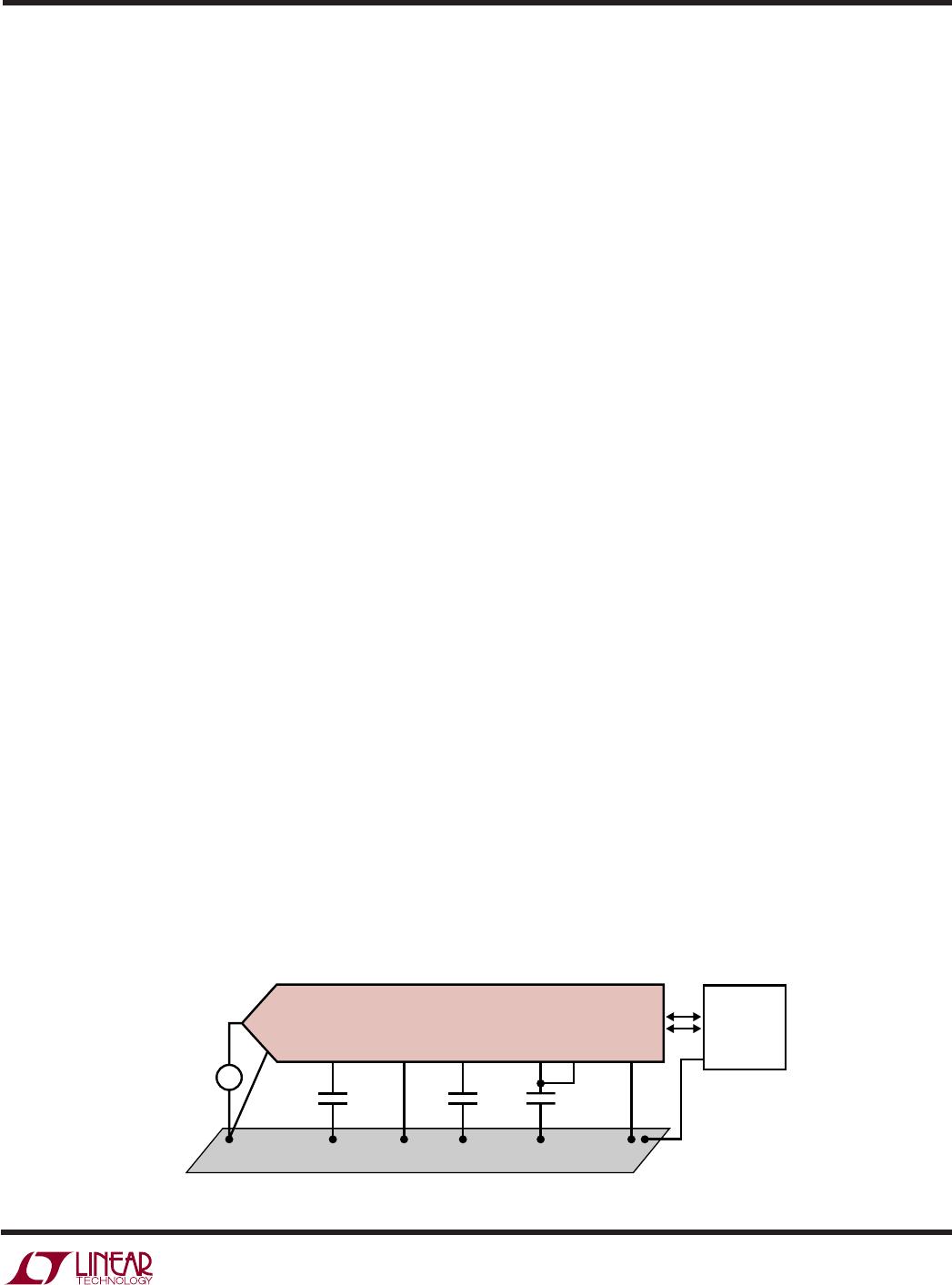

Figures 13a, 13b, 13c and 13d show the schematic and

layout of a suggested evaluation board. The layout demon-

strates the proper use of decoupling capacitors and ground

plane with a 2-layer printed circuit board.

Figure 12. Power Supply Grounding Practice

1419 F12

+A

IN

AGNDREFCOMP V

SS

AV

DD

LTC1419

DIGITAL

SYSTEM

ANALOG

INPUT

CIRCUITRY

54

2

26 28

DV

DD

27

DGND

14

1

10µF

–A

IN

10µF

10µF

ANALOG GROUND PLANE

+

–