1

100V, 2A Peak, High Frequency Half-Bridge Drivers with

Adjustable Dead Time Control and PWM Input

HIP2120, HIP2121

The HIP2120 and HIP2121 are 100V, high frequency, half-bridge

MOSFET driver ICs. They are based on the popular ISL2100A and

ISL2101A half-bridge drivers.

These drivers have a programmable dead-time to insure

break-before-make operation between the high-side and low-side

drivers. The dead-time is adjustable up to 250ns.

A single PWM logic input controls both bridge outputs (HO, LO). An

enable pin (EN), when low, drives both outputs to a low state. All

logic inputs are V

DD

tolerant and the HIP2120 has CMOS inputs

with hysteresis for superior operation in noisy environments.

The HIP2120 has hysteretic inputs with thresholds that are

proportional to V

DD

. The HIP2121 has 3.3V logic/TTL compatible

inputs.

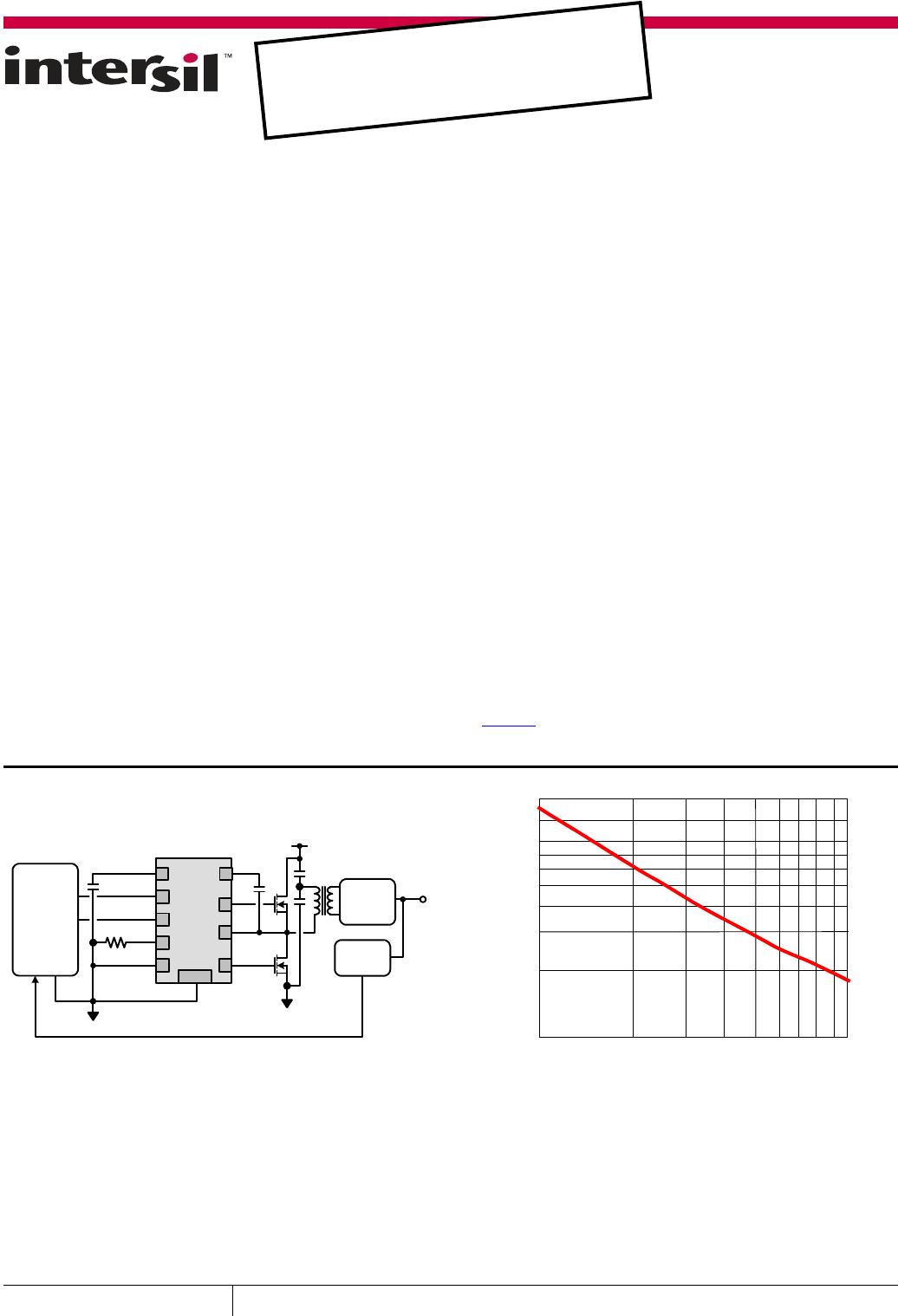

Two package options are provided. The 10 Ld 4x4 DFN package has

standard pinouts. The 9 Ld 4x4 DFN package omits pin 2 to comply

with 100V conductor spacing per IPC-2221.

Features

• 9 Ld TDFN “B” Package Compliant with 100V Conductor

Spacing Guidelines per IPC-2221

• Break-Before-Make Dead-Time Prevents Shoot-through and is

adjustable up to 220ns

• Bootstrap Supply Max Voltage to 114VDC

• Wide Supply Voltage Range (8V to 14V)

• Supply Undervoltage Protection

• CMOS Compatible Input Thresholds with Hysteresis (HIP2120)

•1.6/1 Typical Output Pull-up/Pull-down Resistance

•On-Chip 1 Bootstrap Diode

Applications

• Telecom Half-Bridge DC/DC Converters

•UPS and Inverters

•Motor Drives

• Class-D Amplifiers

• Forward Converter with Active Clamp

Related Literature

• FN7670 “HIP2122, HIP2123 100V, 2A Peak, High Frequency

Half-Bridge Driver with Delay Timers”

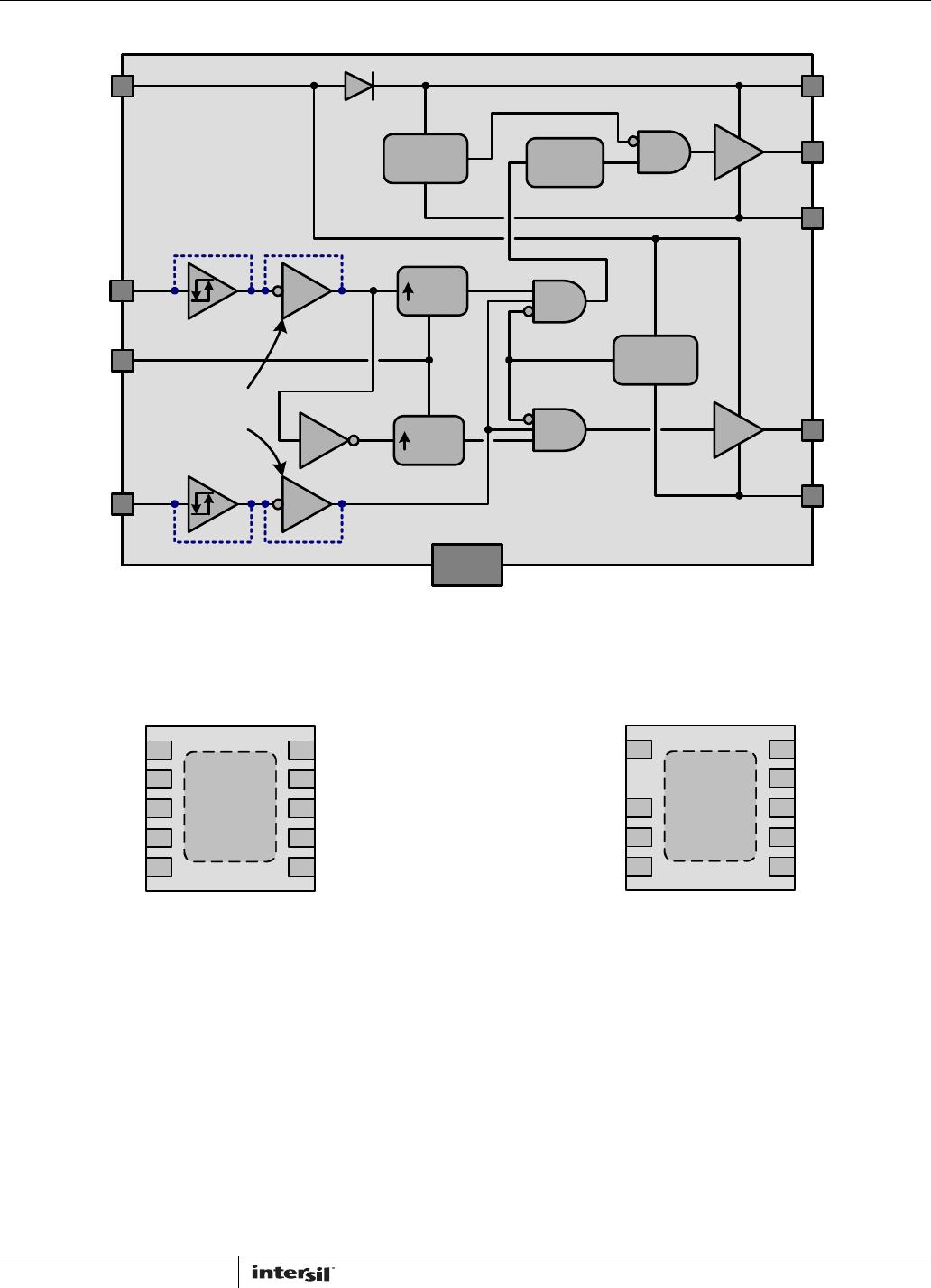

FIGURE 1. TYPICAL APPLICATION FIGURE 2. DEAD-TIME vs TIMING RESISTOR

VDD HB

HO

HS

LOVSS

PWM

EN

100V max

RDT

FEEDBACK

WITH

ISOLATION

PWM

CONTROLLER

SECONDARY

CIRCUITS

HIP2120/21

EPAD

HALF BRIDGE

R

DT

(k)

8162432485640 64 80

DEAD-TIME (ns)

200

160

140

120

100

80

60

40

20

CAUTION: These devices are sensitive to electrostatic discharge; follow proper IC Handling Procedures.

1-888-INTERSIL or 1-888-468-3774

|Copyright Intersil Americas Inc. 2011. All Rights Reserved

Intersil (and design) is a trademark owned by Intersil Corporation or one of its subsidiaries.

All other trademarks mentioned are the property of their respective owners.

December 23, 2011

FN7668.0

N

O

T

R

E

C

O

M

M

E

N

D

E

D

F

O

R

N

E

W

D

E

S

I

G

N

S

N

O

R

E

C

O

M

M

E

N

D

E

D

R

E

P

L

A

C

E

M

E

N

T

c

o

n

t

a

c

t

o

u

r

T

e

c

h

n

i

c

a

l

S

u

p

p

o

r

t

C

e

n

t

e

r

a

t

1

-8

8

8

-

I

N

T

E

R

S

I

L

o

r

w

w

w

.

i

n

te

r

s

i

l

.

c

o

m

/

t

s

c