DS3234

Extremely Accurate SPI Bus RTC with

Integrated Crystal and SRAM

16 ____________________________________________________________________

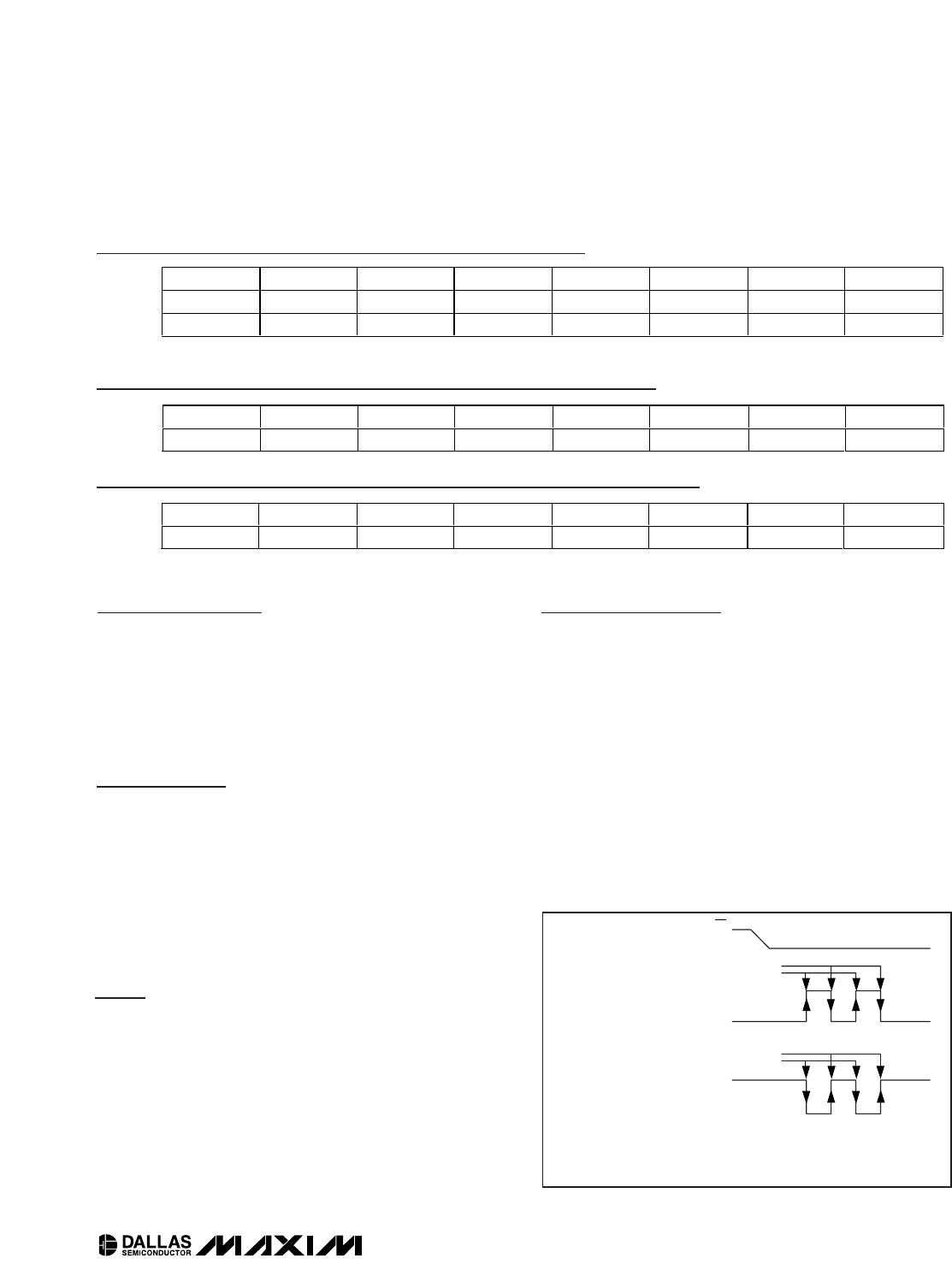

Aging Offset Register (10h/90h)

The aging offset register takes a user-provided value to

add to or subtract from the oscillator capacitor array.

The data is encoded in two’s complement, with bit 7

representing the SIGN bit. One LSB represents the

smallest capacitor to be switched in or out of the

capacitance array at the crystal pins. The aging offset

register capacitance value is added or subtracted from

the capacitance value that the device calculates for

each temperature compensation. The offset register is

added to the capacitance array during a normal tem-

perature conversion, if the temperature changes from

the previous conversion, or during a manual user con-

version (setting the CONV bit). To see the effects of the

aging register on the 32kHz output frequency immedi-

ately, a manual conversion should be performed after

each aging offset register change.

Positive aging values add capacitance to the array,

slowing the oscillator frequency. Negative values

remove capacitance from the array, increasing the

oscillator frequency.

The change in ppm per LSB is different at different tem-

peratures. The frequency vs. temperature curve is shift-

ed by the values used in this register. At +25°C, one

LSB typically provides about 0.1ppm change in fre-

quency. These bits are all set to logic 0 when power is

first applied.

Use of the aging register is not needed to achieve the

accuracy as defined in the EC tables, but could be

used to help compensate for aging at a given tempera-

ture. See the

Typical Operating Characteristics

section

for a graph showing the effect of the register on accu-

racy over temperature.

Temperature Registers (11h–12h)

Temperature is represented as a 10-bit code with a res-

olution of 0.25°C and is accessible at location 11h and

12h. The temperature is encoded in two’s complement

format, with bit 7 in the MSB representing the SIGN bit.

The upper 8 bits, the integer portion, are at location 11h

and the lower 2 bits, the fractional portion, are in the

upper nibble at location 12h. Example: 00011001 01b =

+25.25°C. Upon power reset, the registers are set to a

default temperature of 0°C and the controller starts a

temperature conversion.

The temperature is read on initial application of V

CC

and once every 64 seconds afterwards. The tempera-

ture registers are updated after each user-initiated con-

version and on every 64-second conversion. The

temperature registers are read-only.