IDT

®

Nineteen Output Differential Buffer for PCIe Gen3

9DB1933

Nineteen Output Differential Buffer for PCIe Gen3

13

1676A—07/12/10

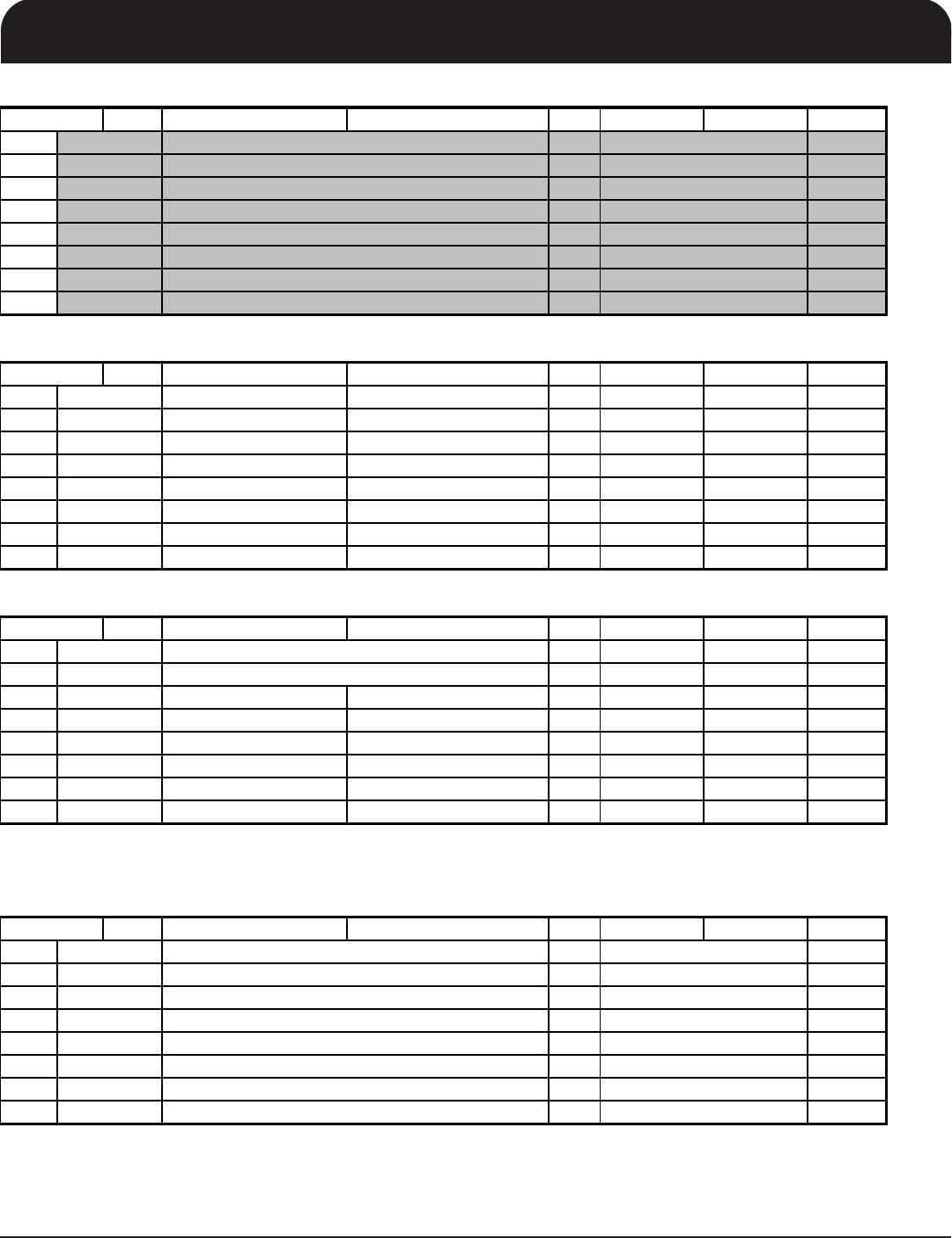

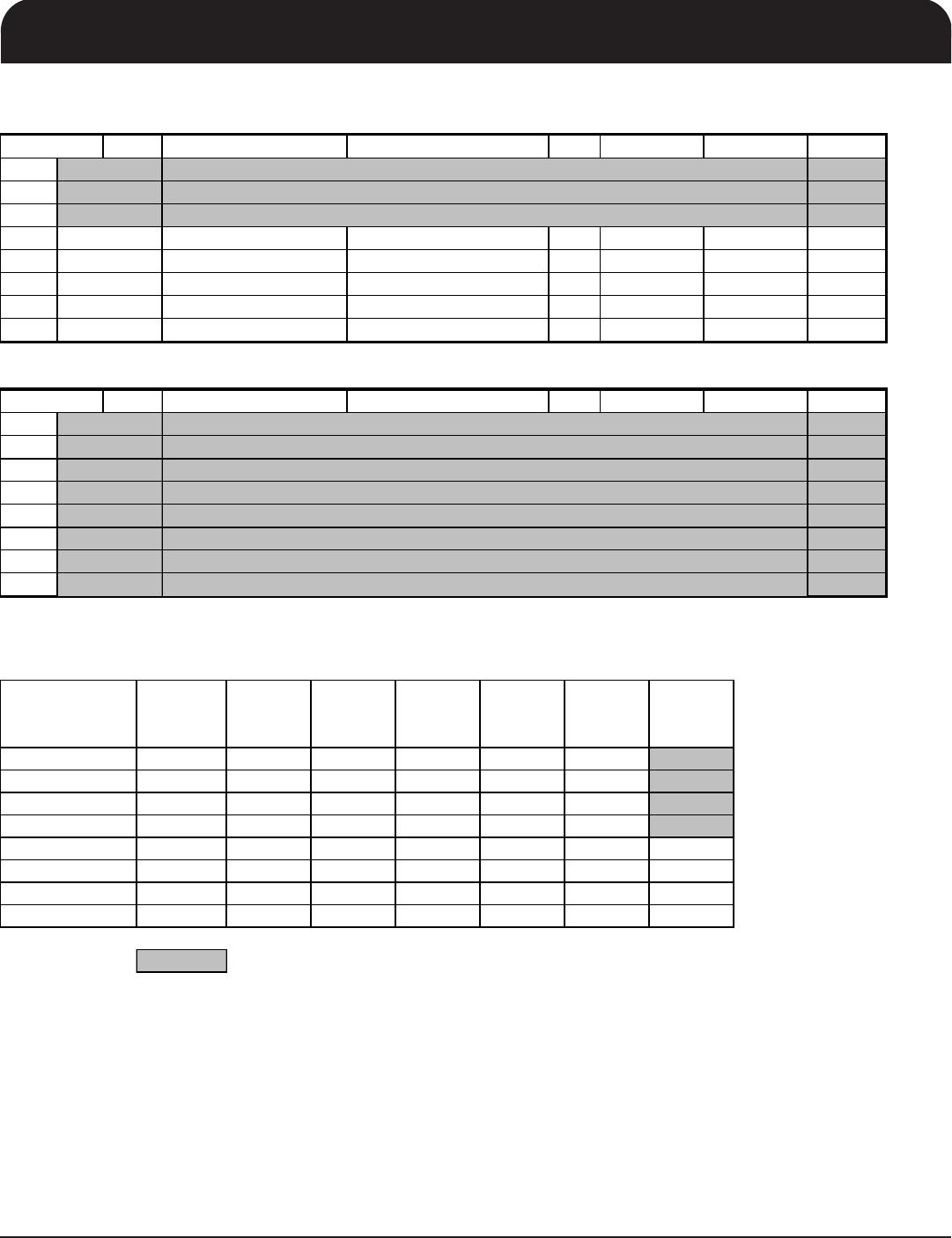

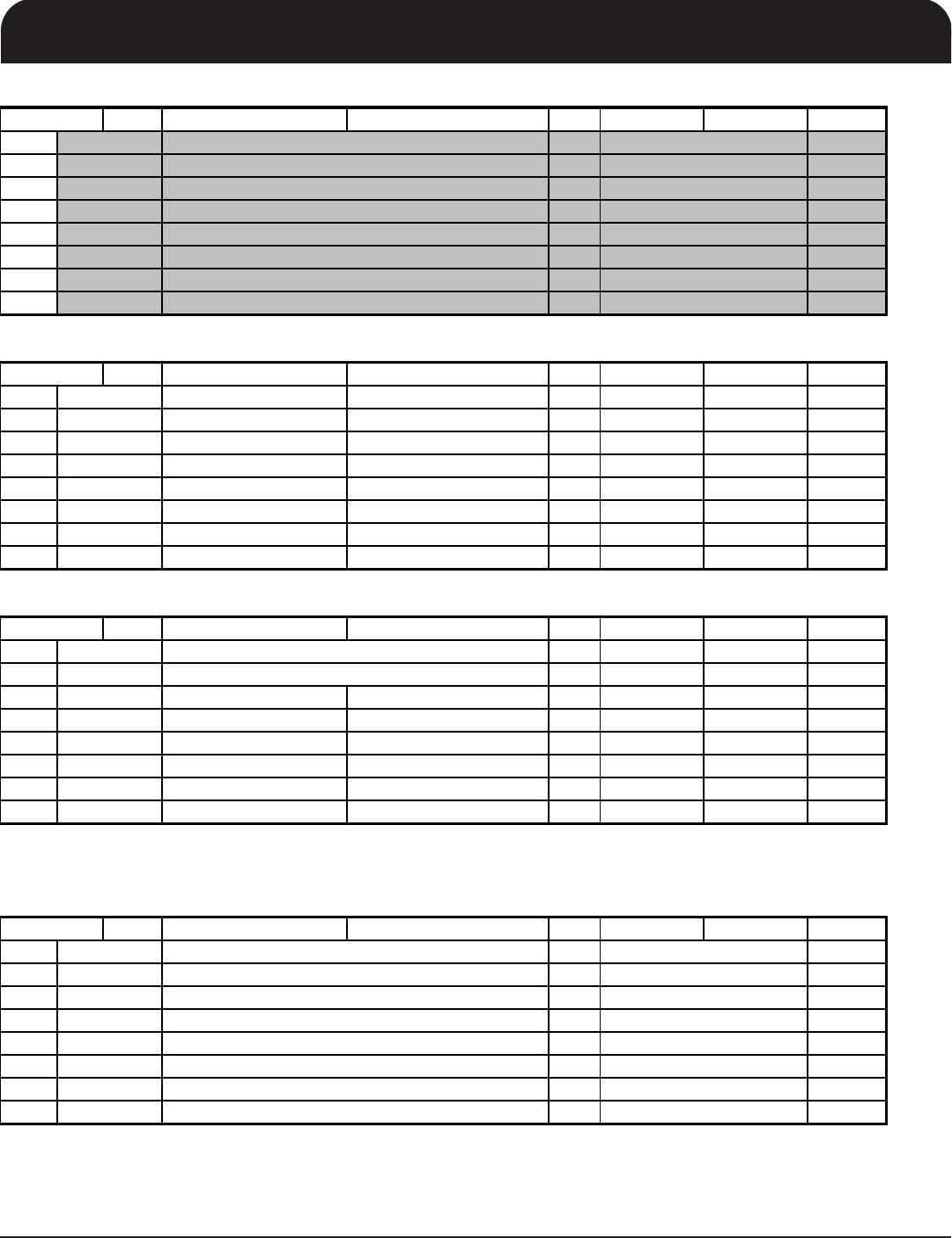

SMBusTable: Reserved Register

1

Bit 0 R

1

SMBusTable: Output Control Register

DIF_7 Output Control RW Hi-Z Enable 1

DIF_5 Output Control RW Hi-Z Enable 1

DIF_4 Output Control RW Hi-Z Enable 1

DIF_2 Output Control RW Hi-Z Enable 1

Bit 0

DIF_0 Output Control RW Hi-Z Enable 1

SMBusTable: Output and PLL BW Control Register

DIF_12 Output Control RW Hi-Z Enable 1

DIF_11 Output Control RW Hi-Z Enable 1

DIF_9 Output Control RW Hi-Z Enable 1

Bit 0

DIF_8 Output Control RW Hi-Z Enable 1

Note: Bit 7 is wired OR to the HIGH_BW# input, any 0 selects High BW

Note: Bit 6 is wired OR to the SMB_A2_PLLBYP# input, any 0 selects Fanout Bypass mode

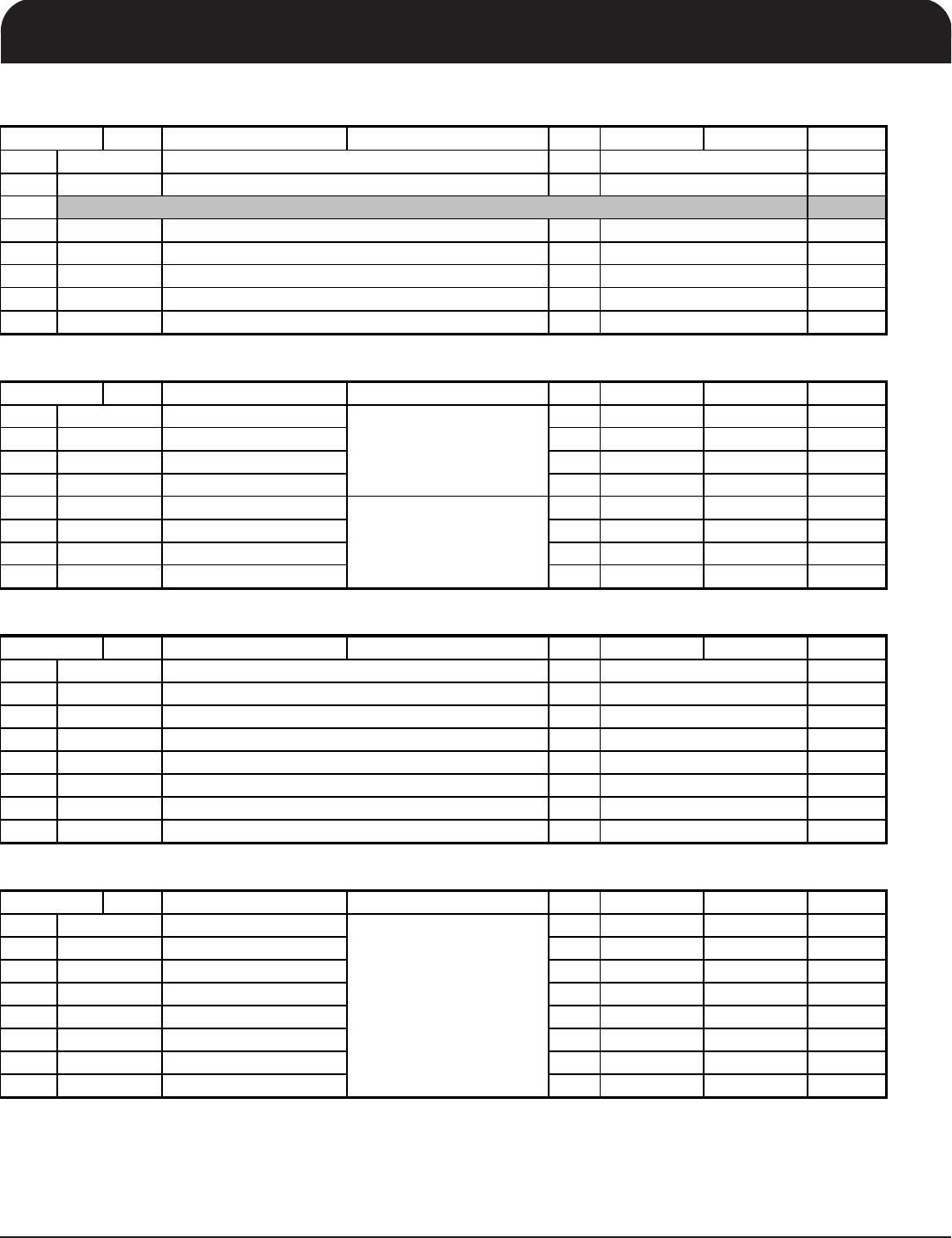

SMBusTable: Output Enable Readback Register

see note PLL_BW# adjust

see note BYPASS# test mode / PLL

Reserved

Readback

Readback - OE9# Input

Readback - OE7# Input

ReadbackReadback - OE_01234# Input

Readback

Readback - OE6# Input

Readback

Readback - SMB_A2_PLLBYP# In

Readback - HIGH_BW# In Readback

Reserved