IDT

®

Nineteen Output Differential Buffer for PCIe Gen3

9DB1933

Nineteen Output Differential Buffer for PCIe Gen3

4

1676A—07/12/10

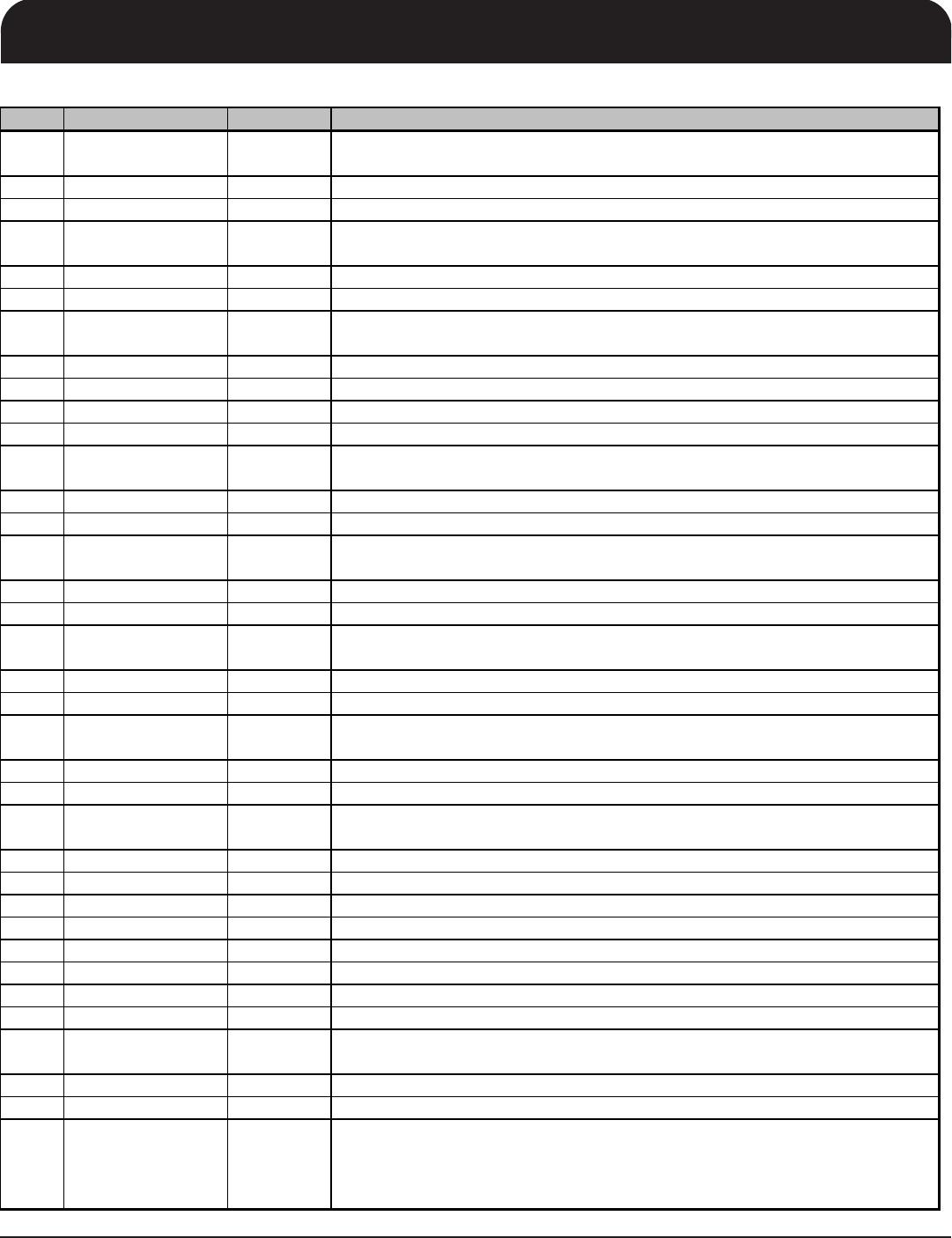

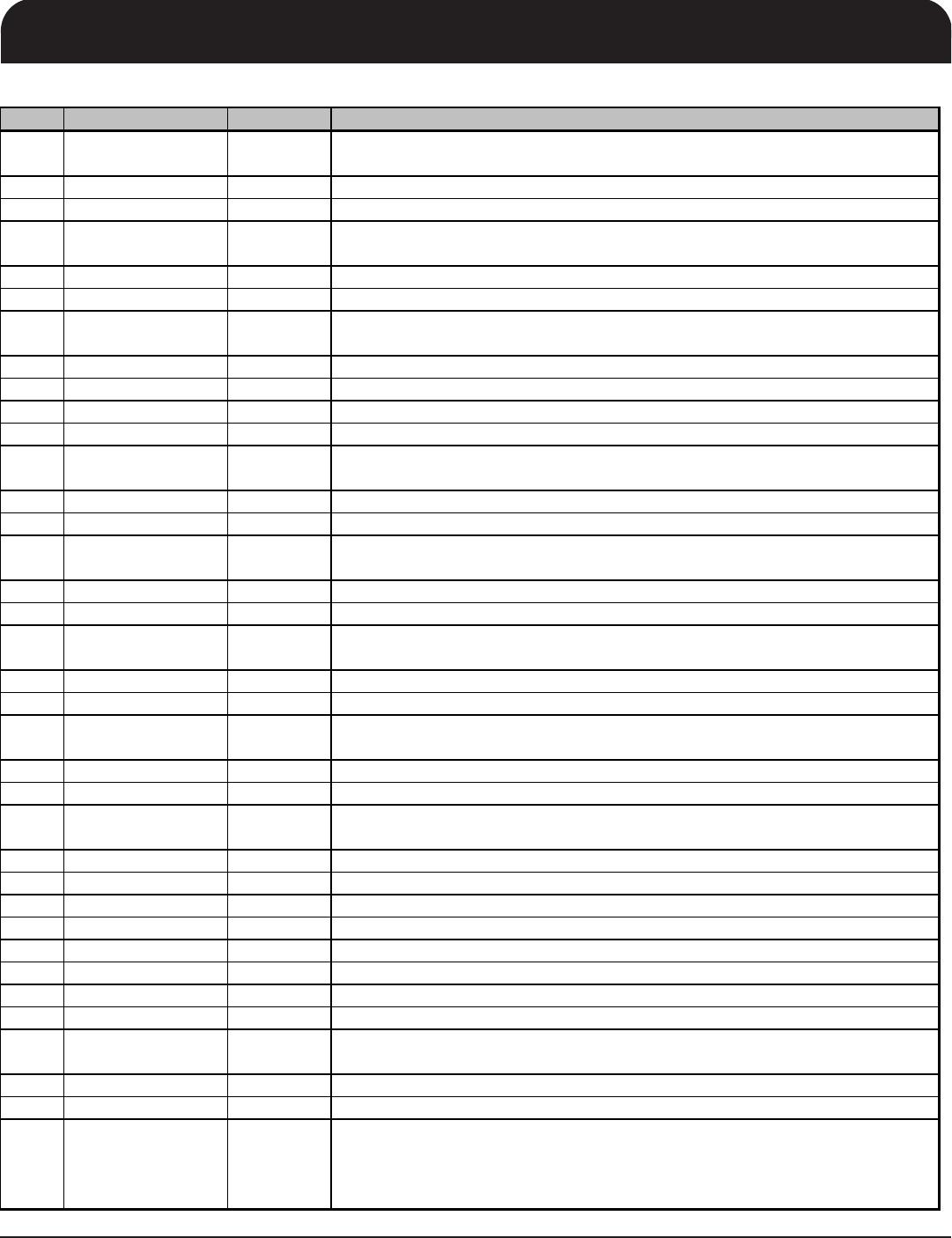

Pin Description (cont.)

PIN # PIN NAME PIN TYPE DESCRIPTION

37 OE9# IN

Active low input for enabling DIF pair 9.

1 =disable outputs, 0 = enable outputs

0.7V differential true clock output

39 DIF_9# OUT 0.7V differential Complementary clock output

40 OE10# IN

Active low input for enabling DIF pair 10.

1 =disable outputs, 0 = enable outputs

0.7V differential true clock output

42 DIF_10# OUT 0.7V differential Complementary clock output

43 OE11# IN

Active low input for enabling DIF pair 11.

1 =disable outputs, 0 = enable outputs

0.7V differential true clock output

45 DIF_11# OUT 0.7V differential Complementary clock output

46 GND PWR Ground pin.

47 VDD PWR Power supply, nominal 3.3V

48 OE12# IN

Active low input for enabling DIF pair 12.

1 =disable outputs, 0 = enable outputs

49 DIF_12 OUT 0.7V differential true clock output

50 DIF_12# OUT 0.7V differential Complementary clock output

51 OE13# IN

Active low input for enabling DIF pair 13.

1 =disable outputs, 0 = enable outputs

52 DIF_13 OUT 0.7V differential true clock output

53 DIF_13# OUT 0.7V differential Complementary clock output

54 OE14# IN

Active low input for enabling DIF pair 14.

1 =disable outputs, 0 = enable outputs

55 DIF_14 OUT 0.7V differential true clock output

56 DIF_14# OUT 0.7V differential Complementary clock output

57 CKPWRGD/PD# IN

A rising edge samples latched inputs and release Power Down Mode, a low

puts the part into power down mode and tristates all outputs.

58 DIF_15 OUT 0.7V differential true clock output

59 DIF_15# OUT 0.7V differential Complementary clock output

60 OE_15_16# IN

Active low input for enabling DIF pair 15 and 16.

1 = tri-state outputs, 0 = enable outputs

61 DIF_ 16 OUT 0.7V differential true clock output

62 DIF_16# OUT 0.7V differential Complementary clock output

Power supply, nominal 3.3V

64 GND PWR Ground pin.

65 DIF_17 OUT 0.7V differential true clock output

66 DIF_17# OUT 0.7V differential Complementary clock output

0.7V differential true clock output

68 DIF_18# OUT 0.7V differential Complementary clock output

69 OE_17_18# IN

Active low input for enabling DIF pair 17, 18.

1 = tri-state outputs, 0 = enable outputs

0.7 V Differential TRUE input

71 DIF_IN# IN 0.7 V Differential Complementary Input

72 SMB_A2_PLLBYP# IN

SMBus address bit 2. When Low, the part operates as a fanout buffer with the

PLL bypassed. When High, the part operates as a zero-delay buffer (ZDB) with

the PLL operating.

0 = fanout mode (PLL bypassed), 1 = ZDB mode (PLL used)