AD7376

Rev. D | Page 13 of 20

PROGRAMMING THE POTENTIOMETER DIVIDER

Voltage Output Operation

The digital potentiometer easily generates a voltage divider at

Wiper W to Terminal B and Wiper W to Terminal A that is

proportional to the input voltage at Terminal A to Terminal B.

Unlike the polarity of V

DD

to GND, which must be positive,

voltage across Terminal A to Terminal B, Wiper W to Terminal A,

and Wiper W to Terminal B can be at either polarity.

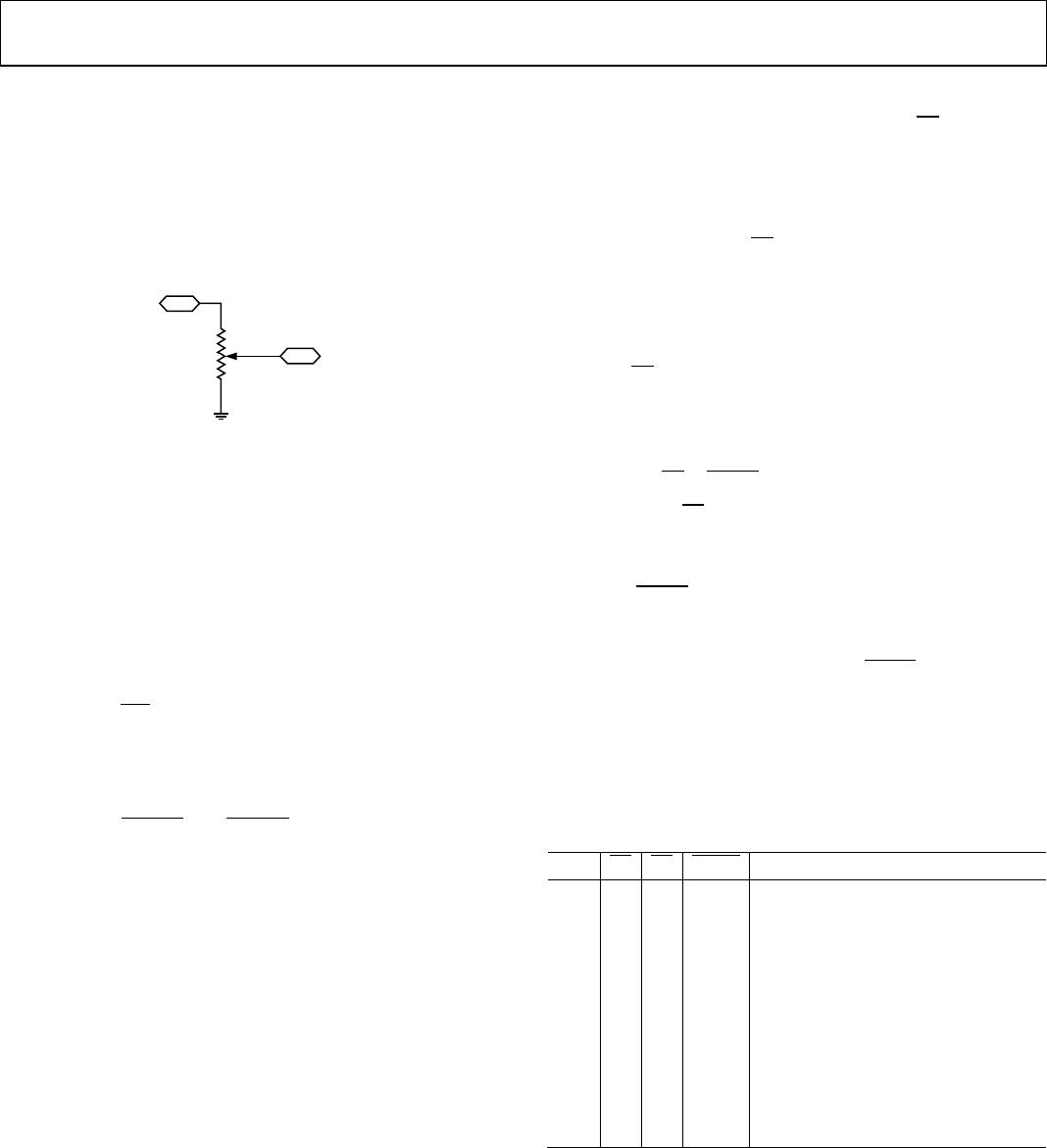

Figure 26. Potentiometer Mode Configuration

If ignoring the effect of the wiper resistance for the purpose of

approximation, connecting the Terminal A to 30 V and the

Terminal B to ground produces an output voltage at the Wiper W

to Terminal B ranging from 0 V to 1 LSB less than 30 V. Each

LSB of voltage is equal to the voltage applied across Terminals A

and B divided by the 128 positions of the potentiometer divider.

The general equation defining the output voltage at V

W

with

respect to ground for any valid input voltage applied to

Terminals A and B is

(3)

A more accurate calculation that includes the effect of wiper

resistance, V

W

, is

B

AB

WA

A

AB

WB

W

V

R

DR

V

R

DR

DV

)(

)(

)( +=

(4)

Operation of the digital potentiometer in the divider mode

results in a more accurate operation over temperature. Unlike

when in rheostat mode, the output voltage in divider mode is

primarily dependent on the ratio, not the absolute values, of the

internal resistors R

WA

and R

WB

. Therefore, the temperature drift

reduces to 5 ppm/°C.

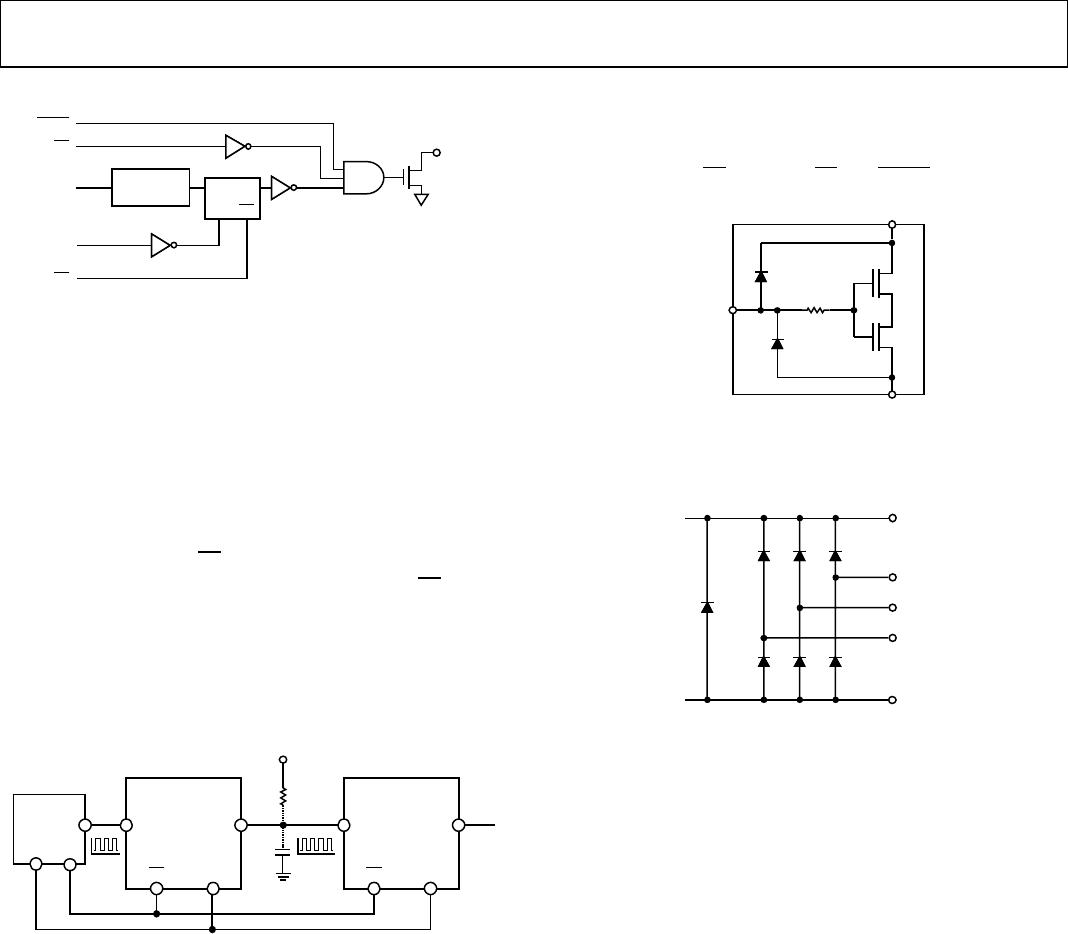

3-WIRE SERIAL BUS DIGITAL INTERFACE

The AD7376 contains a 3-wire digital interface (

CS

, CLK, and

SDI). The 7-bit serial word must be loaded MSB first. The

format of the word is shown in Figure 2. The positive edge-

sensitive CLK input requires clean transitions to avoid clocking

incorrect data into the serial input register. Standard logic

families work well. When

CS

is low, the clock loads data into the

serial register upon each positive clock edge.

The data setup and hold times in Table 3 determine the valid

timing requirements. The AD7376 uses a 7-bit serial input data

register word that is transferred to the internal RDAC register

when the

CS

line returns to logic high. Extra MSB bits are

ignored.

The AD7376 powers up at a random setting. However, the

midscale preset or any desirable preset can be achieved by

manipulating

RS

or

SHDN

with an extra I/O.

When the reset (

RS

) pin is asserted, the wiper resets to the

midscale value. Midscale reset can be achieved dynamically or

during power-up if an extra I/O is used.

When the

SHDN

pin is asserted, the AD7376 opens SW

A

to let

the Terminal A float and to short Wiper W to Terminal B. The

AD7376 consumes negligible power during the shutdown mode

and resumes the previous setting once the

SHDN

pin is released.

On the other hand, the AD7376 can be programmed with any

settings during shutdown. With an extra programmable I/O

asserting shutdown during power-up, this unique feature allows

the AD7376 with programmable preset at any desirable level.

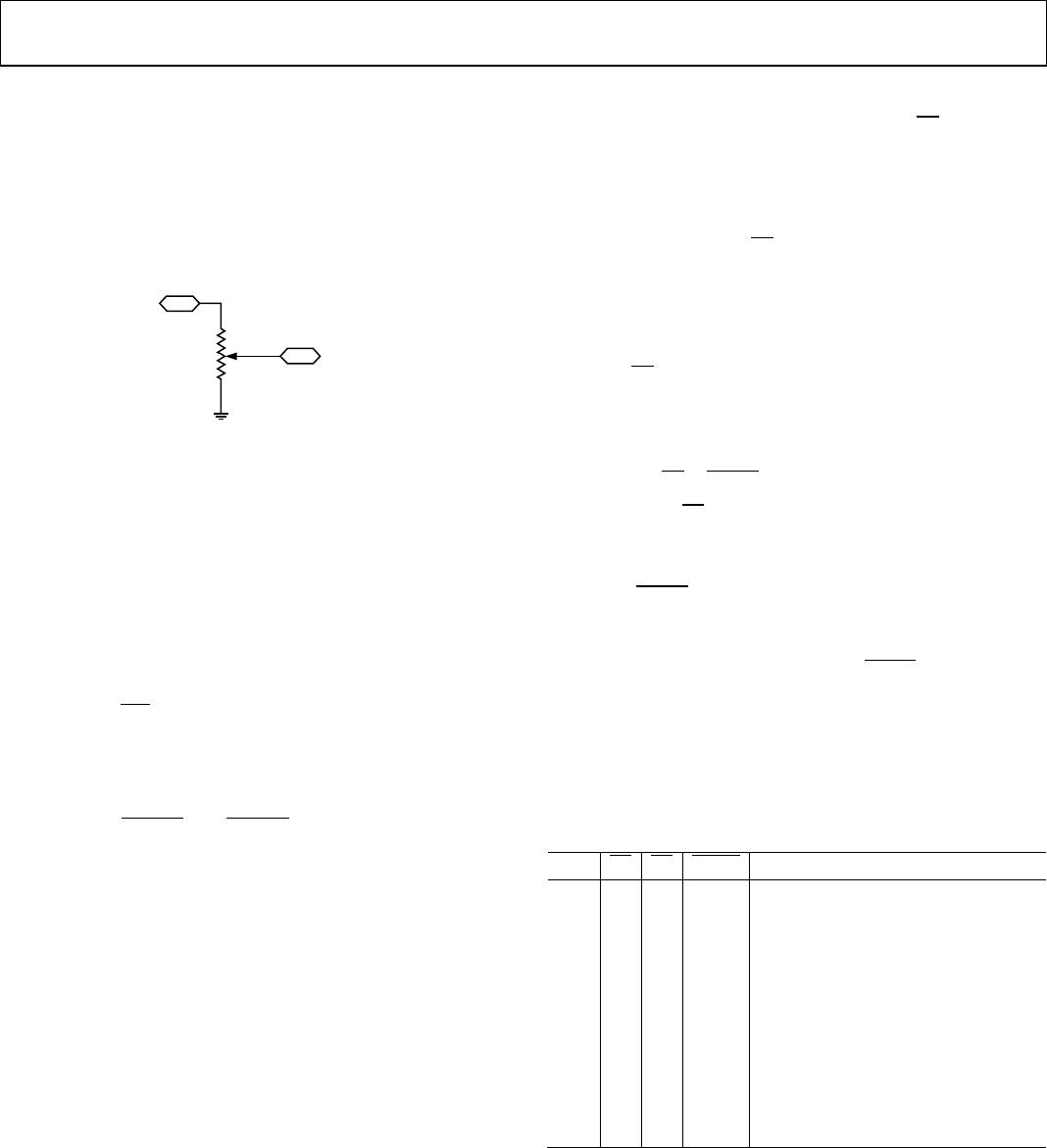

Table 7 shows the logic truth table for all operations.

Table 7. Input Logic Control Truth Table

1

CLK

CS

RS

SHDN

Register Activity

L L H H Enables SR, enables SDO pin.

P L H H Shifts one bit in from the SDI pin. The

seventh previously entered bit is

shifted out of the SDO pin.

X P H H Loads SR data into 7-bit RDAC latch.

X H H H No operation.

Sets 7-bit RDAC latch to midscale,

wiper centered, and SDO latch cleared.

X H P H Latches 7-bit RDAC latch to 0x40.

X H H L Opens circuits resistor of Terminal A,

connects Wiper W to Terminal B,

turns off SDO output transistor.

1

P = positive edge, X = don’t care, and SR = shift register.