AD7376

Rev. D | Page 5 of 20

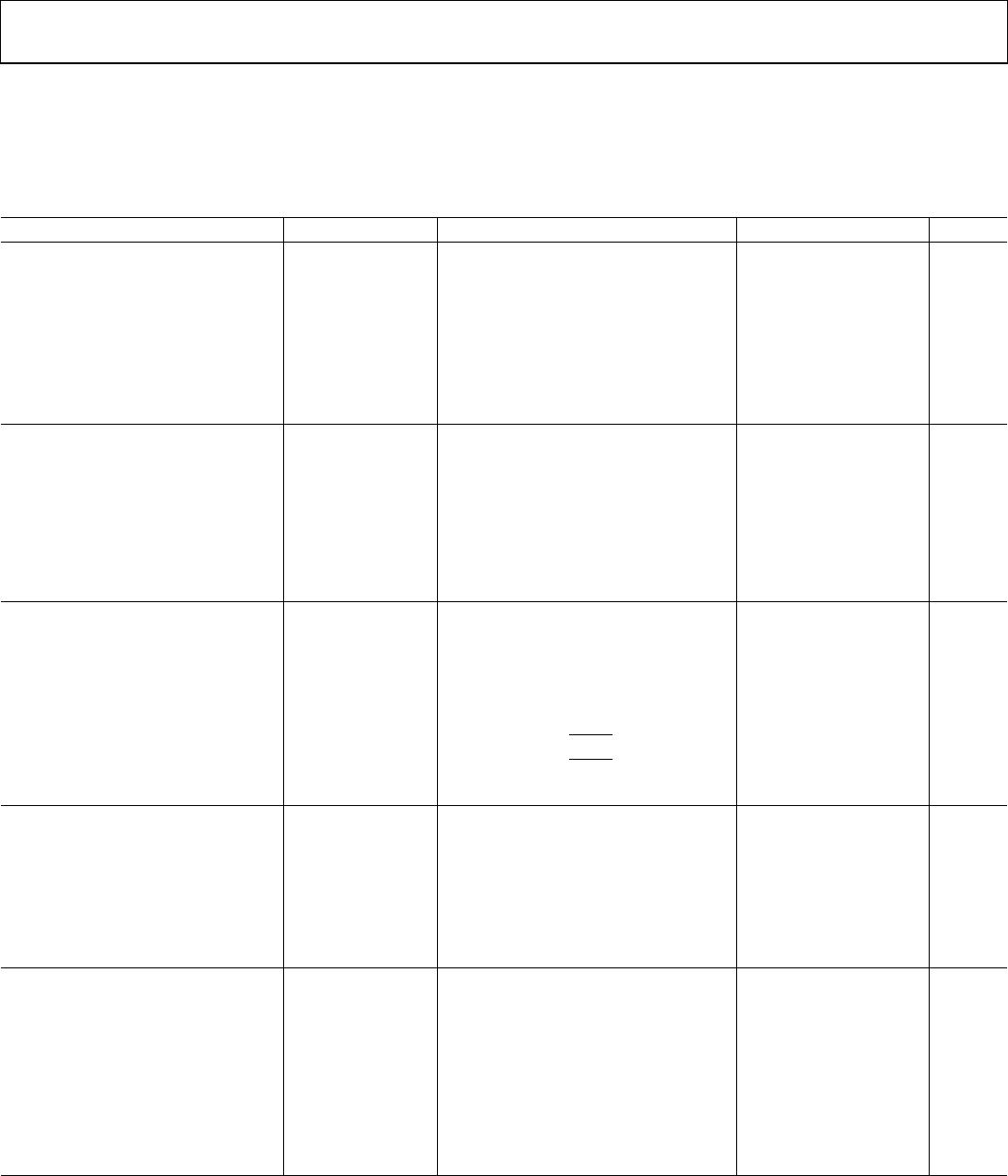

Parameter Symbol Conditions Min Typ

1

Max Unit

DIGITAL INPUTS AND OUTPUTS

Input Logic High V

IH

V

DD

= 5 V or 15 V 2.4 V

Input Logic Low V

IL

V

DD

= 5 V or 15 V 0.8 V

Output Logic High V

OH

R

Pull-Up

= 2.2 kΩ to 5 V 4.9 V

OL

OL

DD

Input Current I

IL

V

IN

= 0 V or 5 V ±1 µA

Input Capacitance

6

C

IL

5 pF

POWER SUPPLIES

Power Supply Range V

DD

/V

SS

Dual-supply range ±4.5 ±16.5 V

Power Supply Range V

DD

Single-supply range, V

SS

= 0 4.5 33 V

Positive Supply Current I

DD

V

IH

= 5 V or V

IL

= 0 V, V

DD

/V

SS

= ±15 V 2 mA

V

IH

= 5 V or V

IL

= 0 V, V

DD

/V

SS

= ±5 V 12 25 µA

Negative Supply Current I

SS

V

IH

= 5 V or V

IL

= 0 V, V

DD

/V

SS

= ±15 V −0.1 mA

IH

IL

DD

SS

Power Dissipation

8

P

DISS

V

IH

= 5 V or V

IL

= 0 V, V

DD

/V

SS

= ±15 V 31.5 mW

Power Supply Rejection Ratio PSRR −0.25 ±0.1 +0.25 %/%

DYNAMIC CHARACTERISTICS

6, 9, 10

Bandwidth −3 dB BW R

AB

= 50 kΩ, code = 0x40 90 kHz

R

AB

= 100 kΩ, code = 0x40 50 kHz

Total Harmonic Distortion THD

W

V

A

= 1 V rms, V

B

= 0 V, f = 1 kHz 0.002 %

V

W

Settling Time t

S

V

A

= 10 V, V

B

= 0 V, ±1 LSB error band 4 µs

Resistor Noise Voltage e

N_WB

R

WB

= 25 kΩ, f = 1 kHz 2 nV√Hz

1

Typical values represent average readings at 25°C, V

DD

= 15 V, and V

SS

= −15 V.

2

Resistor position nonlinearity error R-INL is the deviation from an ideal value measured between the maximum and minimum resistance wiper positions. R-DNL

measures the relative step change from an ideal value measured between successive tap positions. Parts are guaranteed monotonic.

3

Pb-free parts have a 35 ppm/°C temperature coefficient.

4

INL and DNL are measured at V

W

with the RDAC configured as a potentiometer divider, similar to a voltage output digital-to-analog converter. V

A

= V

DD

and V

B

= 0 V.

DNL specification limits of ±1 LSB maximum are guaranteed monotonic operating conditions.

5

Resistor Terminals A, B, and W have no limitations on polarity with respect to each other.

6

Guaranteed by design and not subject to production test.

7

Measured at the A terminal. A terminal is open circuit in shutdown mode.

8

P

DISS

is calculated from (I

DD

× V

DD

) + abs(I

SS

× V

SS

). CMOS logic level inputs result in minimum power dissipation.

9

Bandwidth, noise, and settling times are dependent on the terminal resistance value chosen. The lowest R value results in the fastest settling time and highest

bandwidth. The highest R value results in the minimum overall power consumption.

10

All dynamic characteristics use V

DD

= 15 V and V

SS

= −15 V.

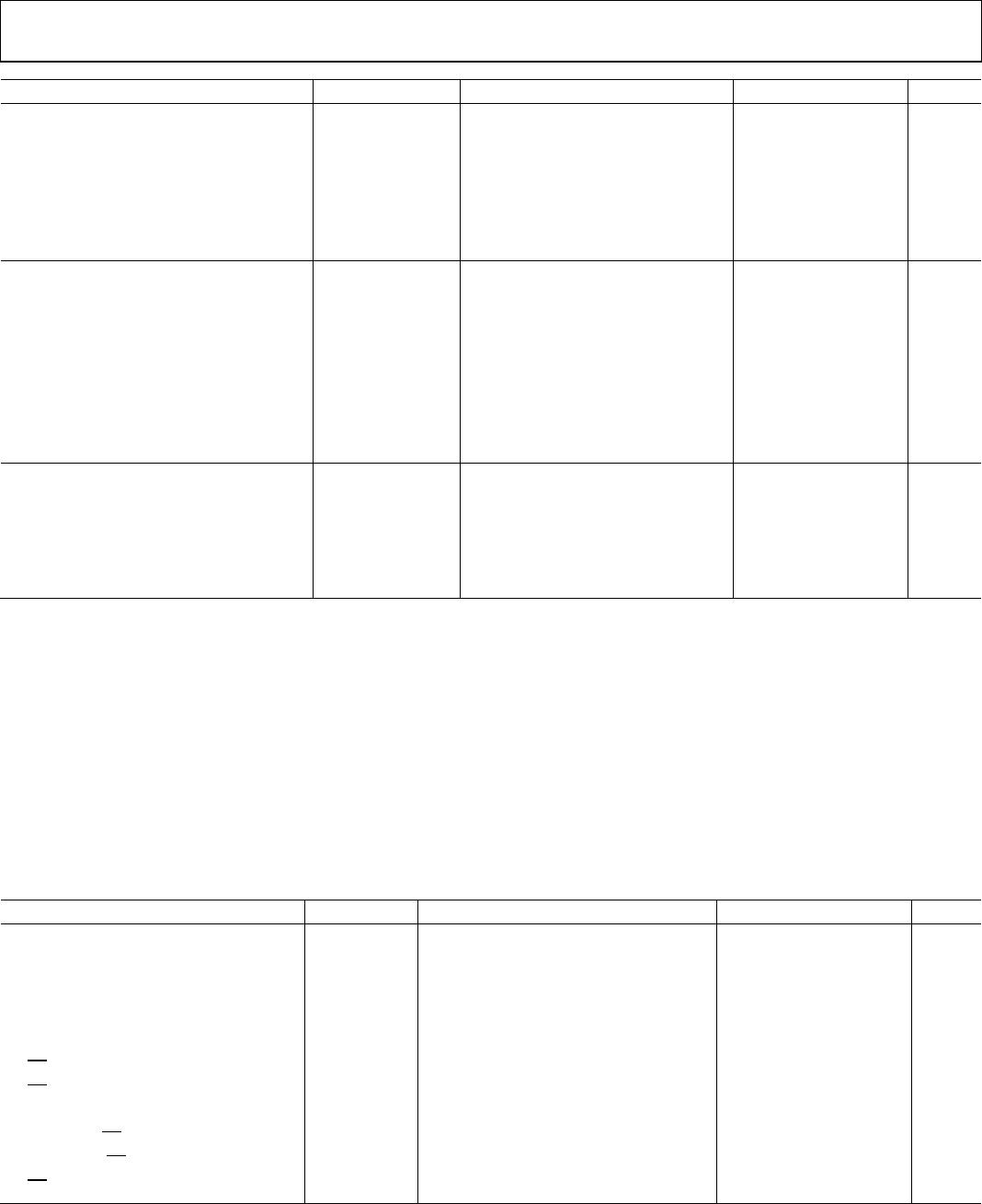

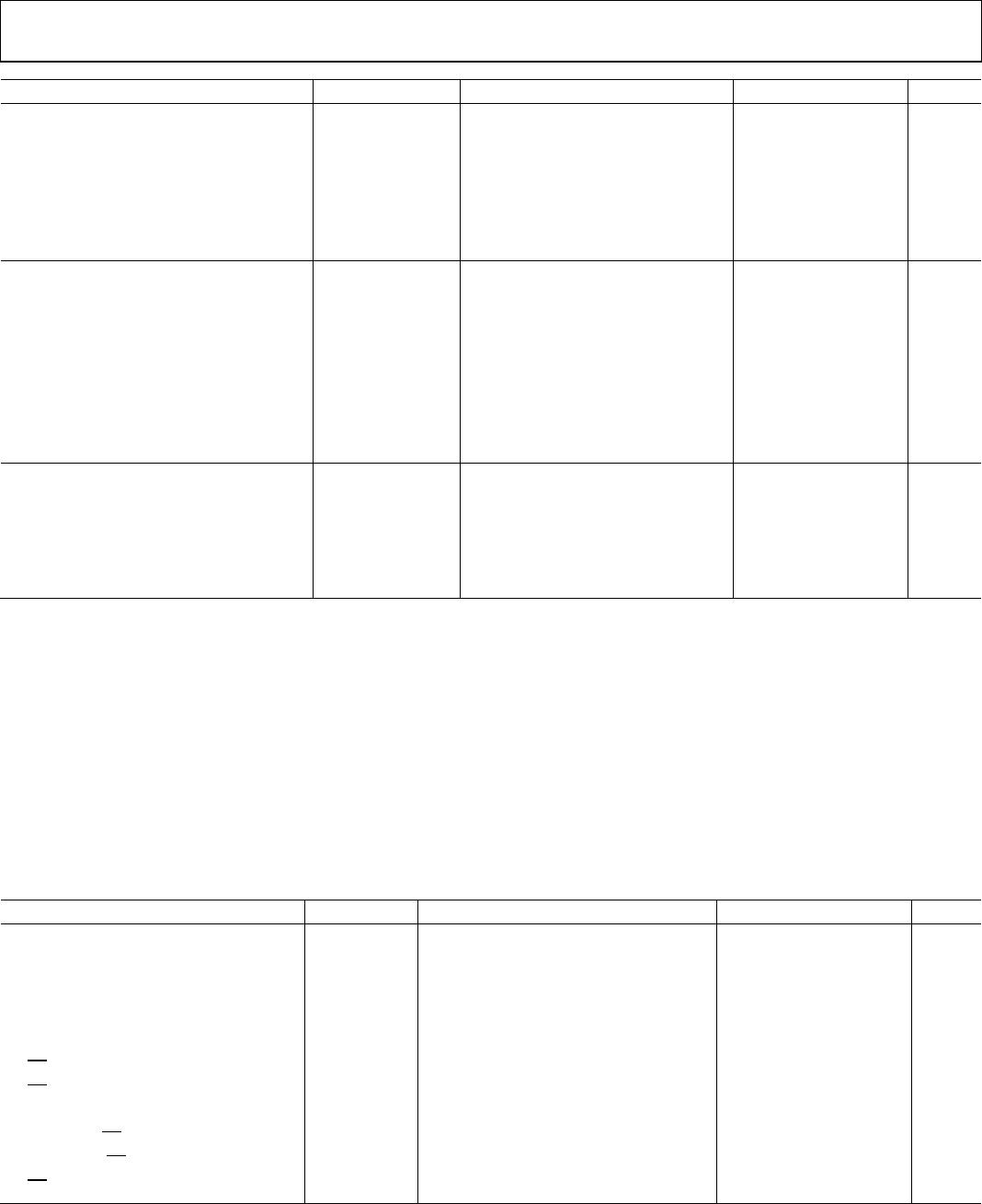

TIMING SPECIFICATIONS

Table 3.

Parameter Symbol Conditions Min Typ Max Unit

INTERFACE TIMING CHARACTERISTICS

1, 2

Clock Frequency f

CLK

4 MHz

Input Clock Pulse Width t

CH

, t

CL

Clock level high or low 120 ns

DS

Data Hold Time t

DH

20 ns

CLK to SDO Propagation Delay

3

t

PD

R

Pull-Up

= 2.2 kΩ, C

L

< 20 pF 10

100 ns

CS

Setup Time t

CSS

120 ns

CS

High Pulse Width t

CSW

150 ns

Reset Pulse Width t

RS

120 ns

CLK Fall to

CS

Fall Hold Time t

CSH0

10 ns

CLK Rise to

CS

Rise Hold Time t

CSH

120 ns

CS

Rise to Clock Rise Setup t

CS1

120 ns

1

Guaranteed by design and not subject to production test.

2

See Figure 3 for the location of the measured values. All input control voltages are specified with t

R

= t

F

= 1 ns (10% to 90% of V

DD

) and timed from a voltage level of 1.6 V.

Switching characteristics are measured using V

DD

= 15 V and V

SS

= −15 V.

3

Propagation delay depends on value of V

DD

, R

Pull-Up

, and C

L

.