1

COMMERCIAL AND INDUSTRIAL TEMPERATURE RANGES

3.3 VOLT DUAL CMOS SyncFIFO™

DUAL 256 X 9, DUAL 512 X 9,

DUAL 1,024 X 9, DUAL 2,048 X 9,

DUAL 4,096 X 9 , DUAL 8,192 X 9

IDT72V801

IDT72V811

IDT72V821

IDT72V831

IDT72V841

IDT72V851

NOVEMBER 2014

IDT and the IDT logo are registered trademarks of Integrated Device Technology, Inc. The TeraSync FIFO is a trademark of Integrated Device Technology, Inc.

©2014 Integrated Device Technology, Inc. All rights reserved. Product specifications subject to change without notice. DSC-4093/5

FEATURES:

••

••

• The IDT72V801 is equivalent to two IDT72V201 256 x 9 FIFOs

••

••

• The IDT72V811 is equivalent to two IDT72V211 512 x 9 FIFOs

••

••

• The IDT72V821 is equivalent to two IDT72V221 1,024 x 9 FIFOs

••

••

• The IDT72V831 is equivalent to two IDT72V231 2,048 x 9 FIFOs

••

••

• The IDT72V841 is equivalent to two IDT72V241 4,096 x 9 FIFOs

••

••

• The IDT72V851 is equivalent to two IDT72V251 8,192 x 9 FIFOs

••

••

• Offers optimal combination of large capacity, high speed,

design flexibility and small footprint

••

••

• Ideal for prioritization, bidirectional, and width expansion

applications

••

••

• 10 ns read/write cycle time

••

••

• 5V input tolerant

••

••

• Separate control lines and data lines for each FIFO

••

••

• Separate Empty, Full, programmable Almost-Empty and

Almost-Full flags for each FIFO

••

••

• Enable puts output data lines in high-impedance state

••

••

• Space-saving 64-pin plastic Thin Quad Flat Pack (TQFP/

STQFP)

••

••

• Industrial temperature range (–40

°°

°°

°C to +85

°°

°°

°C) is available

••

••

• Green parts available, see ordering information

DESCRIPTION:

The IDT72V801/72V811/72V821/72V831/72V841/72V851/72V851 are

dual synchronous (clocked) FIFOs. The device is functionally equivalent to

two IDT72V201/72V211/72V221/72V231/72V241/72V251 FIFOs in a single

package with all associated control, data, and flag lines assigned to separate

pins.

Each of the two FIFOs (designated FIFO A and FIFO B) contained in the

IDT72V801/72V811/72V821/72V831/72V841/72V851 has a 9-bit input data

port (DA0 - DA8, DB0 - DB8) and a 9-bit output data port (QA0 - QA8,

QB0 - QB8). Each input port is controlled by a free-running clock (WCLKA,

WCLKB), and two Write Enable pins (WENA1, WENA2, WENB1, WENB2).

Data is written into each of the two arrays on every rising clock edge of the Write

Clock (WCLKA, WCLKB) when the appropriate Write Enable pins are

asserted.

The output port of each FIFO bank is controlled by its associated clock pin

(RCLKA, RCLKB) and two Read Enable pins (RENA1, RENA2, RENB1,

RENB2). The Read Clock can be tied to the Write Clock for single clock operation

or the two clocks can run asynchronous of one another for dual clock operation.

An Output Enable pin (OEA, OEB) is provided on the read port of each FIFO

for three-state output control.

Each of the two FIFOs has two fixed flags, Empty (EFA, EFB) and Full (FFA,

FFB). Two programmable flags, Almost-Empty (PAEA, PAEB) and Almost-Full

(PAFA, PAFB), are provided for each FIFO bank to improve memory utilization.

If not programmed, the programmable flags default to Empty+7 for PAEA and

PAEB, and Full-7 for PAFA and PAFB.

The IDT72V801/72V811/72V821/72V831/72V841/72V851 architecture

lends itself to many flexible configurations such as:

• 2-level priority data buffering

• Bidirectional operation

• Width expansion

• Depth expansion

This FIFO is fabricated using IDT's high-performance submicron CMOS

technology.

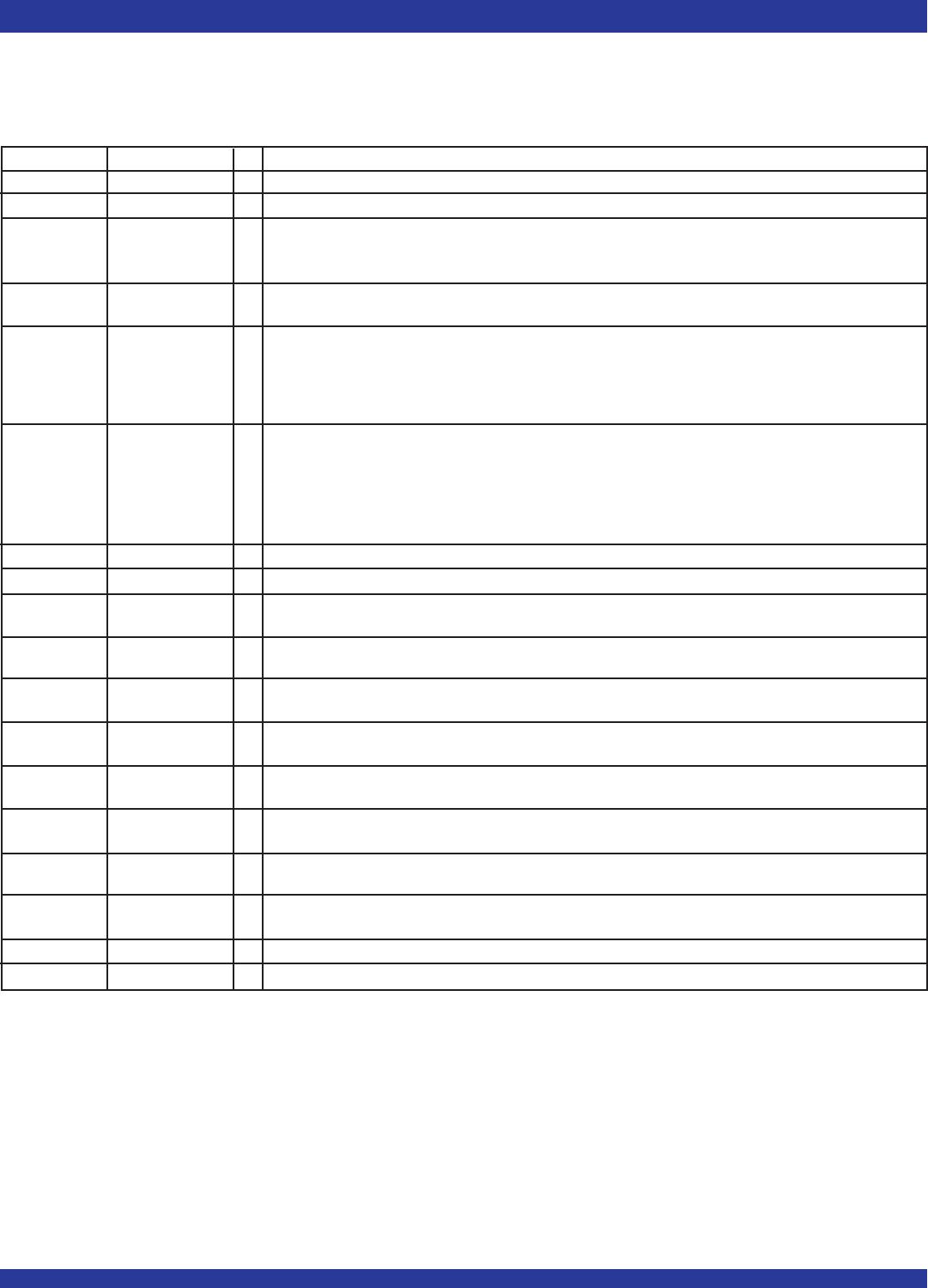

FUNCTIONAL BLOCK DIAGRAM

WCLKA

WENA1

WENA2

DA

0

- DA

8

LDA

OFFSET REGISTERINPUT REGISTER

WRITE CONTROL

LOGIC

RESET LOGIC

OUTPUT REGISTER

OEA

RSA

QA

0

- QA

8

RCLKA

RENA1

RENA2

READ CONTROL

LOGIC

READ POINTER

FLAG

LOGIC

EFA

PAEA

PAFA

FFA

4093 drw 01

WCLKB

WENB1

WENB2

DB

0

- DB

8

LDB

OFFSET REGISTERINPUT REGISTER

RAM ARRAY

256 x 9, 512 x 9,

1,024 x 9, 2,048 x 9,

4,096 x 9, 8,192 x 9

WRITE CONTROL

LOGIC

WRITE POINTER

RESET LOGIC

OUTPUT REGISTER

OEB

RSB

QB

0

- QB

8

RCLKB

RENB1

RENB2

READ CONTROL

LOGIC

READ POINTER

FLAG

LOGIC

EFB

PAFB

FFB

PAEB

WRITE POINTER

RAM ARRAY

256 x 9, 512 x 9,

1,024 x 9, 2,048 x 9,

4,096 x 9, 8,192 x 9