Data Sheet AD5512A/AD5542A

Rev. C | Page 17 of 21

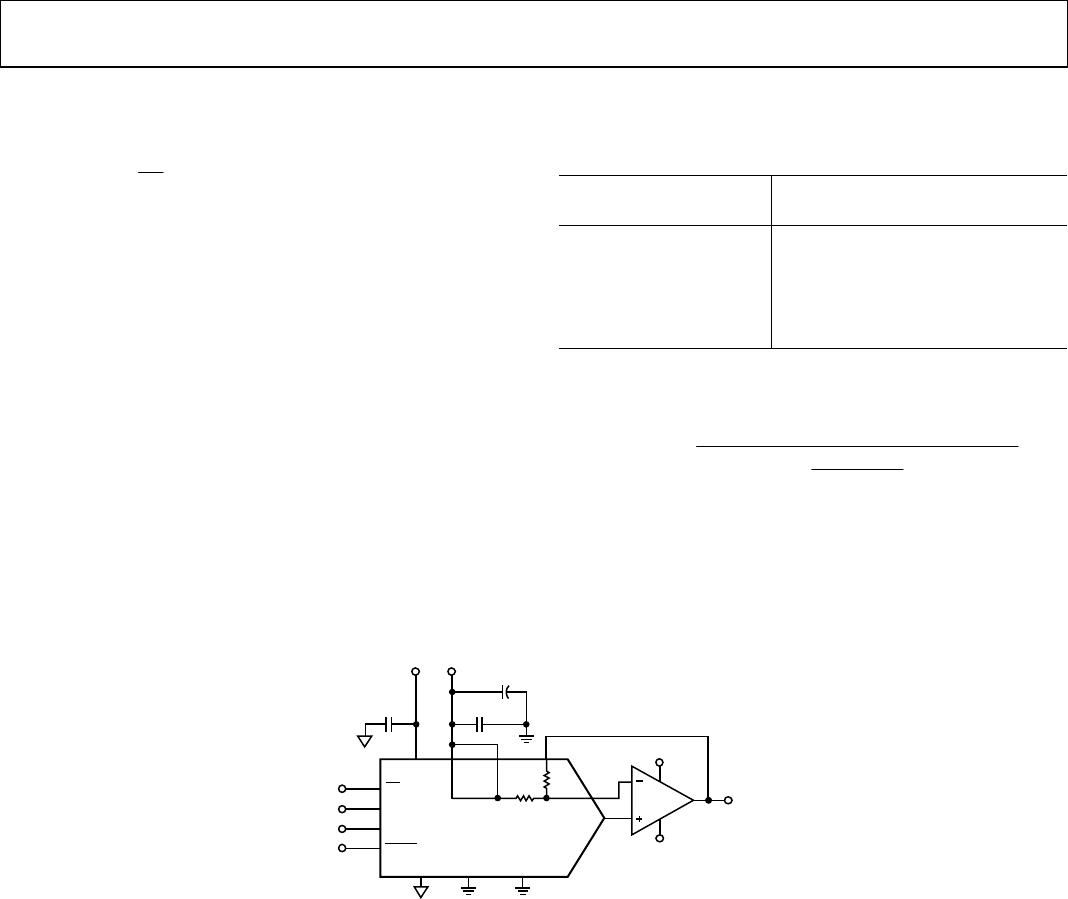

OUTPUT AMPLIFIER SELECTION

For bipolar mode, a precision amplifier should be used and

supplied from a dual power supply. This provides the ±V

REF

output. In a single-supply application, selection of a suitable op

amp may be more difficult because the output swing of the ampli-

fier does not usually include the negative rail, in this case,

AGND. This can result in some degradation of the specified

performance unless the application does not use codes near zero.

The selected op amp must have a very low-offset voltage (the

DAC LSB is 38 μV for the AD5542A with a 2.5 V reference)

to eliminate the need for output offset trims. Input bias current

should also be very low because the bias current, multiplied by

the DAC output impedance (approximately 6 kΩ), adds to the

zero-code error. Rail-to-rail input and output performance is

required. For fast settling, the slew rate of the op amp should

not impede the settling time of the DAC. Output impedance

of the DAC is constant and code-independent, but to minimize

gain errors, the input impedance of the output amplifier should

be as high as possible. The amplifier should also have a 3 dB

bandwidth of 1 MHz or greater. The amplifier adds another

time constant to the system, thus increasing the settling time

of the output. A higher 3 dB amplifier bandwidth results in a

shorter effective settling time of the combined DAC and amplifier.

FORCE SENSE AMPLIFIER SELECTION

Use single-supply, low-noise amplifiers. A low-output impedance

at high frequencies is preferred because the amplifiers must be

able to handle dynamic currents of up to ±20 mA.

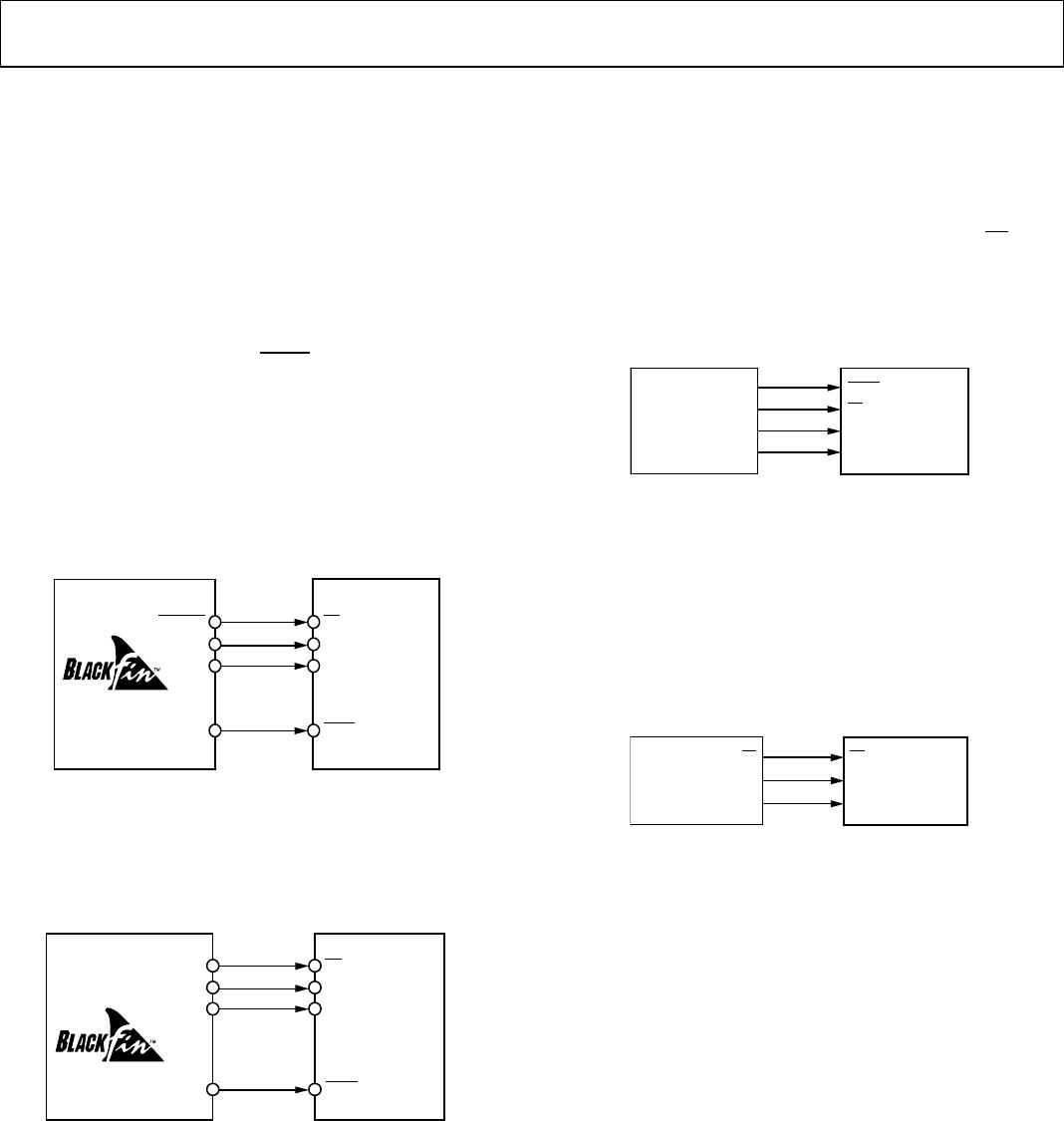

REFERENCE AND GROUND

Because the input impedance is code-dependent, the refer-

ence pin should be driven from a low impedance source. The

AD5512A/AD5542A operate with a voltage reference ranging

from 2 V to V

DD

. References below 2 V result in reduced accuracy.

The full-scale output voltage of the DAC is determined by the

reference. Table 9 and Table 10 outline the analog output voltage

or particular digital codes. For optimum performance, Kelvin

sense connections are provided on the AD5512A/AD5542A.

If the application doesn’t require separate force and sense lines,

tie the lines close to the package to minimize voltage drops

between the package leads and the internal die.

POWER-ON RESET

The AD5512A/AD5542A have a power-on reset function to

ensure that the output is at a known state on power-up. On

power-up, the DAC register MSB is 1 and all other bits are 0

until the data is loaded from the serial register. However, the

serial register is not cleared on power-up; therefore, its contents

are undefined. When loading data initially to the DAC, 16 bits or

more should be loaded to prevent erroneous data appearing on

the output. If more than 16 bits are loaded, the last 16 are kept,

and if less than 16 bits are loaded, bits remain from the previous

word. If the AD5512A/AD5542A must be interfaced with data

shorter than 16 bits, the data should be padded with 0s at the

LSBs.

POWER SUPPLY AND REFERENCE BYPASSING

For accurate high-resolution performance, it is recommended

that the reference and supply pins be bypassed with a 10 μF

tantalum capacitor in parallel with a 0.1 μF ceramic capacitor.