AD5512A/AD5542A Data Sheet

Rev. C | Page 4 of 21

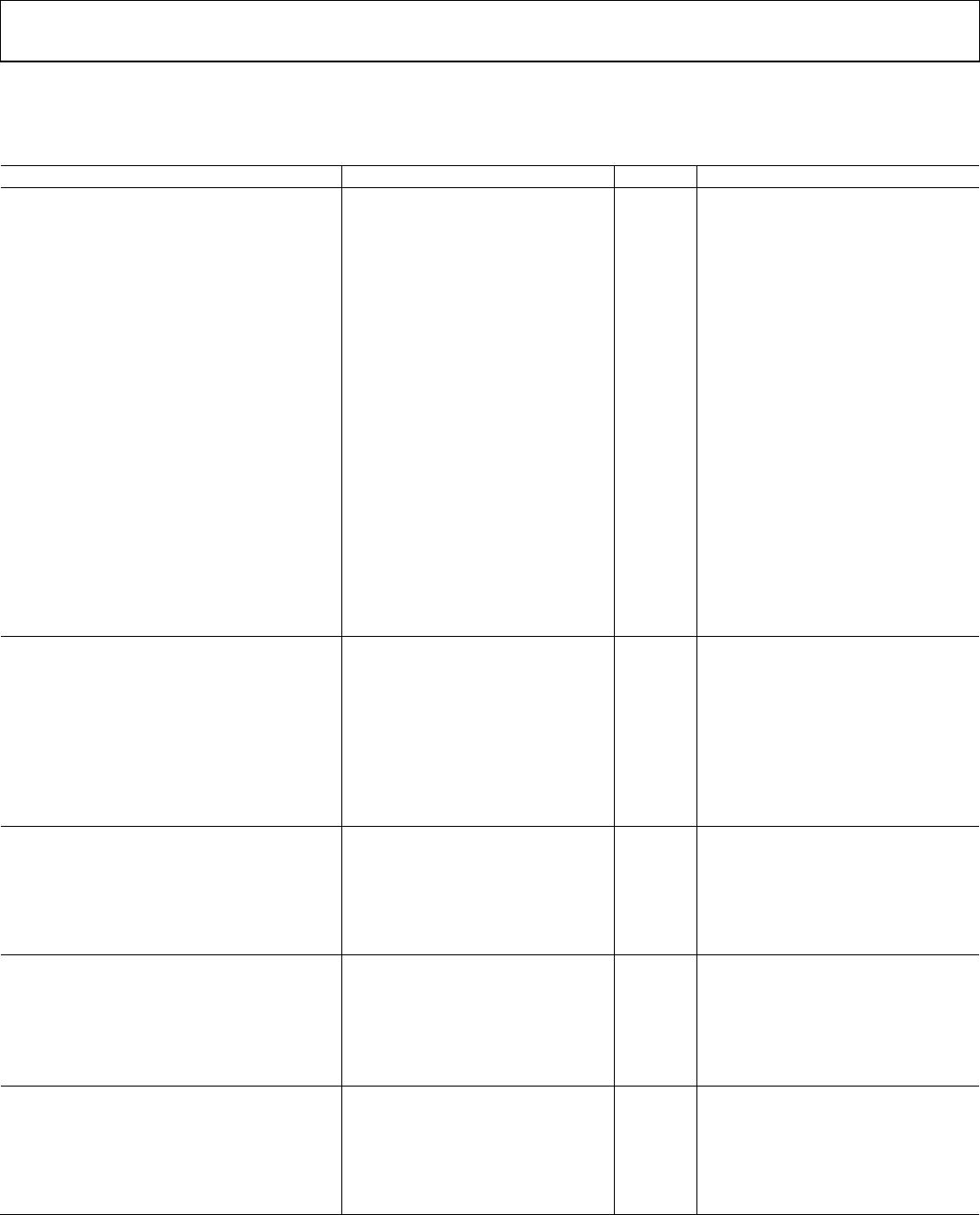

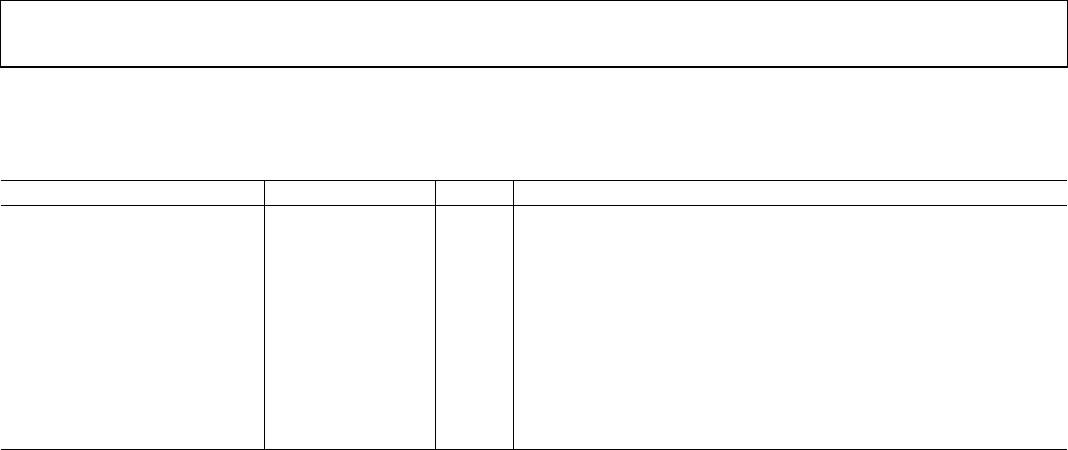

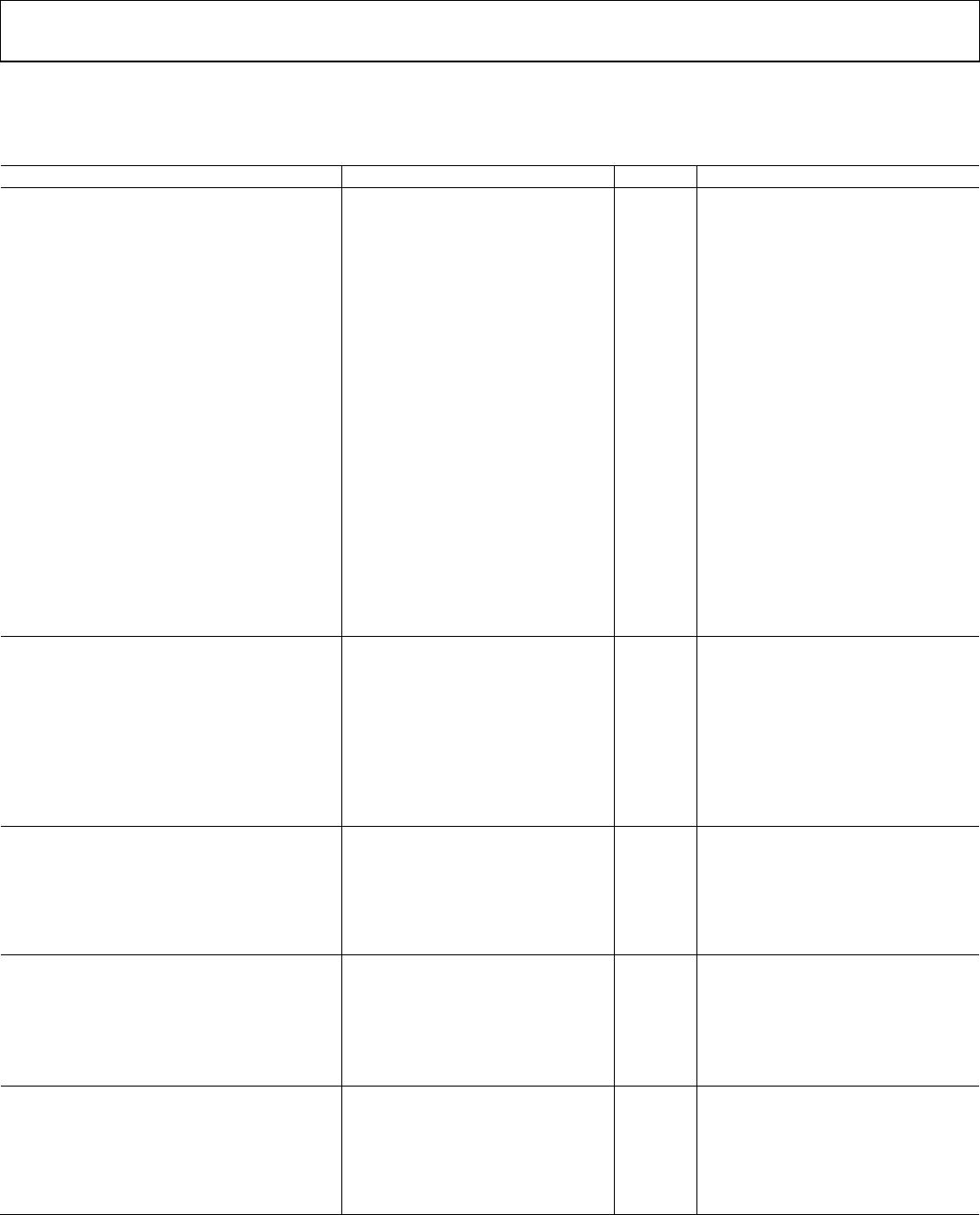

AD5542A

V

DD

= 2.7 V to 5.5 V, V

LOGIC

= 2.7 V to 5.5 V, V

REF

= 2.5 V, AGND = DGND = 0 V, −40°C < T

A

< +85°C, unless otherwise noted.

Table 3.

Parameter

1

Min Typ Max Unit Test Condition

STATIC PERFORMANCE

Resolution 16 Bits

Relative Accuracy (INL) ±0.5 ±1.0 LSB B grade

±2.0 A grade

Differential Nonlinearity (DNL)

Gain Error +0.5 ±2 LSB T

A

= 25°C

±3 LSB

Gain Error Temperature Coefficient ±0.1 ppm/°C

Unipolar Zero-Code Error 0.3 ±0.7 LSB T

A

= 25°C

±1.5 LSB

Unipolar Zero-Code Temperature Coefficient ±0.05 ppm/°C

Bipolar Resistor Matching 1.000 Ω/Ω R

FB

/R

INV

, typically R

FB

= R

INV

= 28 kΩ

±0.0015 ±0.0076 % Ratio error

Bipolar Zero Offset Error ±1 ±5 LSB T

A

= 25°C

±6 LSB

Bipolar Zero Temperature Coefficient ±0.2 ppm/°C

Bipolar Zero-Code Offset Error

A

±6 LSB

Bipolar Gain Error ±1 ±5 LSB T

A

= 25°C

±6 LSB

Bipolar Gain Temperature Coefficient ±0.1 ppm/°C

OUTPUT CHARACTERISTICS

Output Voltage Range 0 V

REF

− 1 LSB V Unipolar operation

−V

REF

+V

REF

− 1 LSB V Bipolar operation

DAC Output Impedance 6.25 kΩ Tolerance typically 20%

Power Supply Rejection Ratio

DD

Output Noise Spectral Density

DAC code = 0x840 (AD5512A) or

0x8400 (AD5542A), frequency = 1 kHz,

unipolar mode

Output Noise 0.134 μV p-p 0.1 Hz to 10 Hz

DAC REFERENCE INPUT

2

Reference Input Range 2.0 V

DD

V

Reference Input Resistance

3

9 kΩ Unipolar operation

7.5 kΩ Bipolar operation

Reference Input Capacitance 26 pF Code 0x0000

26 pF Code 0xFFFF

LOGIC INPUTS

Input Current ±1 μA

Input Low Voltage, V

INL

0.8 V V

DD

= 2.7 V to 5.5 V

Input High Voltage, V

INH

2.4 V V

DD

= 2.7 V to 5.5 V

Input Capacitance

2

10 pF

Hysteresis Voltage

2

0.15 V

V

DD

2.7 5.5 V All digital inputs at 0 V, V

LOGIC

, or V

DD

I

DD

125 150 µA V

IH

= V

LOGIC

or V

DD

and V

IL

= GND

V

LOGIC

1.8 5.5 V

I

LOGIC

15 24 µA All digital inputs at 0 V, V

LOGIC

, or V

DD

Power Dissipation 0.625 0.825 mW

1

For 2.7 V ≤ V

LOGIC

≤ 5.5 V, temperatures are as follows: A, B versions −40°C to +85°C.

2

Guaranteed by design, not subject to production test.

3

Reference input resistance is code-dependent, minimum at 0x8555.