LTC4000

23

4000fb

For more information www.linear.com/LTC4000

applicaTions inForMaTion

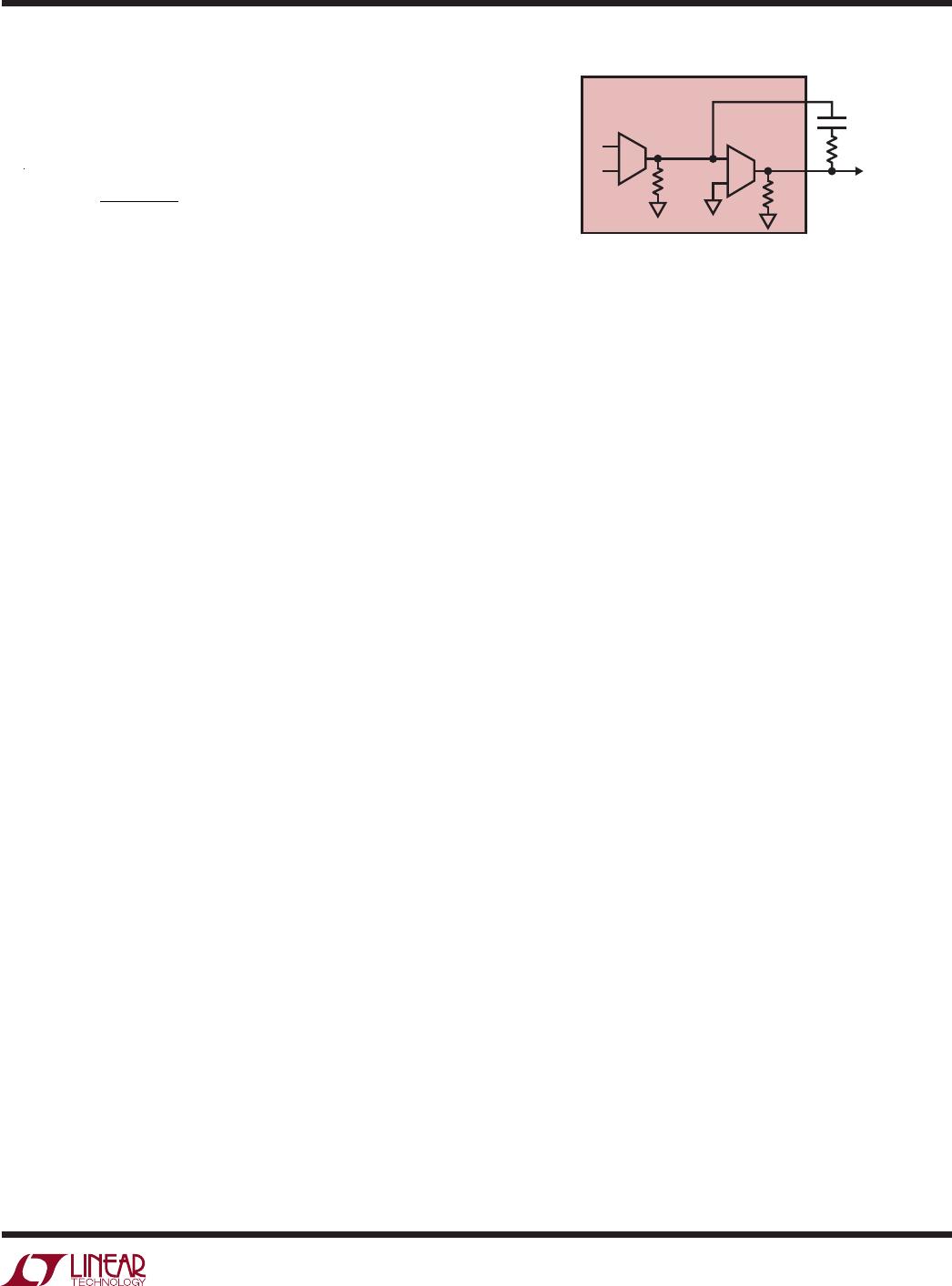

Figure 11. Error Amplifier Followed by Output Amplifier Driving

CC and ITH Pins

Setting the Input Voltage Monitoring Resistor Divider

The falling threshold voltage level for this monitoring

function can be calculated as follows:

R

VM1

=

V

VM _RST

1.193V

– 1

• R

VM2

where R

VM1

and R

VM2

form a resistor divider connected

between the monitored voltage and GND, with the center

tap point connected to the VM pin as shown in Figure 6. The

rising threshold voltage level can be calculated similarly.

Compensation

In order for the LTC4000 to control the external DC/DC

converter, it has to be able to overcome the sourcing bias

current of the ITH or VC pin of the DC/DC converter. The

typical sinking capability of the LTC4000 at the ITH pin is

1mA at 0.4V with a maximum voltage range of 0V to 6V.

It is imperative that the local feedback of the DC/DC con-

verter be set up such that during regulation of any of the

LTC4000 loops this local loop is out of regulation and

sources as much current as possible from its ITH/VC pin.

For example for a DC/DC converter regulating its output

voltage, it is recommended that the converter feedback

divider is programmed to be greater than 110% of the

output voltage regulation level programmed at the OFB pin.

There are four feedback loops to consider when setting up

the compensation for the LTC4000.

As mentioned

before

these loops are: the input current loop, the charge current

loop, the float voltage loop and the output voltage loop.

All of these loops have an error amp (A4-A7) followed by

another amplifier (A10) with the intermediate node driv-

ing the CC pin and the output of A10 driving the ITH pin

as shown in Figure 11. The most common compensation

network of a series capacitor (C

C

) and resistor (R

C

) between

the CC pin and the ITH pin is shown here.

Each of the loops has slightly different dynamics due to

differences in the feedback signal path. The analytic descrip-

tion of each of the loops is included in the Appendix sec-

tion. In most situations, an alternative empirical approach

to compensation, as described here, is more practical.

CC

ITH

LTC4000

–

+

C

C

4000 F11

R

C

A4-A7

g

m4-7

= 0.2m

A10

g

m10

= 0.1m

+

–

R

O4-7

R

O10

Empirical Loop Compensation

Based on the five analytical expressions given in the Ap-

pendix section, and the transfer function from the ITH

pin to the input and output current of the external DC/DC

converter, the user can analytically determine the complete

loop transfer function of each of the loops. Once these are

obtained, it is a matter of analyzing the gain and phase

bode plots to ensure that there is enough phase and gain

margin at unity crossover with the selected values of R

C

and C

C

for all operating conditions.

Even though it is clear that an analytical compensation

method is possible, sometimes certain complications

render this method difficult to tackle. These complica-

tions include the lack of easy availability of the switching

converter transfer function from the ITH or VC control

node to its input or output current, and the variability of

parameter values of the components such as the ESR of

the output capacitor or the R

DS(ON)

of the external PFETs.

Therefore a simpler and more practical way to compensate

the LTC4000 is provided here. This empirical method

involves injecting an AC signal into the loop, observing

the loop transient response and adjusting the

C

C

and R

C

values to quickly iterate towards the final values. Much

of the detail of this method is derived from Application

Note19 which can be found at www.linear.com using

AN19 in the search box.

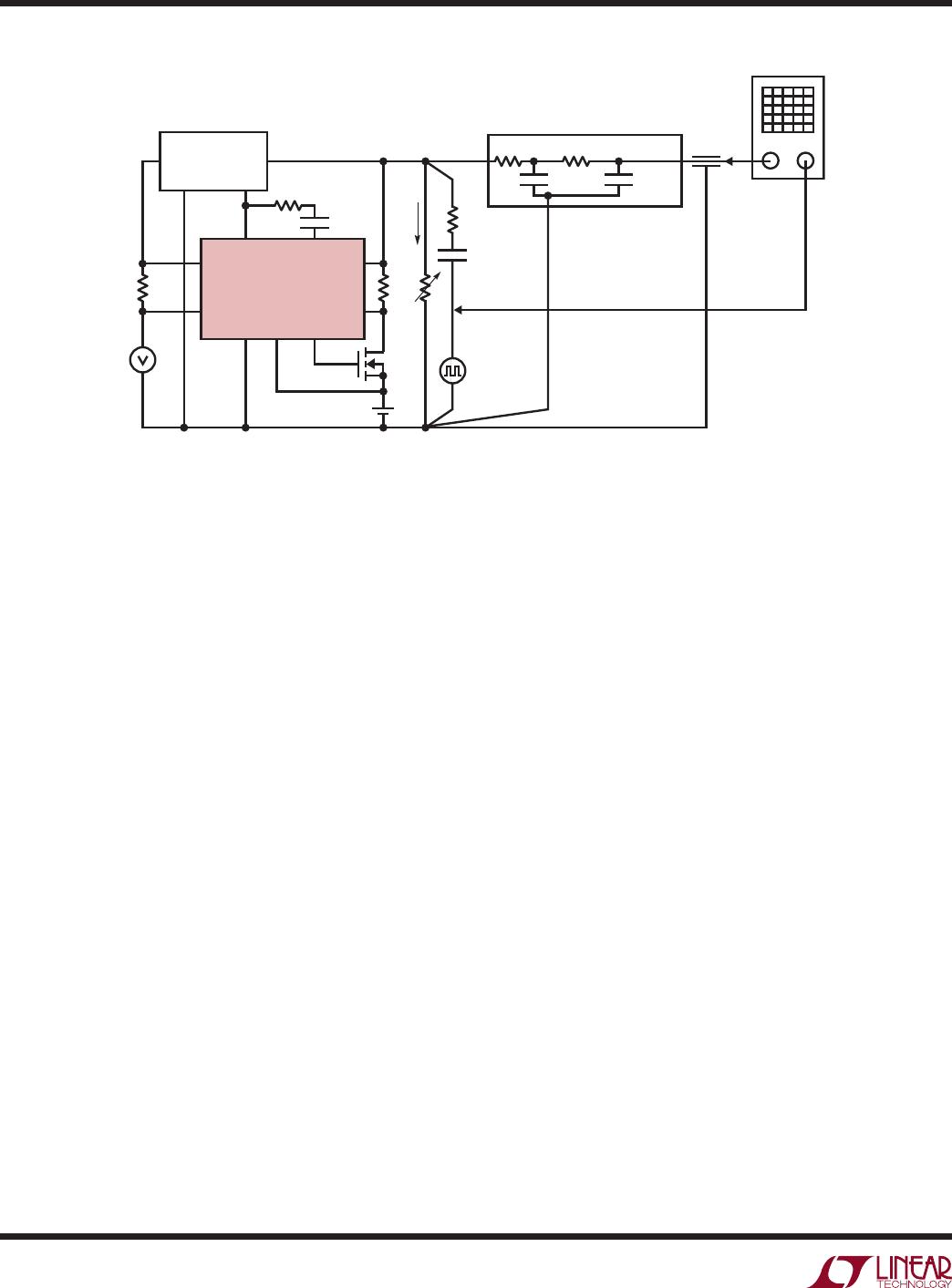

Figure 12 shows the recommended setup to inject an

AC-coupled output load variation into the loop. A function

generator with 50Ω output impedance is coupled through

a 50Ω/1000µF series RC network to the regulator output.