LTC4000

31

4000fb

For more information www.linear.com/LTC4000

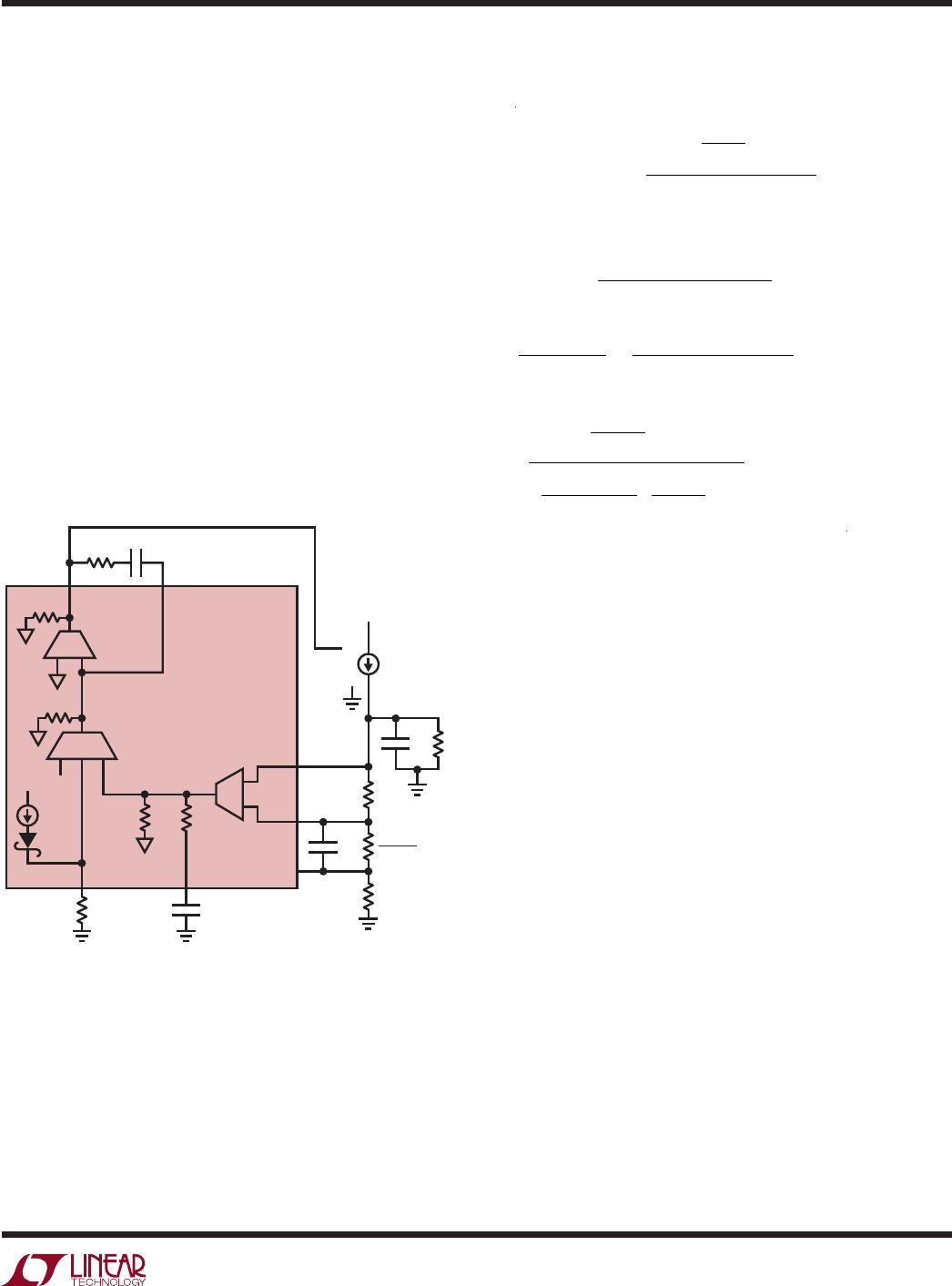

The Output Voltage Regulation Loop

The feedback signal for the output voltage regulation loop

is the voltage on the OFB pin, which is connected to the

center node of the resistor divider between the output

voltage (connected to C

SP

) and the FBG pin. This voltage

is compared to an internal reference (1.193V typical) by

the transconductance error amplifier A7. This amplifier

then drives the output transconductance amplifier (A10)

to appropriately adjust the voltage on the ITH pin driving

the external DC/DC converter to regulate the output volt-

age observed by the OFB pin. This loop is shown in detail

in Figure 21.

Figure 21. Simplified Linear Model of the Output Voltage

Regulation Loop

Figure 22. Simplified Linear Model of the Battery Float

Voltage Regulation Loop

The simplified loop transmission is as follows:

L

OV

(s) = g

m7

R

C

–

1

g

m10

C

C

s + 1

C

C

s

•

R

OFB2

R

OFB

•

R

L

R

L

• C

L

s + 1

• Gmo

p

(s)

where Gmo

p

(s) is the transfer function from V

ITH

to

the output current of the external DC/DC converter, and

R

OFB

= R

OFB1

+ R

OFB2

.

applicaTions inForMaTion

The Battery Float Voltage Regulation Loop

The battery float voltage regulation loop is very similar to

the output float voltage regulation loop. Instead of observ-

ing the voltage at the OFB pin, the battery float voltage

regulation loop observes the voltage at the BFB pin.

One significant difference is that while the value of R

L

in the output voltage loop can vary significantly, the

output resistance of the battery float voltage loop is a

small constant value approximately equal to the sum

of the on-resistance of the external PFET (R

DS(ON)

) and

the series internal resistance of the battery (R

BAT

). This

approximation is valid for any efficient system such that

most of the output power from the battery is delivered to

the system load and not dissipated on the battery inter-

nal resistance or the charging PFET on-resistance. For a

typical system, minimum R

L

is at least five times larger

than R

DS(ON)

+ R

BAT

and R

BFB

is at least 10

6

times larger

than R

BAT

. Figure 22 shows the detail of the battery float

voltage regulation loop.

CC

A7

g

m6

= 0.5m

A10

g

m10

= 0.1m

ITH

INPUT

BAT

INTERNALLY

PULLED HIGH

BFB

LTC4000

FBG

+

–

–

+

C

C

4000 F22

R

C

1.136V

R

BFB1

Gmo

p

(s)

R

BFB2

R

O6

R

O10

C

L

R

L

+

–

R

BAT

R

DS(ON)

R

CS

LOAD

CC

A7

g

m7

= 0.5m

A10

g

m10

= 0.1m

ITH

INPUT

LOAD

CSP

INTERNALLY

PULLED HIGH

OFB

LTC4000

FBG

+

–

–

+

C

C

4000 F21

R

C

1.193V

R

OFB1

Gmo

p

(s)

R

OFB2

R

O7

R

O10

C

L

R

L

+

–