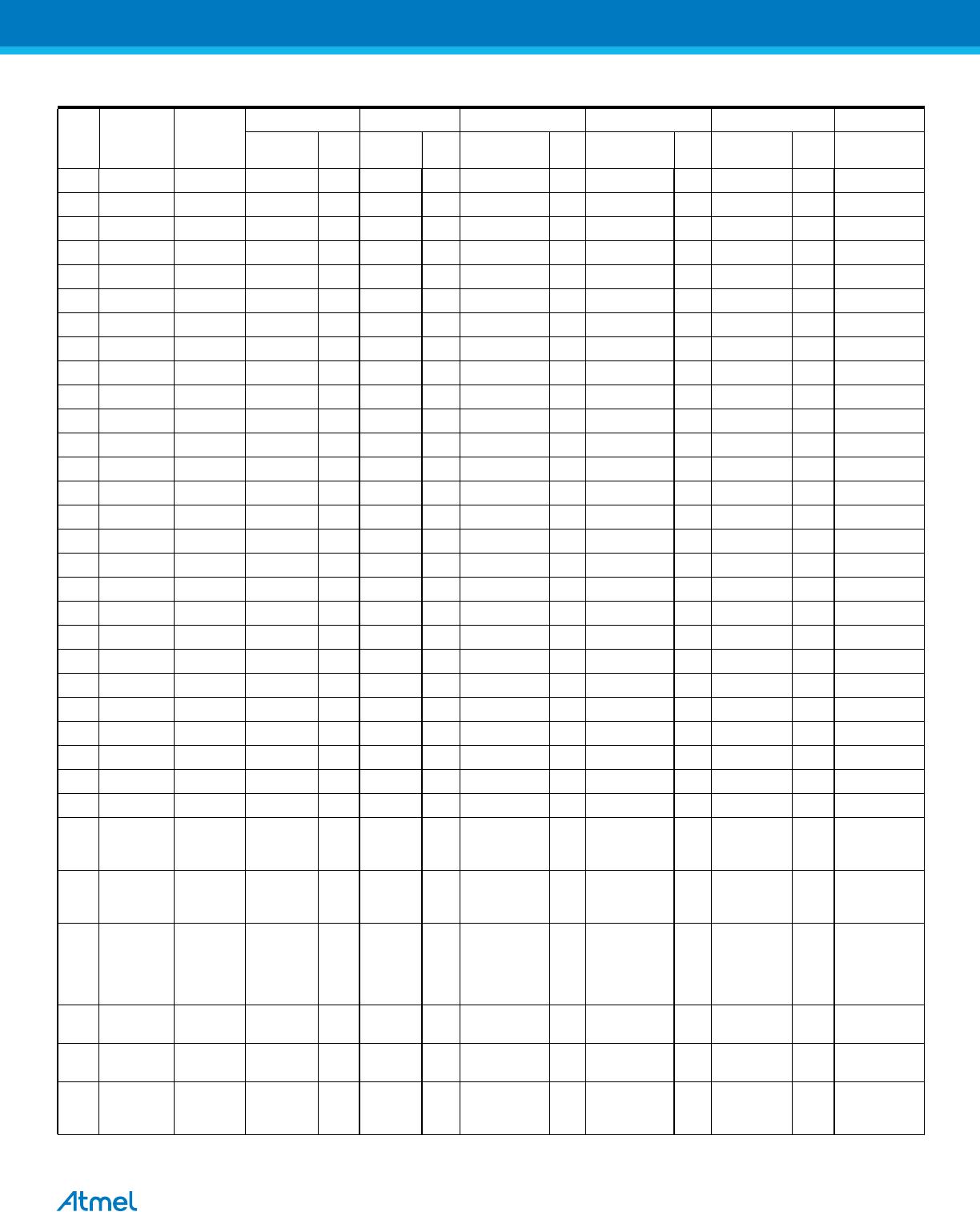

13

SAM9N12/SAM9CN11/SAM9CN12 [SUMMARY DATASHEET]

11063HS–ATARM–27-Sep-13

T1

VDDIOP1 GPIO PC27 I/O LCDVSYNC O RTS1 O PIO, I, PU, ST

M4

VDDIOP1 GPIO PC28 I/O LCDHSYNC O CTS1 I PIO, I, PU, ST

N4

VDDIOP1 GPIO_CLK PC29 I/O LCDDEN O SCK1 I/O PIO, I, PU, ST

T2

VDDIOP1 GPIO_CLK2 PC30 I/O LCDPCK O PIO, I, PU, ST

U1

VDDIOP1 GPIO PC31 I/O FIQ I PCK1 O PIO, I, PU, ST

P15

VDDNF EBI PD0 I/O NANDOE O PIO, I, PU

N14

VDDNF EBI PD1 I/O NANDWE O PIO, I, PU

M15

VDDNF EBI PD2 I/O A21/NANDALE O A21,O, PD

M14

VDDNF EBI PD3 I/O A22/NANDCLE O A22,O, PD

P16

VDDNF EBI PD4 I/O NCS3 O PIO, I, PU

M17

VDDNF EBI PD5 I/O NWAIT I PIO, I, PU

L15

VDDNF EBI PD6 I/O D16 O PIO, I, PU

L16

VDDNF EBI PD7 I/O D17 O PIO, I, PU

L17

VDDNF EBI PD8 I/O D18 O PIO, I, PU

K17

VDDNF EBI PD9 I/O D19 O PIO, I, PU

K16

VDDNF EBI PD10 I/O D20 O PIO, I, PU

K15

VDDNF EBI PD11 I/O D21 O PIO, I, PU

J17

VDDNF EBI PD12 I/O D22 O PIO, I, PU

J16

VDDNF EBI PD13 I/O D23 O PIO, I, PU

H17

VDDNF EBI PD14 I/O D24 O PIO, I, PU

J15

VDDNF EBI PD15 I/O D25 O A20 O A20, O, PD

G17

VDDNF EBI PD16 I/O D26 O A23 O A23, O, PD

H16

VDDNF EBI PD17 I/O D27 O A24 O A24, O, PD

H15

VDDNF EBI PD18 I/O D28 O A25 O A25, O, PD

F17

VDDNF EBI PD19 I/O D29 O NCS2 O PIO, I, PU

G16

VDDNF EBI PD20 I/O D30 O NCS4 O PIO, I, PU

E17

VDDNF EBI PD21 I/O D31 O NCS5 O PIO, I, PU

H8

H9

H10

VDDIOM POWER VDDIOM I I

J14

K14

L14

VDDNF POWER VDDNF I I

J8

J9

J10

K9

K10

GNDIOM GND GNDIOM I I

P9

P12

VDDIOP0 POWER VDDIOP0 I I

L3

L4

VDDIOP1 POWER VDDIOP1 I I

P6

P7

P13

GNDIOP GND GNDIOP I I

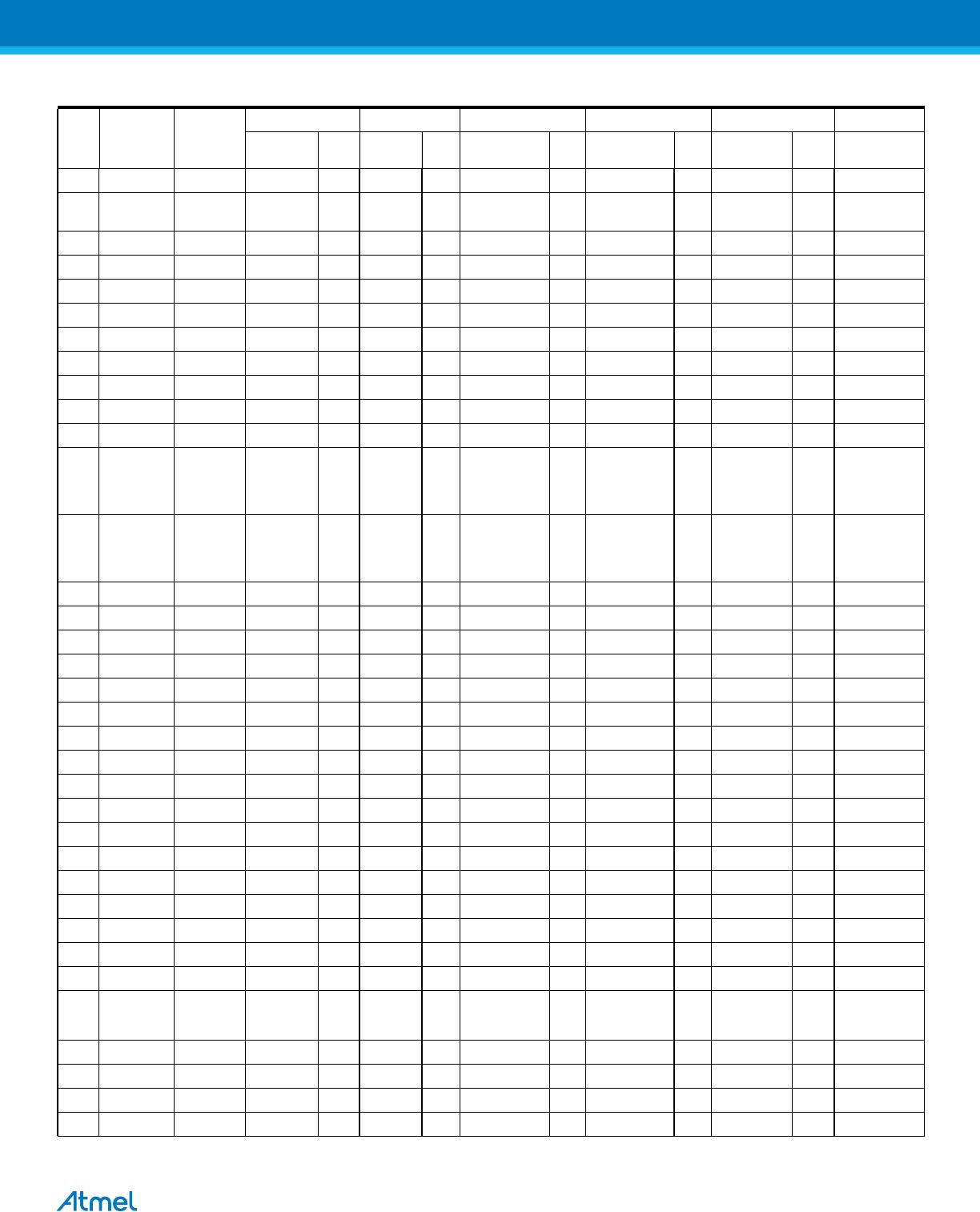

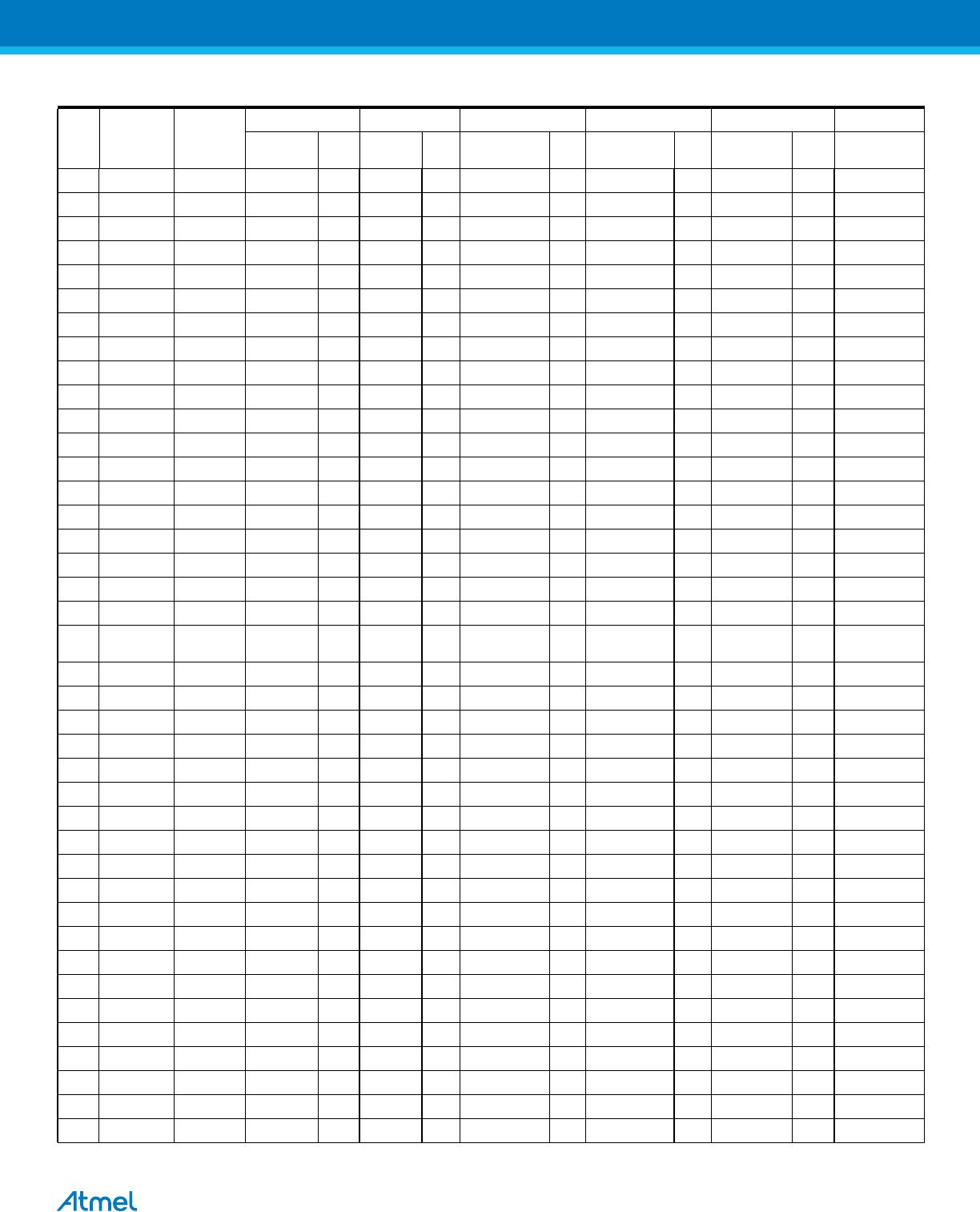

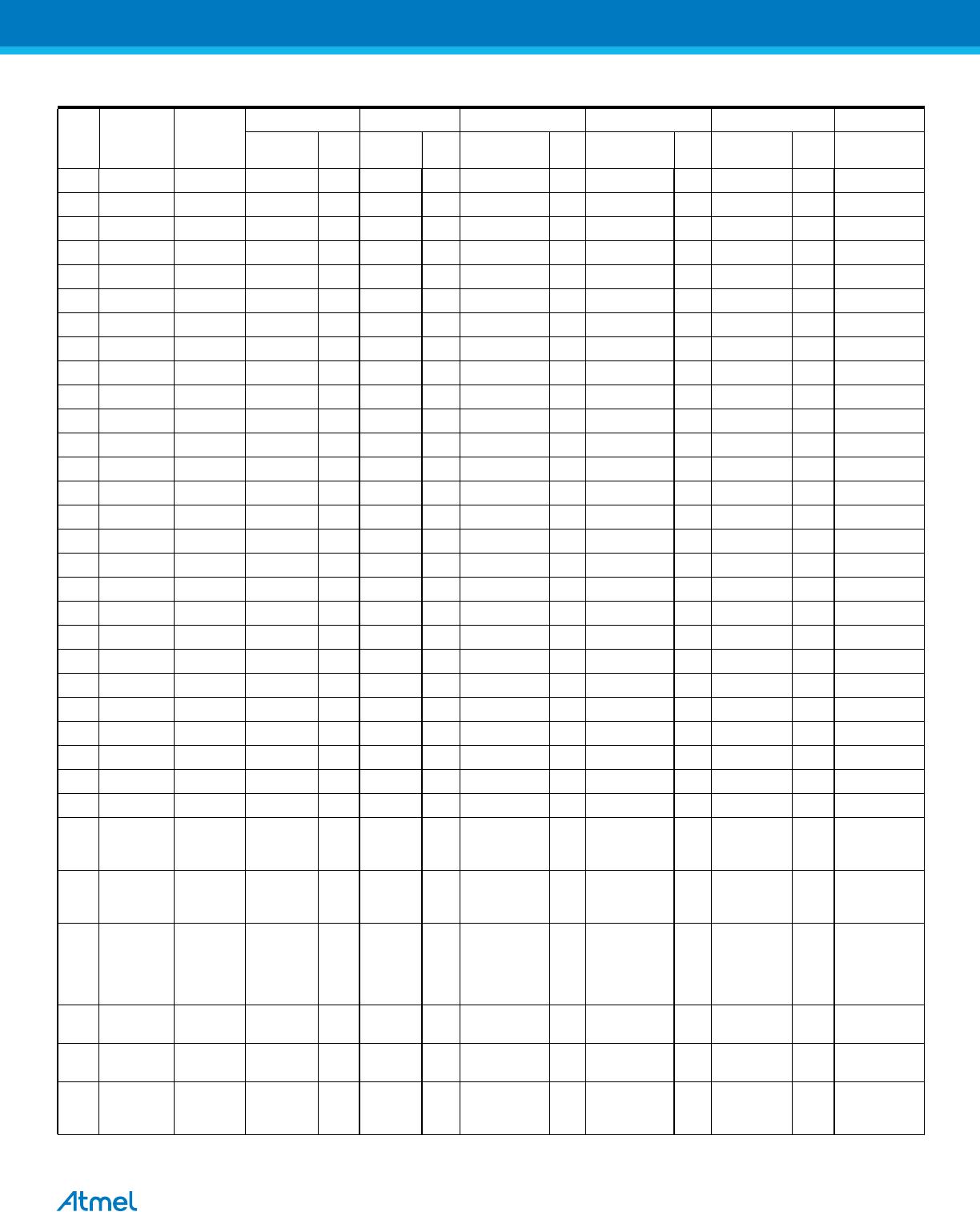

Table 4-1. BGA217 Pin Description (Continued)

Ball Power Rail I/O Type

Primary Alternate PIO Peripheral A PIO Peripheral B PIO Peripheral C Reset State

Signal Dir Signal Dir Signal Dir Signal Dir Signal Dir

Signal, Dir, PU,

PD, ST