AD650 Data Sheet

Rev. E | Page 10 of 20

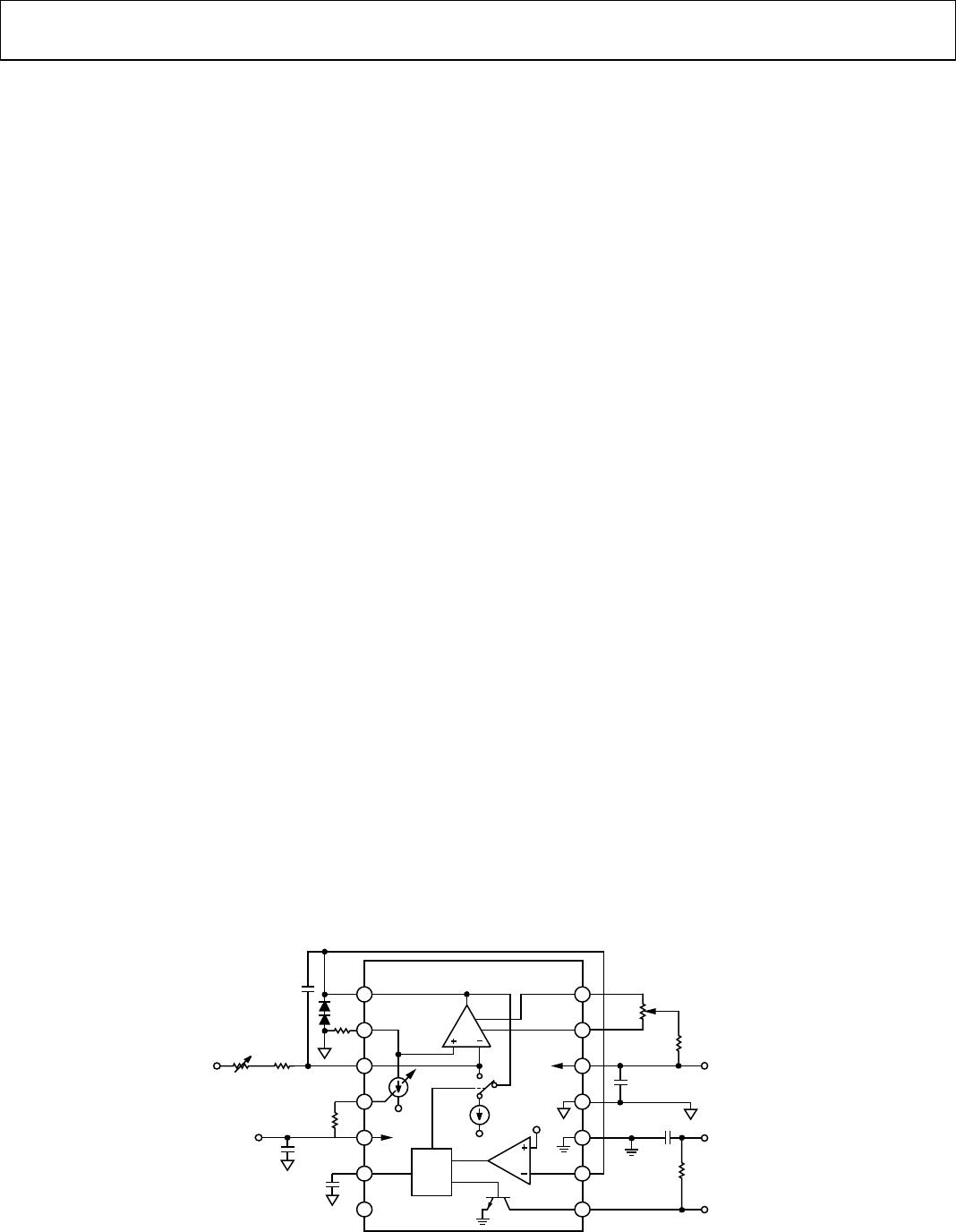

BIPOLAR V/F

Figure 11 shows how the internal bipolar current sink is used to

provide a half-scale offset for a ±5 V signal range, while providing

a 100 kHz maximum output frequency. The nominally 0.5 mA

(±10%) offset current sink is enabled when a 1.24 kΩ resistor is

connected between Pin 4 and Pin 5. Thus, with the grounded

10 kΩ nominal resistance shown, a −5 V offset is developed at

Pin 2. Because Pin 3 must also be at −5 V, the current through R

IN

is 10 V/40 kΩ = +0.25 mA at V

IN

= +5 V, and 0 mA at V

IN

= –5 V.

Components are selected using the same guidelines outlined for

the unipolar configuration with one alteration. The voltage

across the total signal range must be equated to the maximum

input voltage in the unipolar configuration. In other words, the

value of the input resistor R

IN

is determined by the input voltage

span, not the maximum input voltage. A diode from Pin 1 to

ground is also recommended. This is further discussed in the

Other Circuit Considerations section.

As in the unipolar circuit, R

IN

and C

OS

must have low temperature

coefficients to minimize the overall gain drift. The 1.24 kΩ

resistor used to activate the 0.5 mA offset current should also

have a low temperature coefficient. The bipolar offset current

has a temperature coefficient of approximately −200 ppm/°C.

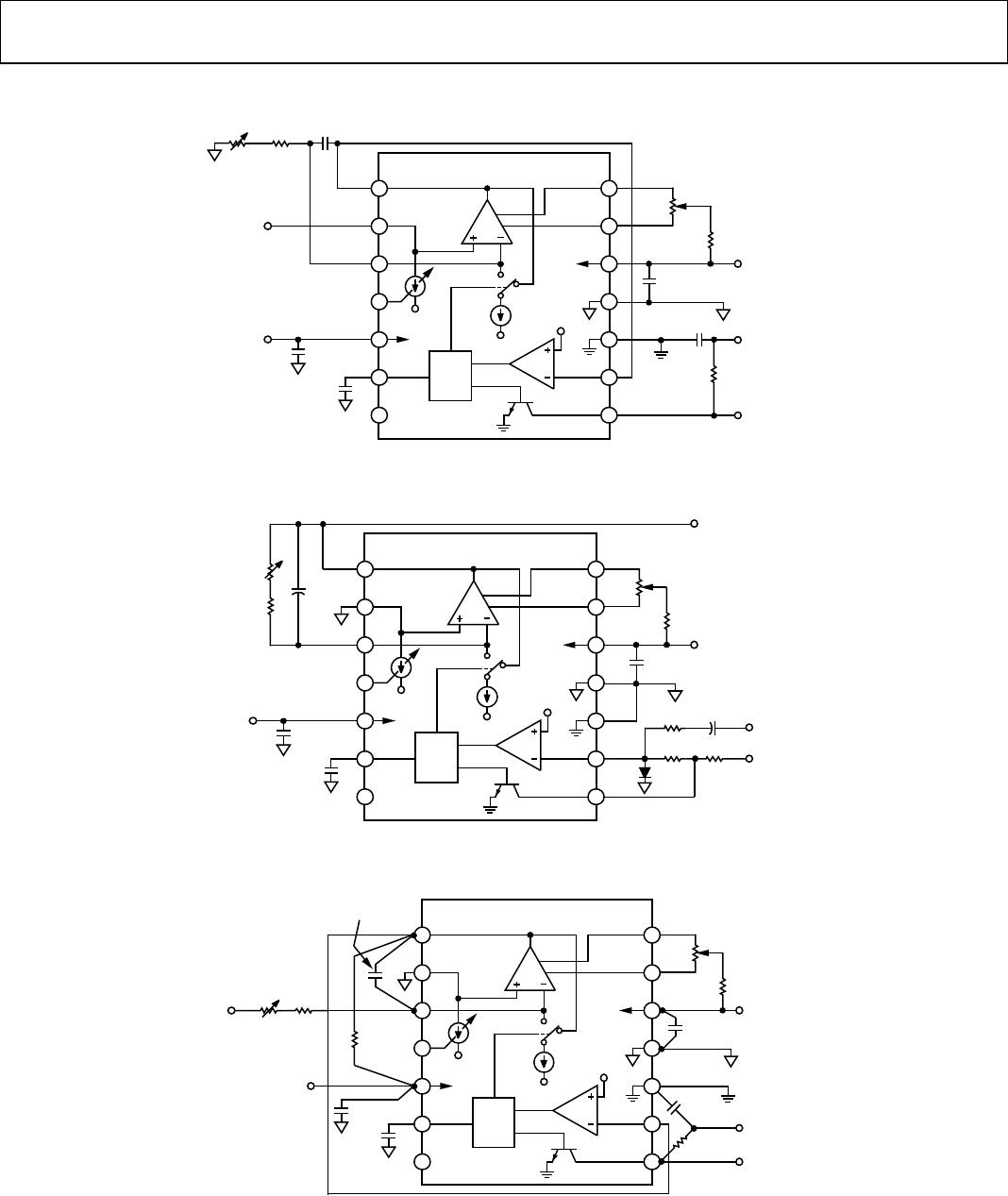

UNIPOLAR V/F, NEGATIVE INPUT VOLTAGE

Figure 12 shows the connection diagram for V/F conversion of

negative input voltages. In this configuration, full-scale output

frequency occurs at negative full-scale input, and zero output

frequency corresponds with zero input voltage.

A very high impedance signal source can be used because it only

drives the noninverting integrator input. Typical input impedance

at this terminal is 1 GΩ or higher. For V/F conversion of positive

input signals using the connection diagram of Figure 4, the

signal generator must be able to source the integration current

to drive the AD650. For the negative V/F conversion circuit of

Figure 12, the integration current is drawn from ground

through R1 and R3, and the active input is high impedance.

Circuit operation for negative input voltages is very similar to

positive input unipolar conversion described in the Unipolar

Configuration section. For best operating results use Equation 7

and Equation 8 in the Component Selection section.

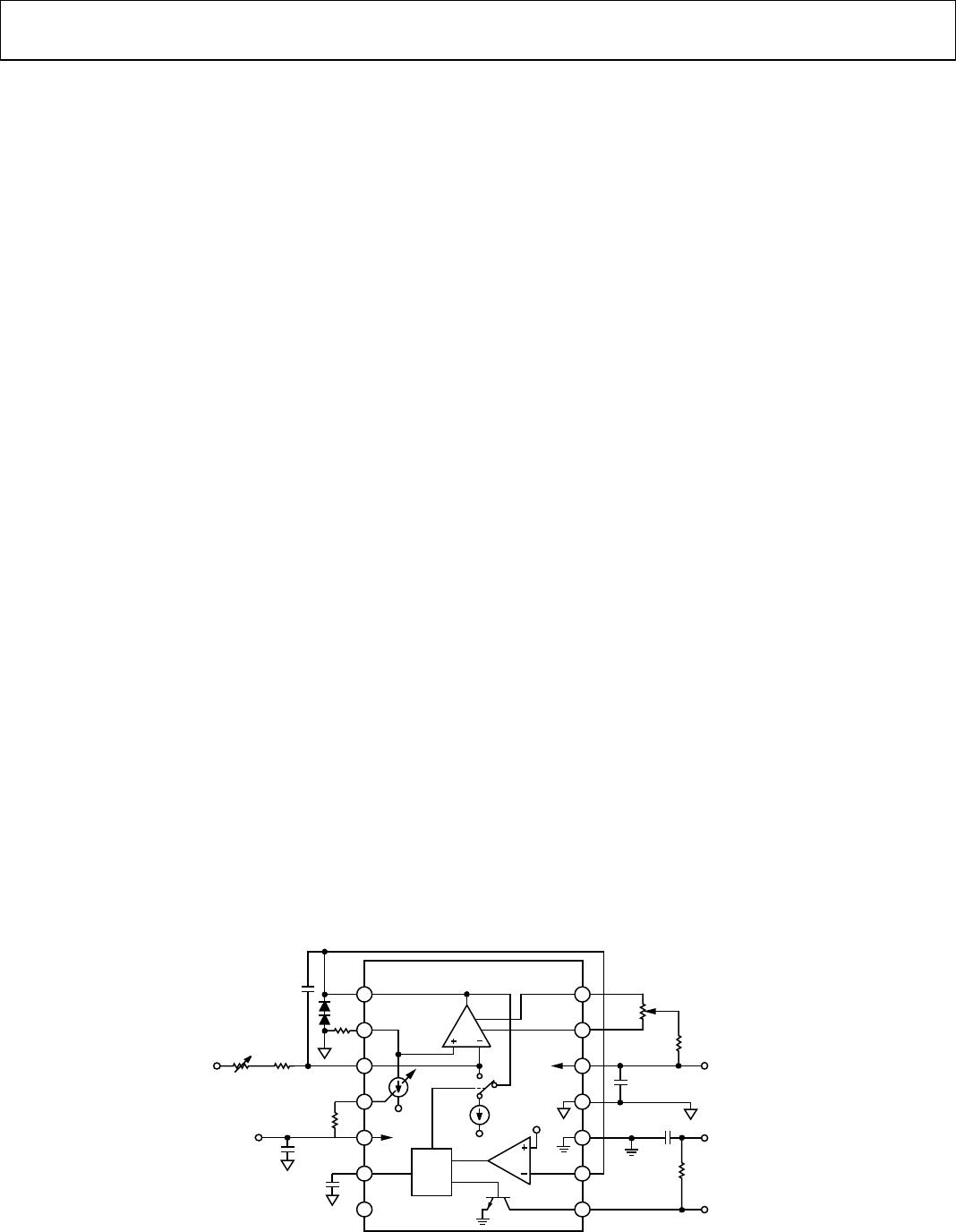

F/V CONVERSION

The AD650 also makes a very linear frequency-to-voltage

converter. Figure 13 shows the connection diagram for F/V

conversion with TTL input logic levels. Each time the input

signal crosses the comparator threshold going negative, the one

shot is activated and switches 1 mA into the integrator input for

a measured time period (determined by C

OS

). As the frequency

increases, the amount of charge injected into the integration

capacitor increases proportionately. The voltage across the

integration capacitor is stabilized when the leakage current

through R1 and R3 equals the average current being switched

into the integrator. The net result of these two effects is an

average output voltage that is proportional to the input

frequency. Optimum performance can be obtained by selecting

components using the same guidelines and equations listed in

the Bipolar V/F section.

For a more complete description of this application, refer to

Analog Devices’ Application Note AN-279.

HIGH FREQUENCY OPERATION

Proper RF techniques must be observed when operating the

AD650 at or near its maximum frequency of 1 MHz. Lead

lengths must be kept as short as possible, especially on the one

shot and integration capacitors, and at the integrator summing

junction. In addition, at maximum output frequencies above

500 kHz, a 3.6 kΩ pull-down resistor from Pin 1 to −V

S

is

required (see Figure 14). The additional current drawn through

the pulldown resistor reduces the op amp’s output impedance

and improves its transient response.

00797-012

OP

AMP

COMP

IN

FREQ

OUT

OUT

ONE

SHOT

8

9

10

11

13

12

7

6

5

4

3

2

1 14

INPUT

OFFSET

TRIM

–0.6V

AD650

–V

S

–V

S

1mA

S1

C

OS

330pF

–15V

0.1µF

V

IN

±5

1.24kΩ

R3

37.4kΩ

10kΩ

R1

5kΩ

C

INT

1000pF

20kΩ

250kΩ

0.1µF

1µF

1kΩ

+15V

+5V

DIGITAL

GND

ANALOG

GND

F

OUT

Figure 11. Connections for ±5 V Bipolar V/F with 0 kHz to 100 kHz TTL Output