ADF4110/ADF4111/ADF4112/ADF4113 Data Sheet

Rev. F | Page 2 of 28

TABLE OF CONTENTS

Features .............................................................................................. 1

Applications ....................................................................................... 1

General Description ......................................................................... 1

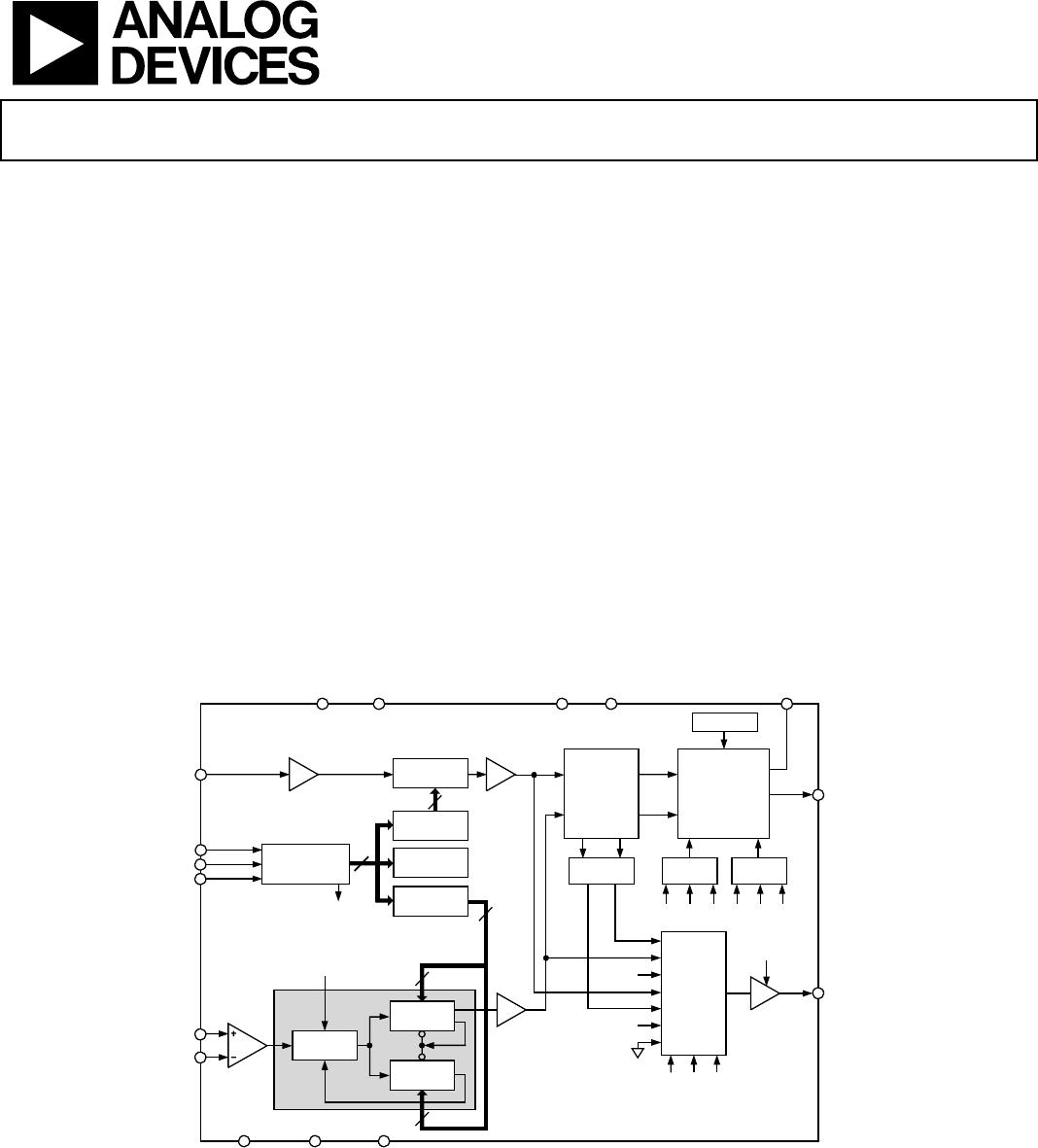

Functional Block Diagram .............................................................. 1

Revision History ............................................................................... 2

Specifications ..................................................................................... 3

Timing Characteristics ..................................................................... 5

Absolute Maximum Ratings ............................................................ 6

Transistor Count ........................................................................... 6

ESD Caution .................................................................................. 6

Pin Configurations and Function Descriptions ........................... 7

Typical Performance Characteristics ............................................. 8

Circuit Description ......................................................................... 12

Reference Input Section ............................................................. 12

RF Input Stage ............................................................................. 12

Prescaler (P/P + 1) ...................................................................... 12

A and B Counters ....................................................................... 12

R Counter .................................................................................... 12

Phase Frequency Detector (PFD) and Charge Pump ............ 13

Muxout and Lock Detect ........................................................... 13

Input Shift Register .................................................................... 13

Function Latch ............................................................................ 19

Initialization Latch ..................................................................... 20

Device Programming after Initial Power-Up ......................... 20

Resynchronizing the Prescaler Output .................................... 21

Applications ..................................................................................... 22

Local Oscillator for GSM Base Station Transmitter .............. 22

Using a D/A Converter to Drive the R

SET

Pin ......................... 23

Shutdown Circuit ....................................................................... 23

Wideband PLL ............................................................................ 23

Direct Conversion Modulator .................................................. 25

Interfacing ................................................................................... 26

PCB Design Guidelines for Chip Scale Package .................... 26

Outline Dimensions ....................................................................... 27

Ordering Guide ............................................................................... 28

REVISION HISTORY

1/13—Rev. E to Rev. F

Changes to Table 1 ............................................................................. 4

Changes to Ordering Guide ........................................................... 28

8/12—Rev. D to Rev. E

Changed CP-20-1 to CP-20-6 ........................................... Universal

Updated Outline Dimensions ........................................................ 28

Changes to Ordering Guide ........................................................... 28

5/12—Rev. C to Rev. D

Changes to Figure 2 ........................................................................... 5

Changes to Figure 4 and Table 4 ...................................................... 7

Updated Outline Dimensions ........................................................ 28

Changes to Ordering Guide ........................................................... 28

3/04—Data sheet changed from Rev. B to Rev. C.

Updated Format .................................................................. Universal

Changes to Specifications ................................................................. 2

Changes to Figure 32 ....................................................................... 22

Changes to the Ordering Guide ..................................................... 28

3/03—Data sheet changed from Rev. A to Rev. B.

Edits to Specifications ....................................................................... 2

Updated OUTLINE DIMENSIONS ............................................. 24

1/01—Data sheet changed from Rev. 0 to Rev. A.

Changes to DC Specifications in B Version, B Chips,

Unit, and Test Conditions/Comments Columns ..................... 2

Changes to Absolute Maximum Rating ......................................... 4

Changes to FR

IN

A Function Test ..................................................... 5

Changes to Figure 8 ........................................................................... 7

New Graph Added—TPC 22 ........................................................... 9

Change to PD Polarity Box in Table V ......................................... 15

Change to PD Polarity Box in Table VI ........................................ 16

Change to PD Polarity Paragraph ................................................. 17

Addition of New Material

(PCB Design Guidelines for Chip–Scale package) ................ 23

Replacement of CP-20 Outline with CP-20 [2] Outline ............ 24