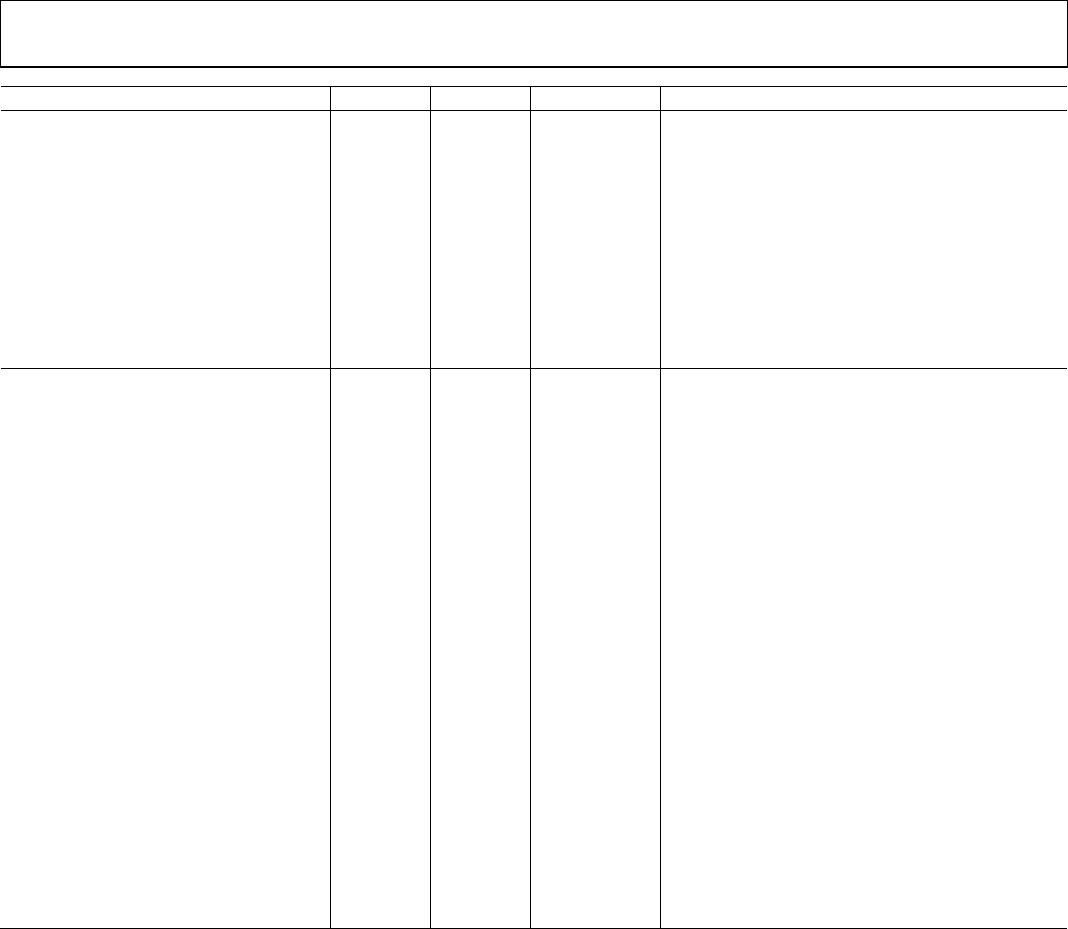

ADF4110/ADF4111/ADF4112/ADF4113 Data Sheet

Rev. F | Page 4 of 28

Parameter B Version B Chips

1

Unit Test Conditions/Comments

POWER SUPPLIES

AV

DD

2.7/5.5 2.7/5.5 V min/V max

DV

DD

AV

DD

AV

DD

V

P

AV

DD

/6.0 AV

DD

/6.0 V min/V max

AV

DD

≤ V

P

≤ 6.0 V. See Figure 25 and Figure 26.

I

DD

5

(AI

DD

+ DI

DD

)

ADF4110 5.5 4.5 mA max 4.5 mA typical.

ADF4112 7.5 6.5 mA max 6.5 mA typical.

ADF4113 11 8.5 mA max 8.5 mA typical.

I

P

0.5 0.5 mA max T

A

= 25°C.

Low Power Sleep Mode 1 1 µA typ

NOISE CHARACTERISTICS

ADF4113 Normalized Phase Noise Floor

6

Phase Noise Performance

7

@ VCO output.

ADF4110: 540 MHz Output

8

−91 −91 dBc/Hz typ @ 1 kHz offset and 200 kHz PFD frequency.

ADF4111: 900 MHz Output

9

@ 1 kHz offset and 200 kHz PFD frequency.

ADF4112: 900 MHz Output

9

−90 −90 dBc/Hz typ @ 1 kHz offset and 200 kHz PFD frequency.

ADF4113: 900 MHz Output

9

−91 −91 dBc/Hz typ @ 1 kHz offset and 200 kHz PFD frequency.

ADF4111: 836 MHz Output

10

−78 −78 dBc/Hz typ @ 300 Hz offset and 30 kHz PFD frequency.

ADF4112: 1750 MHz Output

11

−86 −86 dBc/Hz typ @ 1 kHz offset and 200 kHz PFD frequency.

12

@ 200 Hz offset and 10 kHz PFD frequency.

ADF4112: 1960 MHz Output

13

−84 −84 dBc/Hz typ @ 1 kHz offset and 200 kHz PFD frequency.

ADF4113: 1960 MHz Output

13

−85 −85 dBc/Hz typ @ 1 kHz offset and 200 kHz PFD frequency.

ADF4113: 3100 MHz Output

14

−86 −86 dBc/Hz typ @ 1 kHz offset and 1 MHz PFD frequency.

Spurious Signals

ADF4110: 540 MHz Output

9

−97/−106 −97/−106 dBc typ @ 200 kHz/400 kHz and 200 kHz PFD frequency.

ADF4111: 900 MHz Output

9

−98/−110 −98/−110 dBc typ @ 200 kHz/400 kHz and 200 kHz PFD frequency.

ADF4112: 900 MHz Output

9

−91/−100 −91/−100 dBc typ @ 200 kHz/400 kHz and 200 kHz PFD frequency.

ADF4113: 900 MHz Output

9

−100/−110 −100/−110 dBc typ @ 200 kHz/400 kHz and 200 kHz PFD frequency.

10

@ 30 kHz/60 kHz and 30 kHz PFD frequency.

ADF4112: 1750 MHz Output

11

−88/−90 −88/−90 dBc typ @ 200 kHz/400 kHz and 200 kHz PFD frequency.

ADF4112: 1750 MHz Output

12

−65/−73 −65/−73 dBc typ @ 10 kHz/20 kHz and 10 kHz PFD frequency.

ADF4112: 1960 MHz Output

13

@ 200 kHz/400 kHz and 200 kHz PFD frequency.

ADF4113: 1960 MHz Output

13

−80/−84 −80/−84 dBc typ @ 200 kHz/400 kHz and 200 kHz PFD frequency.

ADF4113: 3100 MHz Output

14

−80/−82 −82/−82 dBc typ @ 1 MHz/2 MHz and 1 MHz PFD frequency.

1

The B chip specifications are given as typical values.

2

This is the maximum operating frequency of the CMOS counters. The prescaler value should be chosen to ensure that the RF input is divided down to a frequency that

is less than this value.

3

AC coupling ensures AV

DD

/2 bias. See Figure 33 for a typical circuit.

4

Guaranteed by design.

5

T

A

= 25°C; AV

DD

= DV

DD

= 3 V; P = 16; SYNC = 0; DLY = 0; RF

IN

for ADF4110 = 540 MHz; RF

IN

for ADF4111, ADF4112, ADF4113 = 900 MHz.

6

The synthesizer phase noise floor is estimated by measuring the in-band phase noise at the output of the VCO, PN

TOT

, and subtracting 20logN (where N is the N divider

value) and 10logF

PFD

: PN

SYNTH

= PN

TOT

– 10logF

PFD

– 20logN.

7

The phase noise is measured with the EV-ADF411XSD1Z evaluation board and the HP8562E spectrum analyzer. The spectrum analyzer provides the REFIN for the

synthesizer (f

REFOUT

= 10 MHz @ 0 dBm). SYNC = 0; DLY = 0 (Table 7).

8

f

REFIN

= 10 MHz; f

PFD

= 200 kHz; offset frequency = 1 kHz; f

RF

= 540 MHz; N = 2700; loop B/W = 20 kHz.

9

f

REFIN

= 10 MHz; f

PFD

= 200 kHz; offset frequency = 1 kHz; f

RF

= 900 MHz; N = 4500; loop B/W = 20 kHz.

10

f

REFIN

= 10 MHz; f

PFD

= 30 kHz; offset frequency = 300 Hz; f

RF

= 836 MHz; N = 27867; loop B/W = 3 kHz.

11

f

REFIN

= 10 MHz; f

PFD

= 200 kHz; offset frequency = 1 kHz; f

RF

= 1750 MHz; N = 8750; loop B/W = 20 kHz

12

f

REFIN

= 10 MHz; f

PFD

= 10 kHz; offset frequency = 200 Hz; f

RF

= 1750 MHz; N = 175000; loop B/W = 1 kHz.

13

f

REFIN

= 10 MHz; f

PFD

= 200 kHz; offset frequency = 1 kHz; f

RF

= 1960 MHz; N = 9800; loop B/W = 20 kHz.

14

f

REFIN

= 10 MHz; f

PFD

= 1 MHz; offset frequency = 1 kHz; f

RF

= 3100 MHz; N = 3100; loop B/W = 20 kHz.