AD7400A Data Sheet

Rev. D | Page 14 of 20

DIFFERENTIAL INPUTS

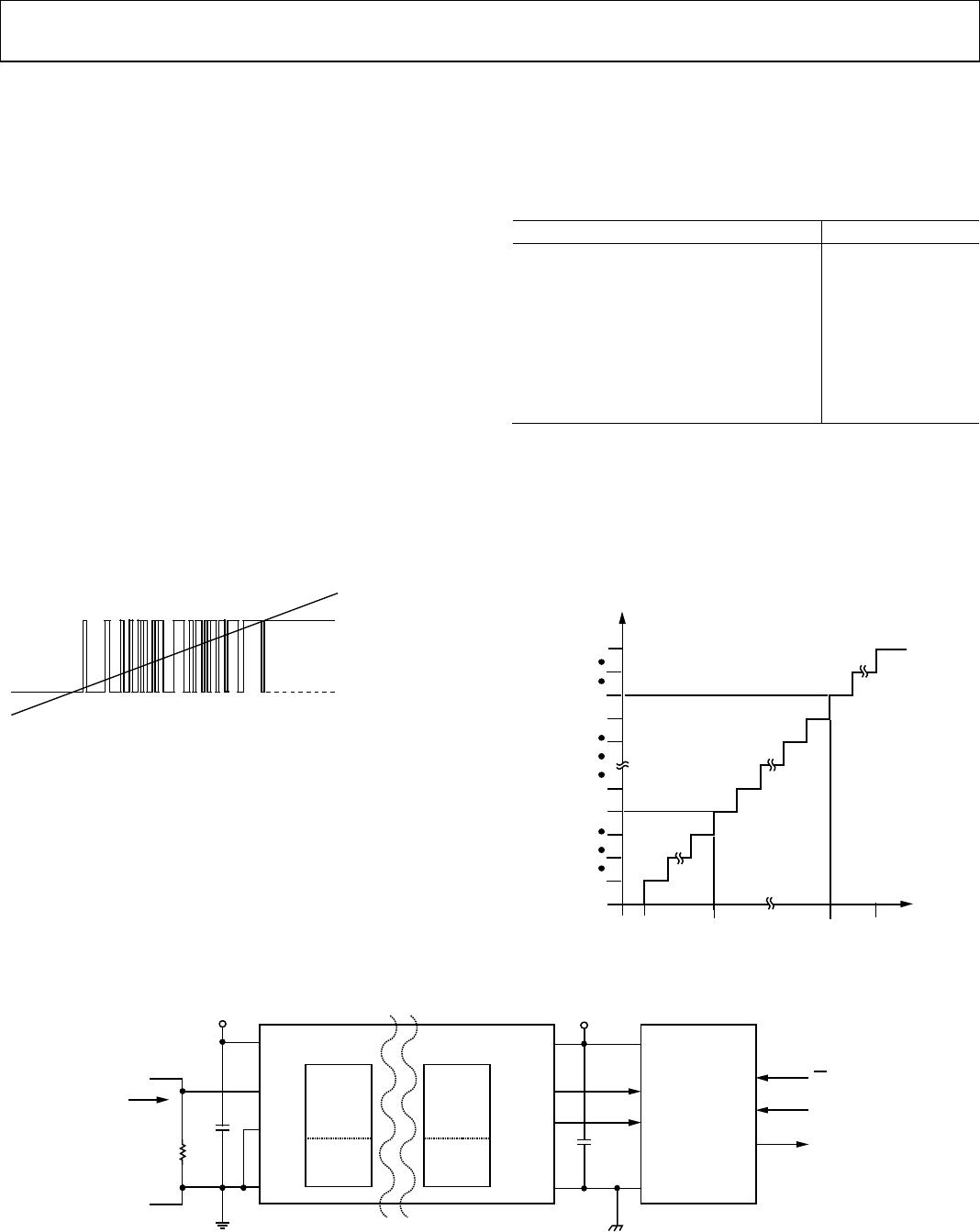

The analog input to the modulator is a switched capacitor

design. The analog signal is converted into charge by highly

linear sampling capacitors. A simplified equivalent circuit

diagram of the analog input is shown in Figure 22. A signal

source driving the analog input must be able to provide the

charge onto the sampling capacitors every half MCLKOUT cycle

and settle to the required accuracy within the next half cycle.

φA

φB

1kΩ

V

IN

–

φA

φB

φB φB

1kΩ

V

IN

+

2pF

2pF

φA φA

MCLKOUT

07077-027

Figure 22. Analog Input Equivalent Circuit

Because the AD7400A samples the differential voltage across its

analog inputs, low noise performance is attained with an input

circuit that provides low common-mode noise at each input.

The amplifiers used to drive the analog inputs play a critical

role in attaining the high performance available from the

AD7400A.

When a capacitive load is switched onto the output of an op

amp, the amplitude drops momentarily. The op amp tries to

correct the situation and, in the process, hits its slew rate limit.

This nonlinear response, which can cause excessive ringing, can

lead to distortion. To remedy the situation, a low-pass RC filter

can be connected between the amplifier and the input to the

AD7400A. The external capacitor at each input aids in supplying

the current spikes created during the sampling process, and the

resistor isolates the op amp from the transient nature of the load.

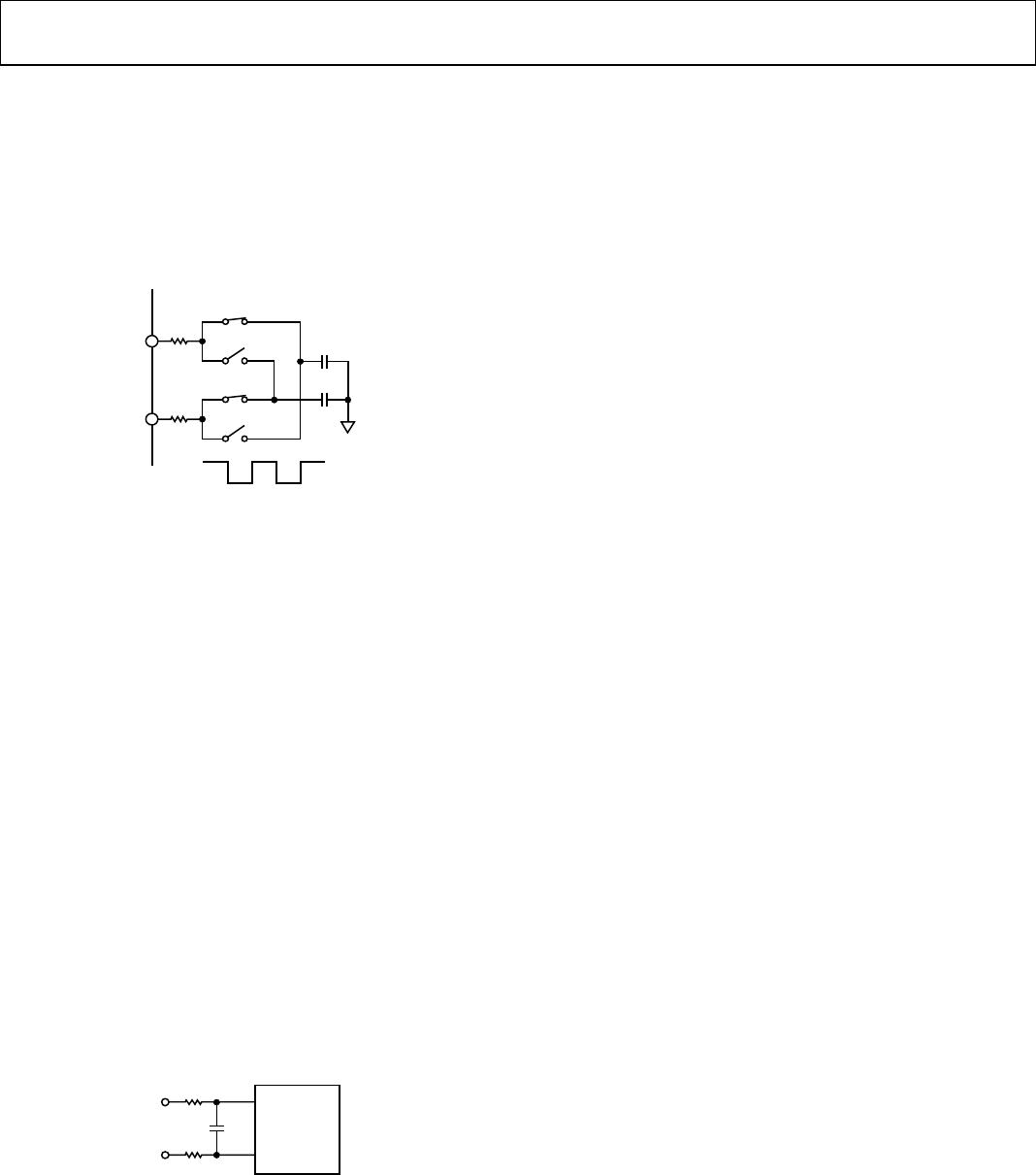

The recommended circuit configuration for driving the differential

inputs to achieve best performance is shown in Figure 23. A

capacitor between the two input pins sources or sinks charge

to allow most of the charge that is needed by one input to be

effectively supplied by the other input. The series resistor again

isolates any op amp from the current spikes created during the

sampling process. Recommended values for the resistors and

capacitor are 22 Ω and 47 pF, respectively.

R

V

IN

–

R

V

IN

+

C

AD7400A

07077-028

Figure 23. Differential Input RC Network

CURRENT SENSING APPLICATIONS

The AD7400A is ideally suited for current sensing applications

where the voltage across a shunt resistor is monitored. The load

current flowing through an external shunt resistor produces a

voltage at the input terminals of the AD7400A. The AD7400A

provides isolation between the analog input from the current

sensing resistor and the digital outputs. By selecting the appropriate

shunt resistor value, a variety of current ranges can be monitored.

Choosing R

SENSE

The shunt resistor values used in conjunction with the AD7400A

are determined by the specific application requirements in terms of

voltage, current, and power. Small resistors minimize power

dissipation, while low inductance resistors prevent any induced

voltage spikes, and good tolerance devices reduce current

variations. The final values chosen are a compromise between

low power dissipation and good accuracy. Low value resistors

have less power dissipated in them, but higher value resistors

may be required to use the full input range of the ADC, thus

achieving maximum SNR performance.

When the peak sense current is known, the voltage range of the

AD7400A (±200 mV) is divided by the maximum sense current

to yield a suitable shunt value. If the power dissipation in the shunt

resistor is too large, the shunt resistor can be reduced, in which

case, less of the ADC input range is used. Using less of the ADC

input range results in performance that is more susceptible to noise

and offset errors because offset errors are fixed and are thus more

significant when smaller input ranges are used.

R

SENSE

must be able to dissipate the I2R power losses. If the power

dissipation rating of the resistor is exceeded, its value may drift

or the resistor may be damaged, resulting in an open circuit.

This can result in a differential voltage across the terminals of

the AD400A in excess of the absolute maximum ratings (see

Table 6.). If I

SENSE

has a large high frequency component, take

care to choose a resistor with low inductance.

VOLTAGE SENSING APPLICATIONS

The AD7400A can also be used for isolated voltage monitoring.

For example, in motor control applications, it can be used to

sense bus voltage. In applications where the voltage being

monitored exceeds the specified analog input range of the

AD7400A, a voltage divider network can be used to reduce

the voltage being monitored to the required range.