Data Sheet AD7400A

Rev. D | Page 17 of 20

APPLICATIONS INFORMATION

GROUNDING AND LAYOUT

Supply decoupling with a value of 100 nF is strongly recom-

mended on both V

DD1

and V

DD2

. Decoupling on one or

both V

DDx

pins does not significantly affect performance. In

applications involving high common-mode transients, ensure

that board coupling across the isolation barrier is minimized.

Furthermore, the board layout should be designed so that

any coupling that occurs equally affects all pins on a given

component side. Failure to ensure this may cause voltage

differentials between pins to exceed the absolute maximum

ratings of the device, thereby leading to latch-up or permanent

damage. Any decoupling used should be placed as close to the

supply pins as possible.

Series resistance in the analog inputs should be minimized to

avoid any distortion effects, especially at high temperatures. If

possible, equalize the source impedance on each analog input to

minimize offset. Beware of mismatch and thermocouple effects

on the analog input PCB tracks to reduce offset drift.

EVALUATING THE AD7400A PERFORMANCE

An AD7400A evaluation board is available with split ground

planes and a board split beneath the AD7400A package to

ensure isolation. This board allows access to each pin on the

device for evaluation purposes.

The evaluation board package includes a fully assembled and

tested evaluation board, documentation, and software for

controlling the board from the PC via the EVA L -CED1Z. The

software also includes a SINC

3

filter implemented on an FPGA.

The evaluation board is used in conjunction with the EVAL-CED1Z

board and can be used as a standalone board. The software

allows the user to perform ac (fast Fourier transform) and dc

(histogram of codes) tests on the AD7400A. The software and

documentation are on a CD that ships with the evaluation board.

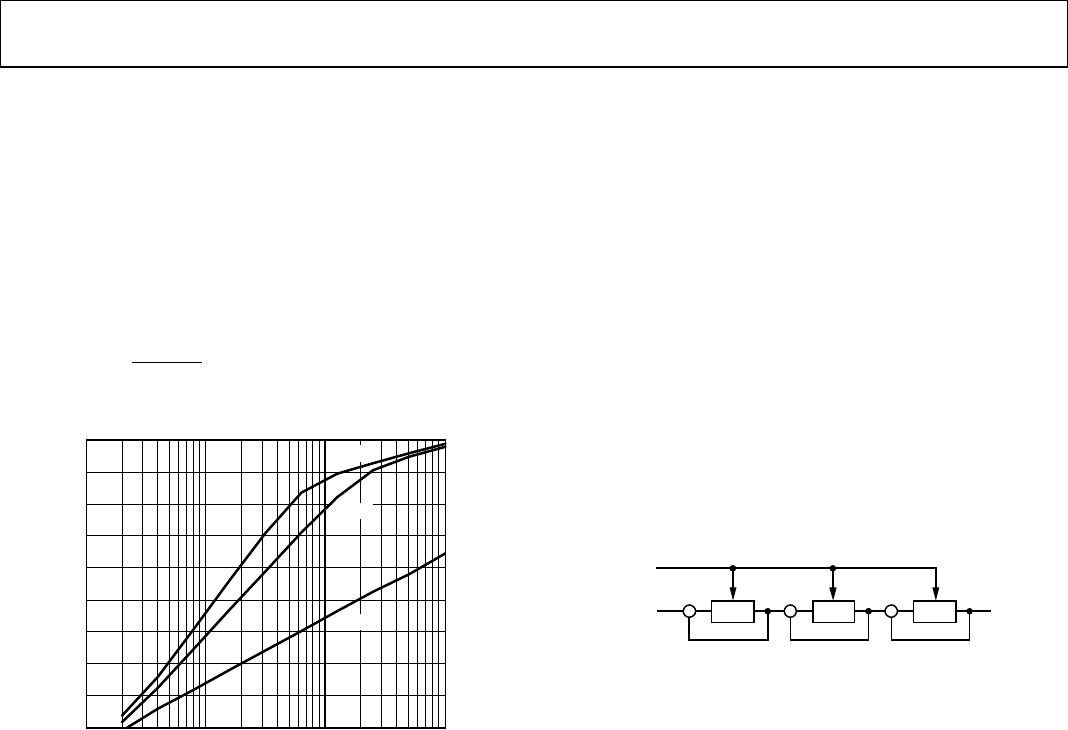

INSULATION LIFETIME

All insulation structures subjected to sufficient time and/or

voltage are vulnerable to breakdown. In addition to the testing

performed by the regulatory agencies, Analog Devices has carried

out an extensive set of evaluations to determine the lifetime of

the insulation structure within the AD7400A.

These tests subjected populations of devices to continuous

cross-isolation voltages. To accelerate the occurrence of failures,

the selected test voltages were values exceeding those of normal

use. The time to failure values of these units were recorded and

used to calculate acceleration factors. These factors were then

used to calculate the time to failure under normal operating

conditions. The values shown in Table 7 are the lesser of the

following two values:

• The value that ensures at least a 50-year lifetime of

continuous use.

• The maximum CSA/VDE approved working voltage.

Note that the lifetime of the AD7400A varies according to

the waveform type imposed across the isolation barrier. The

iCoupler insulation structure is stressed differently depending

on whether the waveform is bipolar ac, unipolar ac, or dc.

Figure 28, Figure 29, and Figure 30 illustrate the different

isolation voltage waveforms.

0V

RATED PEAK VOLTAGE

07077-029

Figure 28. Bipolar AC Waveform

0V

RATED PEAK VOLTAGE

07077-030

Figure 29. Unipolar AC Waveform

0V

RATED PEAK VOLTAGE

07077-031

Figure 30. DC Waveform