DS580F6 11

CS8406

3. GENERAL DESCRIPTION

The CS8406 is a monolithic CMOS device which encodes a nd transmits audio data according to the AES3,

IEC60958, S/PDIF, and EIAJ CP1201 interface standards. The CS8406 accepts audio, channel status and user da-

ta, which is then multiplexed, encoded, and driven onto a cable.

The audio data is input through a configurable, 3-wire input port. The channel status bits and user bit data are input

through an SPI or I²C Mode microcontroller port and may be assembled in separate block sized buffers.

For systems with no microcontroller, a Stand-Alone Mode allows direct access to channel status and user data input

pins.

Target applications include CD-R, DAT, DVD, MD and VTR equipment, mixing consoles, digital audio transmission

equipment, high quality A/D converters, effects processors, set-top TV boxes, and computer audio systems.

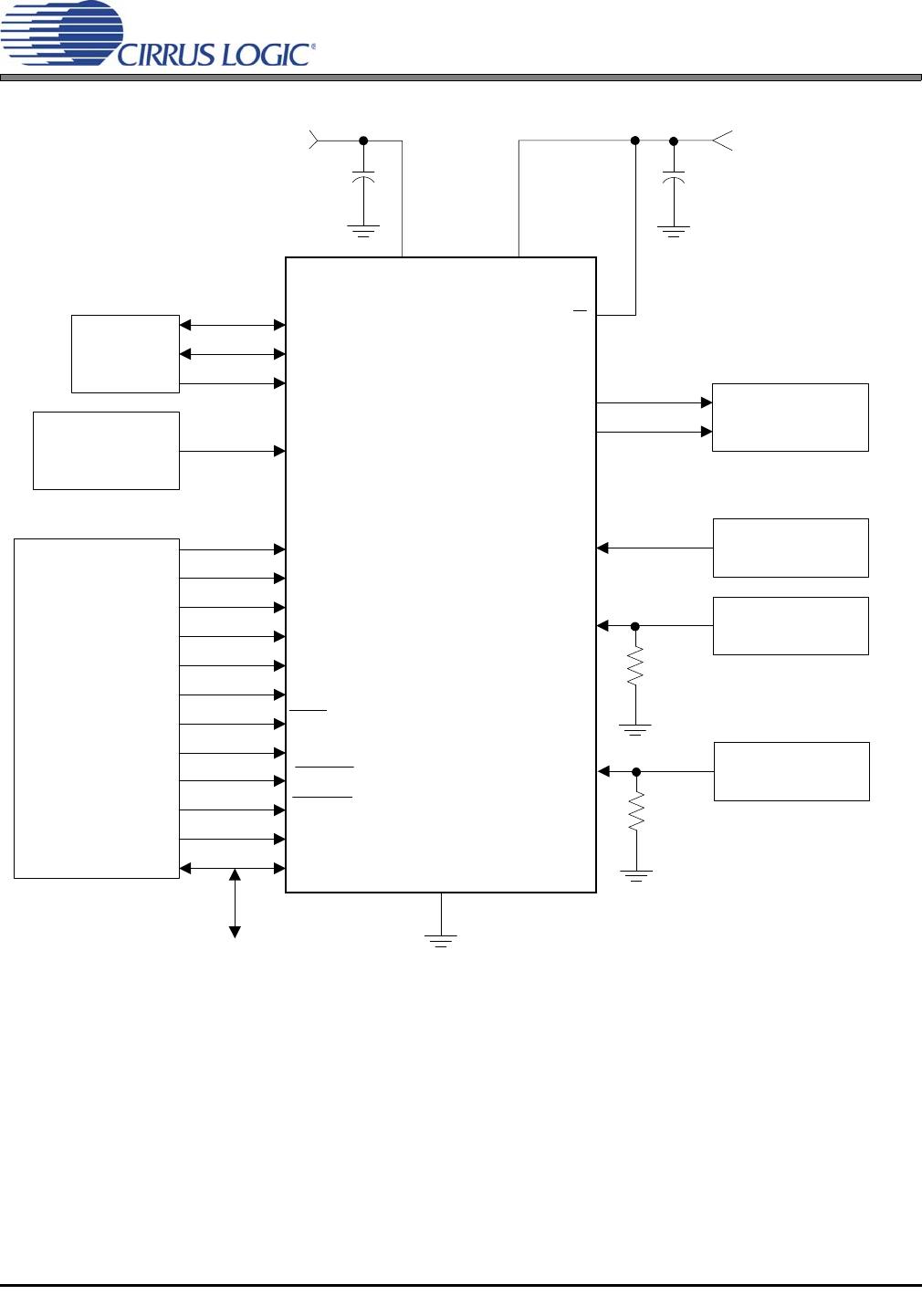

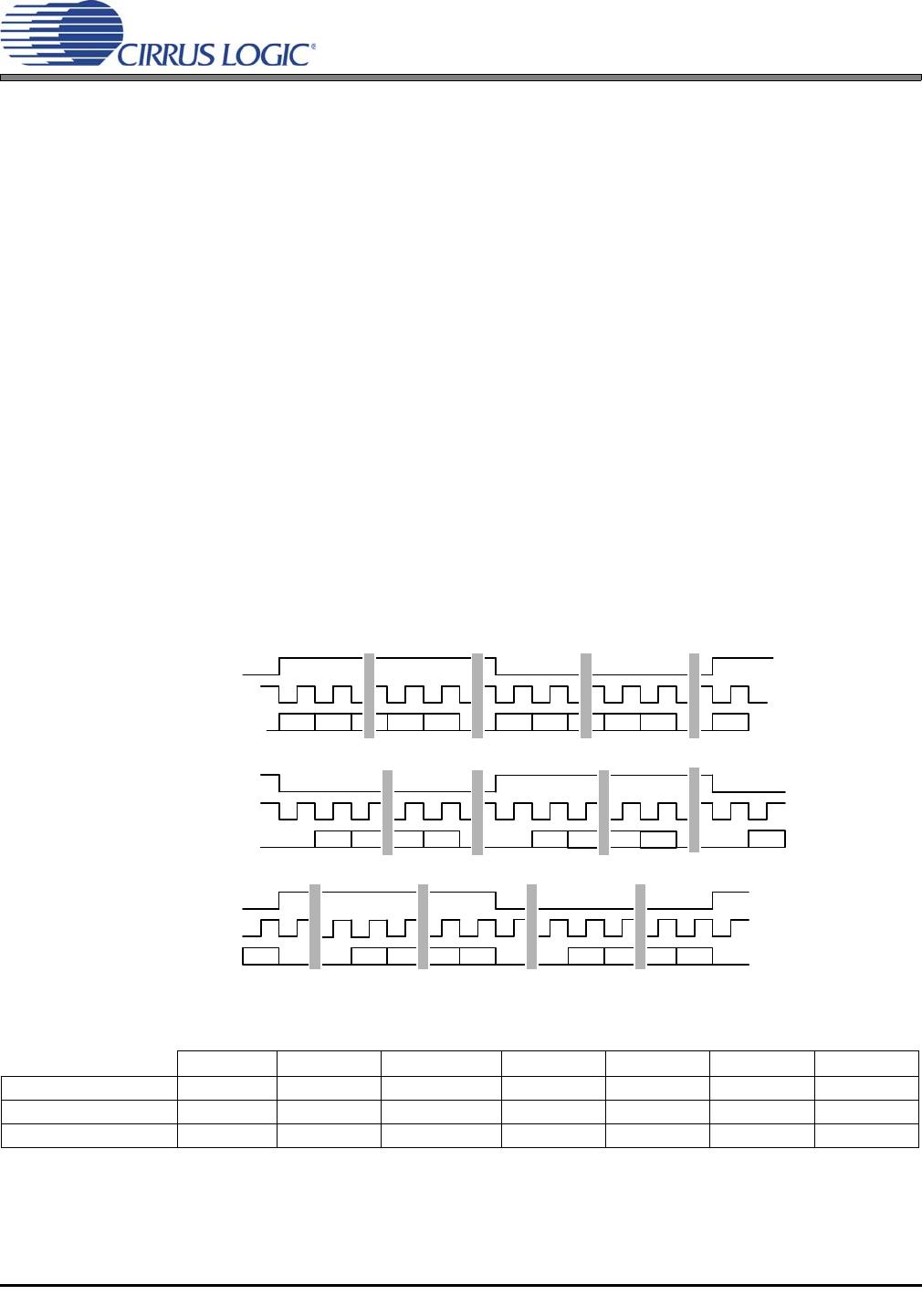

Figure 5 shows the supply and external connections to the CS8406 when configured for operation with a microcon-

troller. Figure 6 shows the supply and external connections to the CS8406 when configured for operation without a

microcontroller.

3.1 AES3 and S/PDIF Standards Documents

This data sheet assumes that the user is familiar with the AES3 and S/PDIF data formats. It is advisable to

have current copies of the AES3 and IEC60958 specifications on hand for easy reference.

The latest AES3 standard is available from the Audio Engi neering Society or ANSI at www.aes.org or

www.ansi.org. Obtain the latest IEC60958 standard from ANSI or from the International Electrotechnical

Commission at www.iec.ch. The latest EIAJ CP-1201 standard is available from the Japanese Electronics

Bureau.

Application Note 22: Overview of Digital Audio Interface Data Structures contains a useful tutorial on digital

audio specifications, but it should not be considered a substitute for the standards.

The paper An Understanding and Implementation of the SCMS Serial Copy Management System for Digital

Audio Transmission, by Clifton Sanchez, is an excellent tutorial on SCMS. It is available from the AES as

reprint 3518.