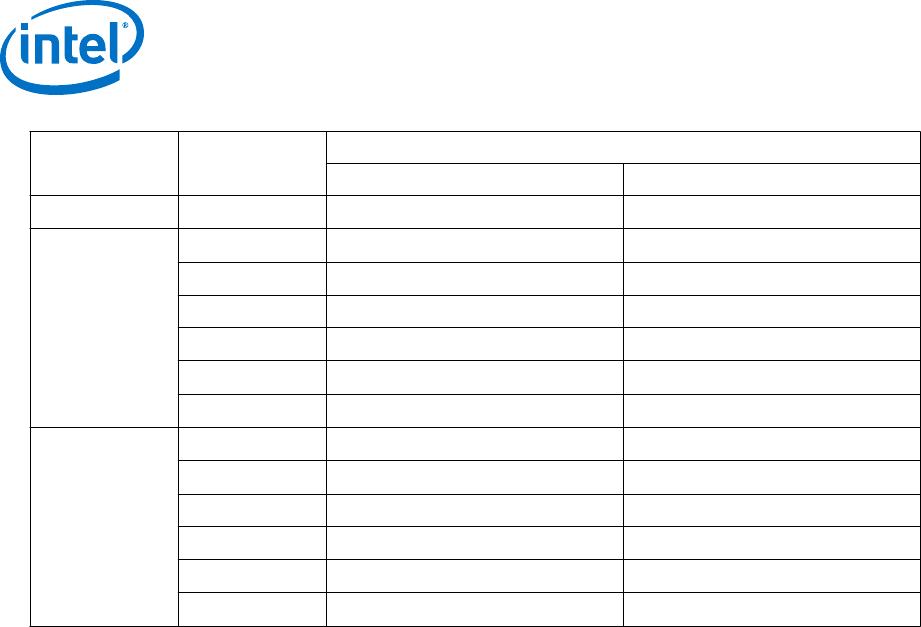

Table 17. Block Protection Bits in EPCQ4A

Status Register Content Memory Content

TB Bit BP2 Bit BP1 Bit BP0 Bit Protected Area Unprotected Area

x 0 0 0 None All sectors

0 0 0 1 Sector 7 Sectors (0 to 6)

0 0 1 0 Sectors (6 to 7) Sectors (0 to 5)

0 0 1 1 Sectors (4 to 7) Sectors (0 to 3)

1 0 0 1 Sector 0 Sectors (1 to 7)

1 0 1 0 Sectors (0 to 1) Sectors (2 to 7)

1 0 1 1 Sectors (0 to 3) Sectors (4 to 7)

x 1 x x All sectors None

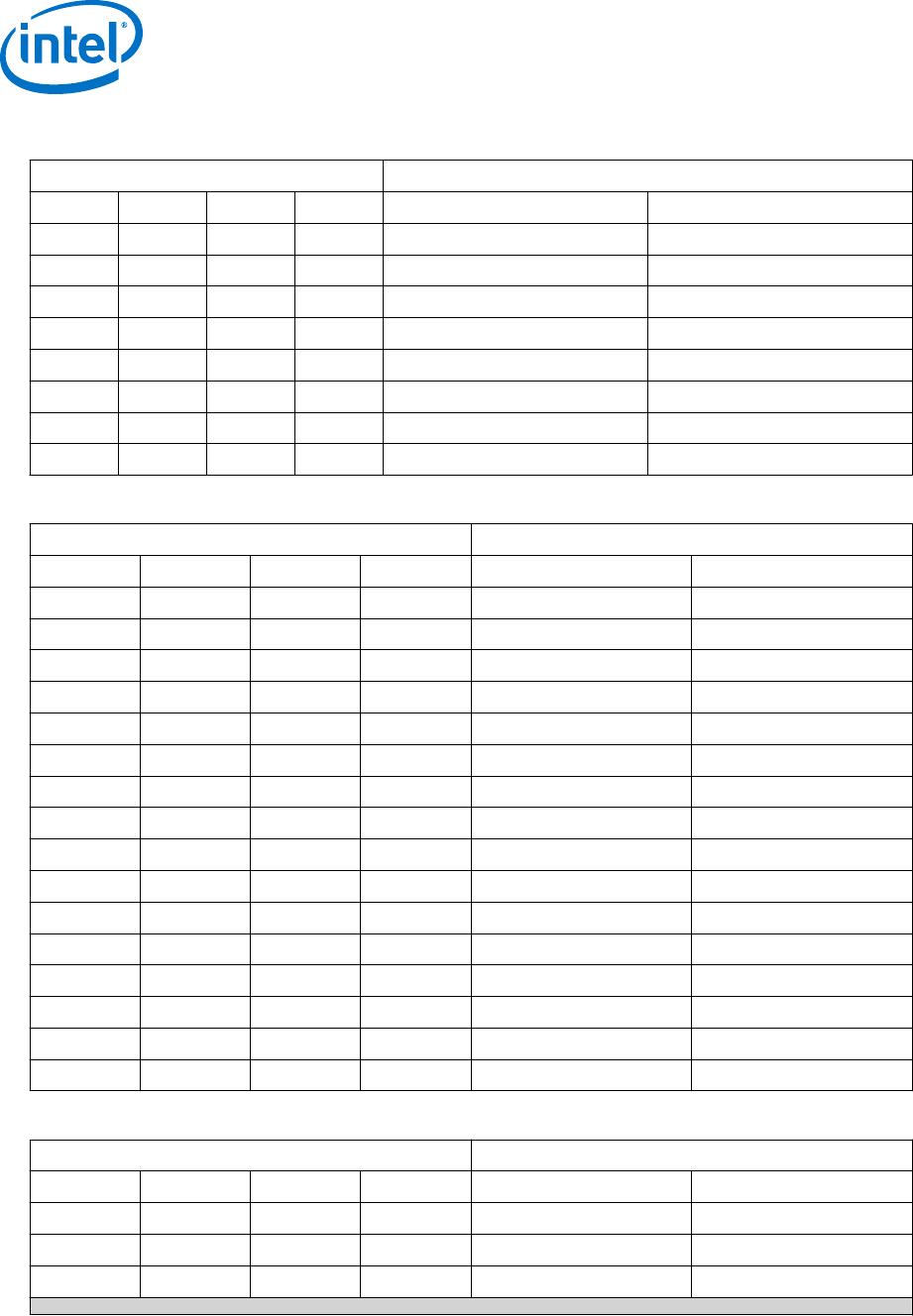

Table 18. Block Protection Bits in EPCQ16A

Status Register Content Memory Content

TB Bit BP2 Bit BP1 Bit BP0 Bit Protected Area Unprotected Area

0 0 0 0 None All sectors

0 0 0 1 Sector 31 Sectors (0 to 30)

0 0 1 0 Sectors (30 to 31) Sectors (0 to 29)

0 0 1 1 Sectors (28 to 31) Sectors (0 to 27)

0 1 0 0 Sectors (24 to 31) Sectors (0 to 23)

0 1 0 1 Sectors (16 to 31) Sectors (0 to 15)

0 1 1 0 All sectors None

0 1 1 1 All sectors None

1 0 0 0 None All sectors

1 0 0 1 Sector 0 Sectors (1 to 31)

1 0 1 0 Sectors (0 to 1) Sectors (2 to 31)

1 0 1 1 Sectors (0 to 3) Sectors (4 to 31)

1 1 0 0 Sectors (0 to 7) Sectors (8 to 31)

1 1 0 1 Sectors (0 to 15) Sectors (16 to 31)

1 1 1 0 All sectors None

1 1 1 1 All sectors None

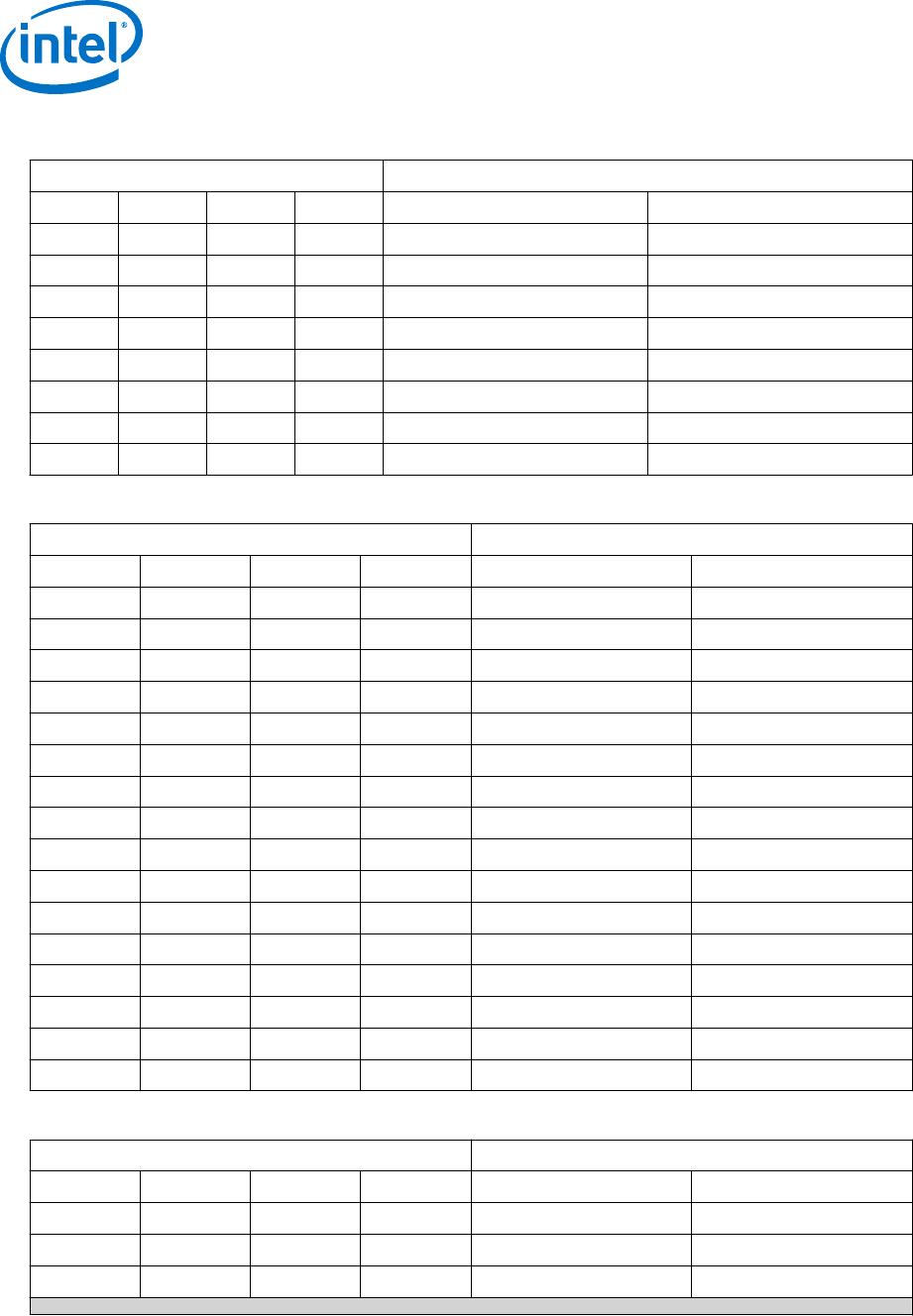

Table 19. Block Protection Bits in EPCQ32A

Status Register Content Memory Content

TB Bit BP2 Bit BP1 Bit BP0 Bit Protected Area Unprotected Area

0 0 0 0 None All sectors

0 0 0 1 Sector 63 Sectors (0 to 62)

0 0 1 0 Sectors (62 to 63) Sectors (0 to 61)

continued...

1. EPCQ-A Serial Configuration Device Datasheet

CF52014 | 2018.04.11

EPCQ-A Serial Configuration Device Datasheet

18