If more than 256 data bytes are shifted into the EPCQ-A device with a write bytes

operation, the previously latched data is discarded and the last 256 bytes are written

to the page. However, if less than 256 data bytes are shifted into the EPCQ-A device,

they are guaranteed to be written at the specified addresses and the other bytes of

the same page are not affected.

The device initiates a self-timed write cycle immediately after the nCS signal is driven

high. For details about the self-timed write cycle time, refer to t

WB

in the related

information below. You must account for this amount of delay before another page of

memory is written. Alternatively, you can check the write in progress bit in the status

register by executing the read status operation while the self-timed write cycle is in

progress. The write in progress bit is set to 1 during the self-timed write cycle and 0

when it is complete.

Note: You must erase all the memory bytes of EPCQ-A devices before you implement the

write bytes operation. You can erase all the memory bytes by executing the erase

sector operation in a sector or the erase bulk operation throughout the entire memory

1.9.10. Quad Input Fast Write Bytes Operation (32h)

This operation is similar to the write bytes operation except that the data are shifted

in on the DATA0, DATA1, DATA2, and DATA3 pins.

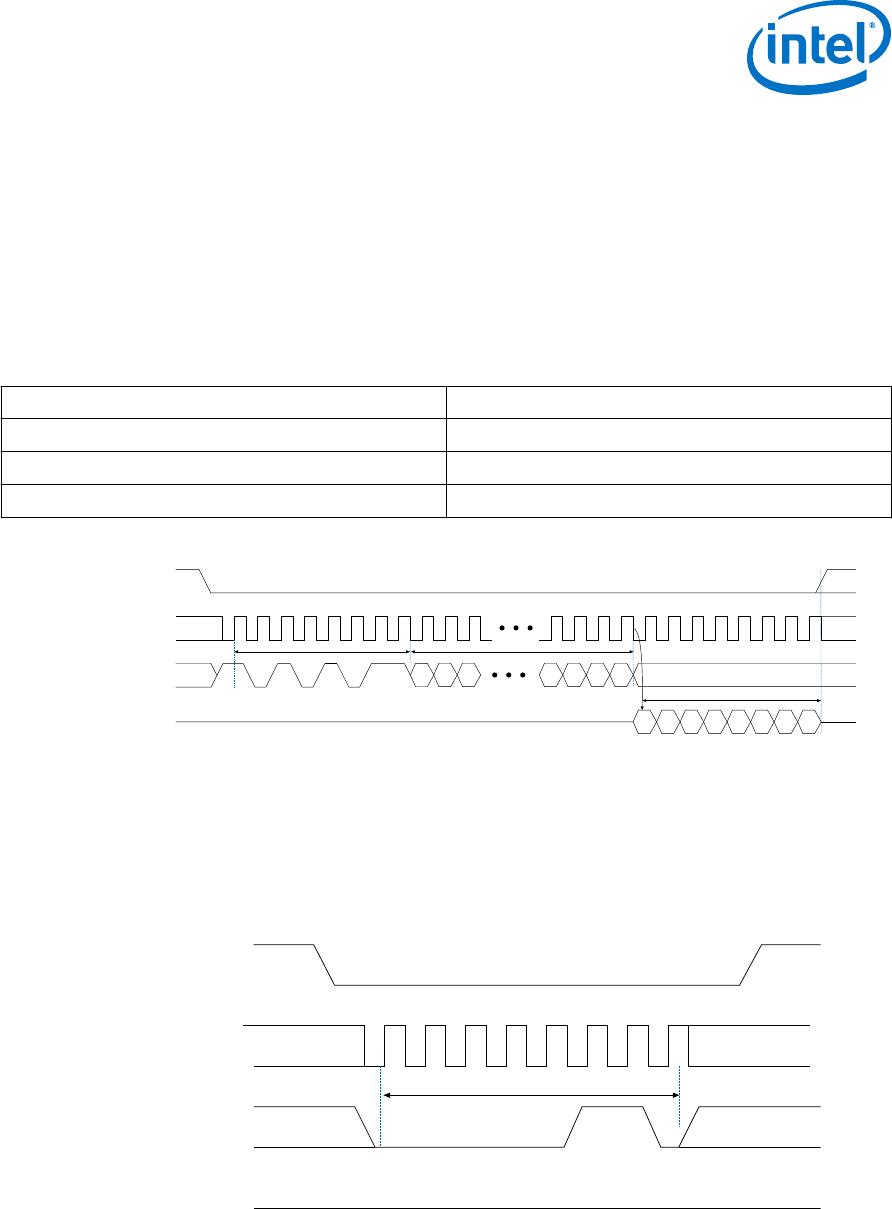

Figure 15. Quad Input Fast Write Bytes Operation Timing Diagram

DATA0

DATA1

nCS

Operation Code (32h)

High Impedance

MSB

DATA2

DATA3

High Impedance

High Impedance

Data In

21 3 9 100

DCLK

3734

35

36

30

31

32

33

39

38

40

42

41

43

MSB

MSBMSB

MSB

MSB

24-bit Address

Data In Data In

2

1 3 4

5

6

44

23 22

21

0 4

1 0

4

0

4

0

4

0

4 40

0 4

0

2 6

6

2

6

2

6

2

6 62

2 6

2

1 5

5

1

5

1

5

1

5 51

1 5

1

3 7

7

3

7

3

7

3

7 73

3 7

3

7

MSB

4

65 7

8

45

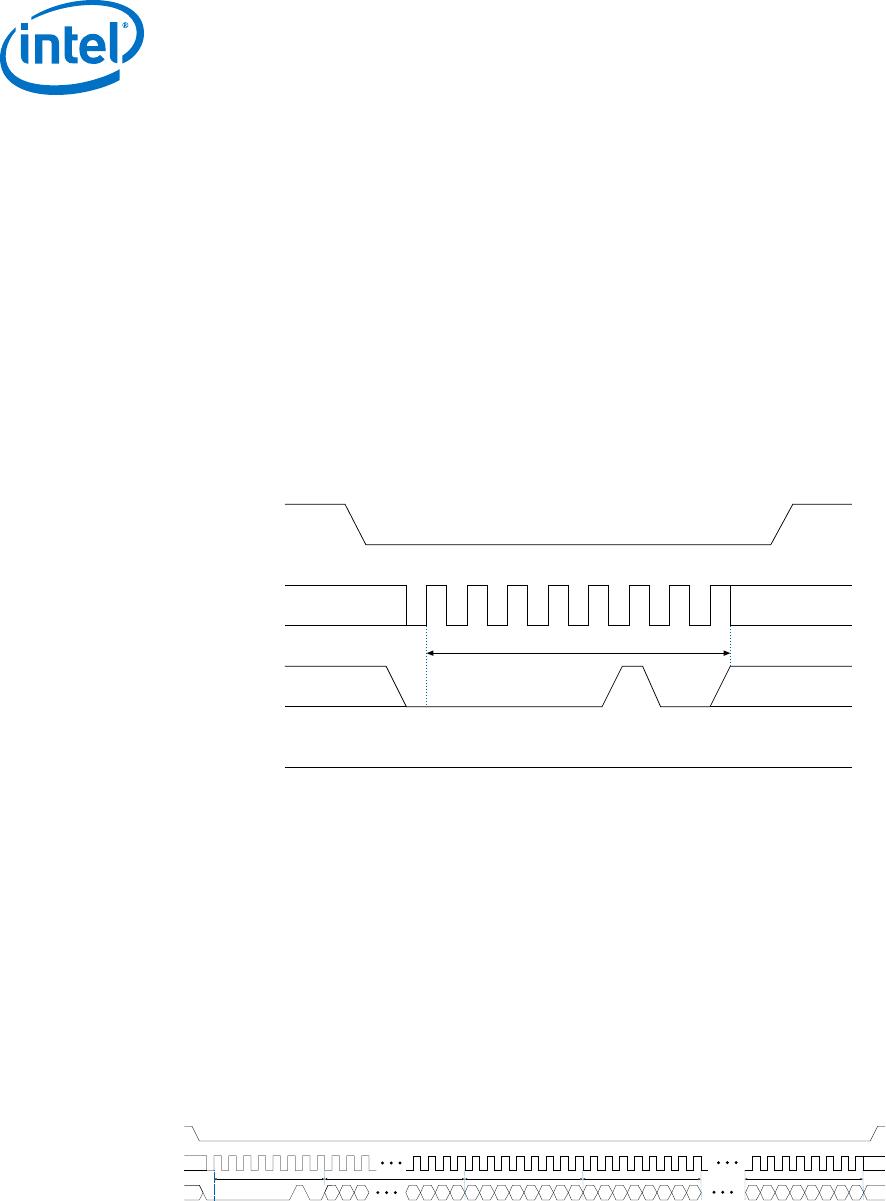

1.9.11. Erase Bulk Operation (C7h)

This operation sets all the memory bits to 1 or 0xFF. Similar to the write bytes

operation, you must execute the write enable operation before the erase bulk

operation.

You can implement the erase bulk operation by driving the nCS signal low and then

shifting in the erase bulk operation code on the DATA0 pin. The nCS signal must be

driven high after the eighth bit of the erase bulk operation code has been latched in.

1. EPCQ-A Serial Configuration Device Datasheet

CF52014 | 2018.04.11

EPCQ-A Serial Configuration Device Datasheet

27