PCA8561 All information provided in this document is subject to legal disclaimers. © NXP Semiconductors N.V. 2015. All rights reserved.

Product data sheet Rev. 4 — 27 March 2015 11 of 55

NXP Semiconductors

PCA8561

Automotive 18 × 4 LCD segment driver

Remark: The internal POR can be disabled by connecting pin PORE to V

SS

. In this case,

the internal registers are not defined and require a hardware reset according to

Section 8.3.3

or a software reset, see Section 8.3.4.

8.3.3 Hardware reset: RST pin

At power-on the PCA8561 can be reset to the following starting conditions by pulling pin

RST

low:

• All backplane and segment outputs are set to V

SS

• The selected drive mode is: 1:4 multiplex with

1

⁄

3

bias

• Blinking is switched off

• The bus interface is initialized

• The address pointer is cleared (set to logic 0)

• The display and the internal oscillator are disabled

• The display registers are set to logic 0

Remark: The hardware reset overrides the POR see Section 8.3.2

.

8.3.4 Command: Software_reset

The internal registers including the display registers and the address pointer (set to

logic 0) of the device are reset by the Software_reset command.

[1] Default value.

8.4 Display data register mapping

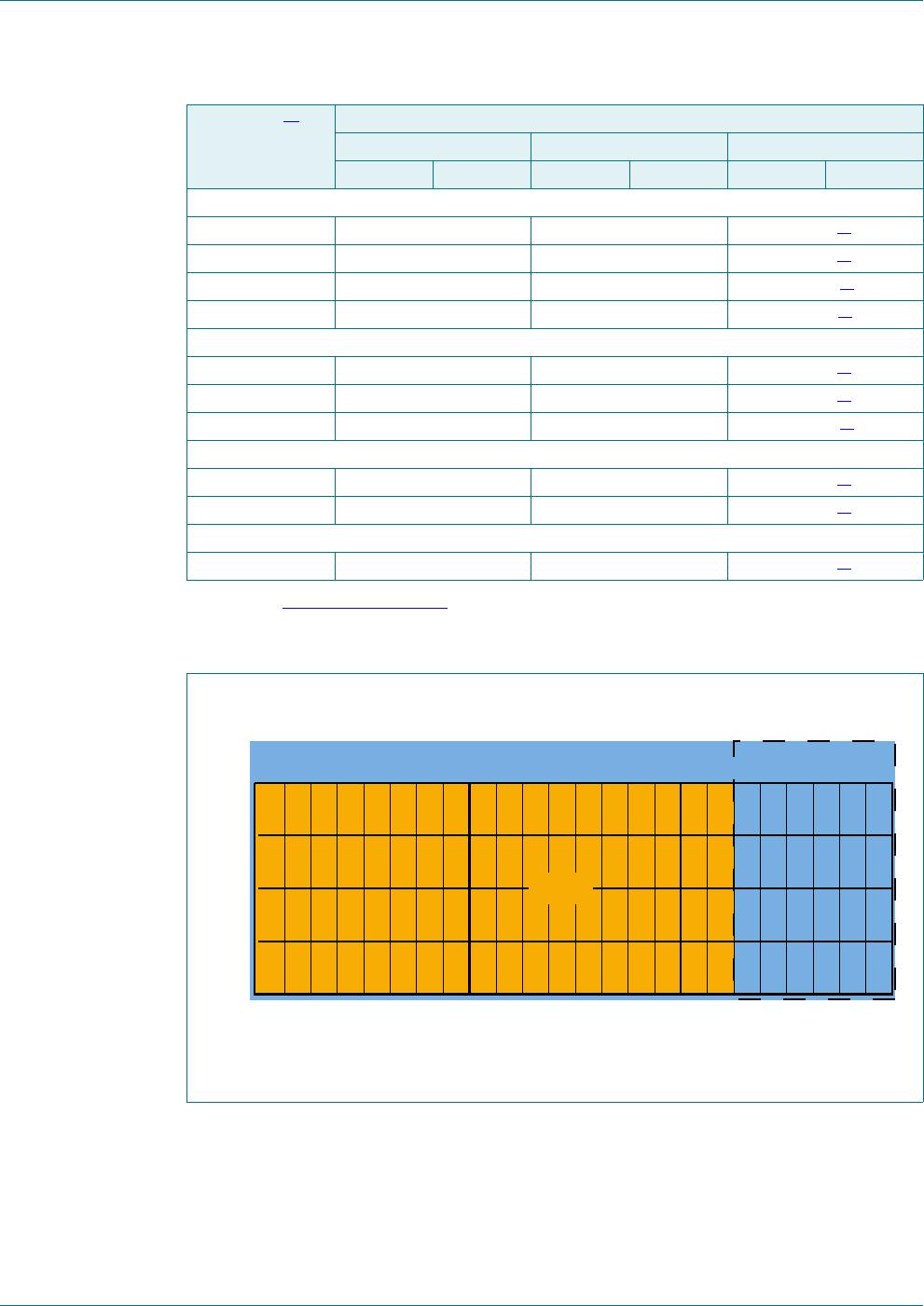

The example in Table 10 and Figure 7 illustrates the segment and backplane mapping of

the display in relation to the display RAM.

For example, in 1:4 multiplex drive mode, the backplanes are served by signals COM0 to

COM3 and the segments are driven by signals SEG0 to SEG17. Contents of addresses

04h to 06h are allocated to the first row (COM0) starting with the LSB driving the leftmost

element and moving forward to the right with increasing bit position. If a bit is logic 0, the

element is off, if it is logic 1 the element is turned on. All register content is LSB to MSB

left to right. Addresses 07h to 09h serve COM1 signals, addresses 0Ah to 0Ch serve

COM2 signals, and addresses 0Dh to 0Fh serve COM3 signals.

For displays with fewer segments/elements the unused bits are ignored.

Table 9. Software_reset - software reset command register (address 00h) bit description

This register can only be written but not read.

Bit Symbol Value Description

7 to 0 SR[7:0] software reset

00000000

[1]

no reset

00101100 software reset