AD9512-EP Enhanced Product

Rev. 0 | Page 4 of 20

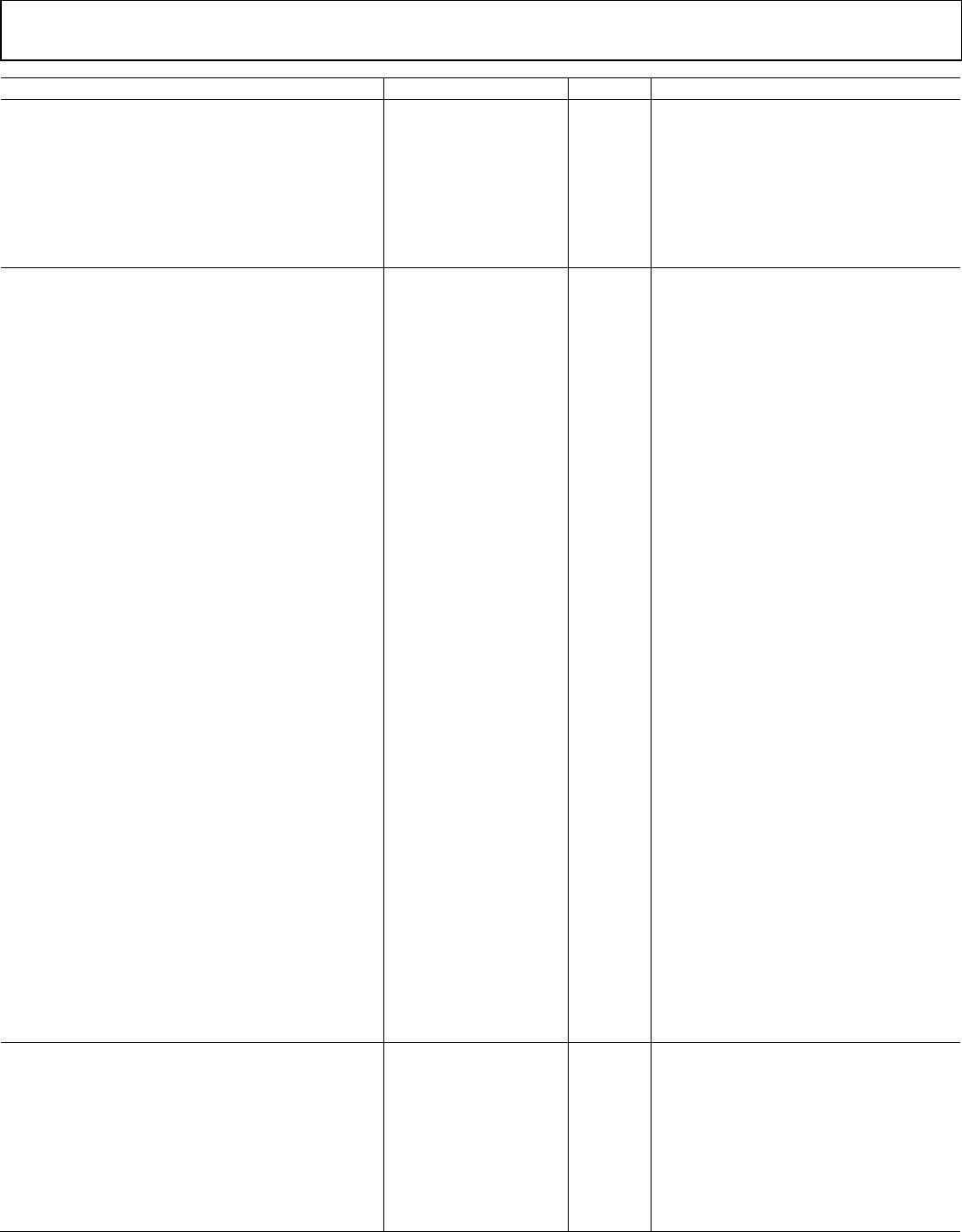

TIMING CHARACTERISTICS

Table 3.

Parameter Min Typ Max Unit Test Conditions/Comments

S

Output level 0x3D (0x3E) (0x3F)[3:2] = 10b

Output Rise Time, t

RP

130 180 ps 20% to 80%, measured differentially

Output Fall Time, t

FP

130 180 ps 80% to 20%, measured differentially

PROPAGATION DELAY, t

PECL

, CLK-TO-LVPECL OUT

1

Divide = Bypass 320 490 635 ps At full temperature range

335 490 635 ps At −40°C to +85°C

Divide = 2 to 32 360 545 695 ps At full temperature range

375 545 695 ps At −40°C to +85°C

Variation with Temperature 0.5 ps/°C

OUTPUT SKEW, LVPECL OUTPUTS

OUT1 to OUT0 on Same Part, t

SKP

2

OUT1 to OUT2 on Same Part, t

SKP

2

15 45 80 ps

OUT0 to OUT2 on Same Part, t

SKP

2

45 65 90 Ps

All LVPECL OUT Across Multiple Parts, t

SKP_AB

3

275 ps

Same LVPECL OUT Across Multiple Parts, t

SKP_AB

3

130 ps

LVDS Termination = 100 Ω differential

Output level 0x40 (0x41) [2:1] = 01b

3.5 mA termination current

Output Rise Time, t

RL

200 350 ps 20% to 80%, measured differentially

Output Fall Time, t

FL

210 350 ps 80% to 20%, measured differentially

PROPAGATION DELAY, t

LVDS

, CLK-TO-LVDS OUT

1

OUT3 to OUT4

Divide = Bypass 0.97 1.33 1.59 ns At full temperature range

0.99 1.33 1.59 ns At −40°C to +85°C

Divide = 2 to 32 1.02 1.38 1.64 ns At full temperature range

1.04 1.38 1.64 ns At −40°C to +85°C

Variation with Temperature

OUTPUT SKEW, LVDS OUTPUTS

OUT3 to OUT4 on Same Part, t

SKV

2

−85 +270 ps

All LVDS OUTs Across Multiple Parts, t

SKV_AB

3

450 ps

Same LVDS OUT Across Multiple Parts, t

SKV_AB

3

325 ps

CMOS B outputs are inverted; termination = open

Output Rise Time, t

RC

681 865 ps 20% to 80%; C

LOAD

= 3 pF

Output Fall Time, t

FC

646 992 ps 80% to 20%; C

LOAD

= 3 pF

PROPAGATION DELAY, t

CMOS

, CLK-TO-CMOS OUT

1

Divide = Bypass 1.0 1.39 1.71 ns At full temperature range

1.02 1.39 1.71 ns At −40°C to +85°C

Divide = 2 to 32 1.05 1.44 1.76 ns At full temperature range

1.07 1.44 1.76 ns At −40°C to +85°C

Variation with Temperature 1 ps/°C

OUTPUT SKEW, CMOS OUTPUTS

OUT3 to OUT4 on Same Part, t

SKC

2

−140 +145 +300 ps

All CMOS OUT Across Multiple Parts, t

SKC_AB

3

650 ps

Same CMOS OUT Across Multiple Parts, t

SKC_AB

3

500 ps

LVPECL-TO-LVDS OUT Everything the same; different logic type

Output Skew, t

SKP_V

0.73 0.92 1.14 ns LVPECL to LVDS on same part

LVPECL-TO-CMOS OUT Everything the same; different logic type

Output Skew, t

SKP_C

0.87 1.14 1.43 ns LVPECL to CMOS on same part