Enhanced Product AD9512-EP

Rev. 0 | Page 7 of 20

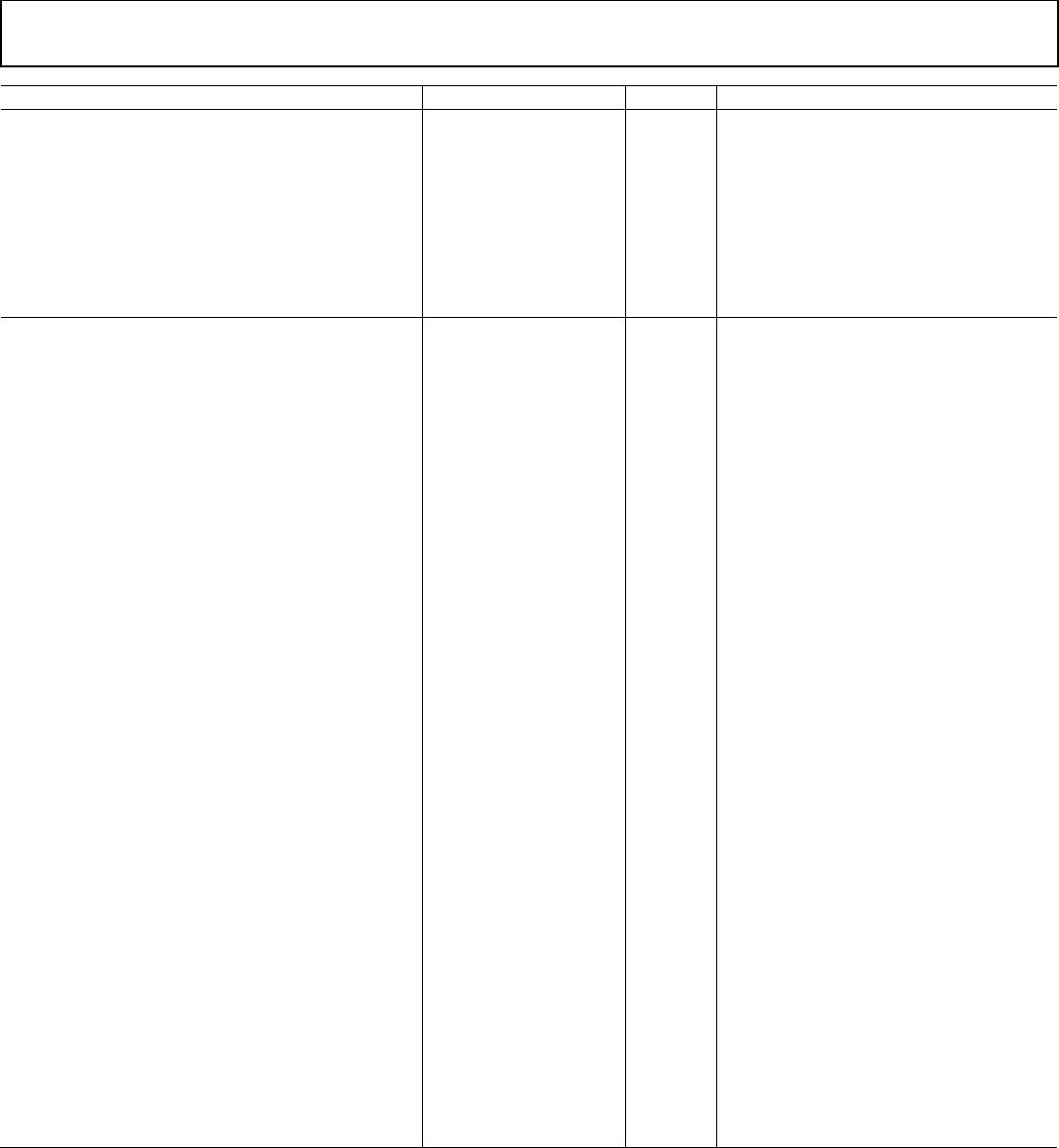

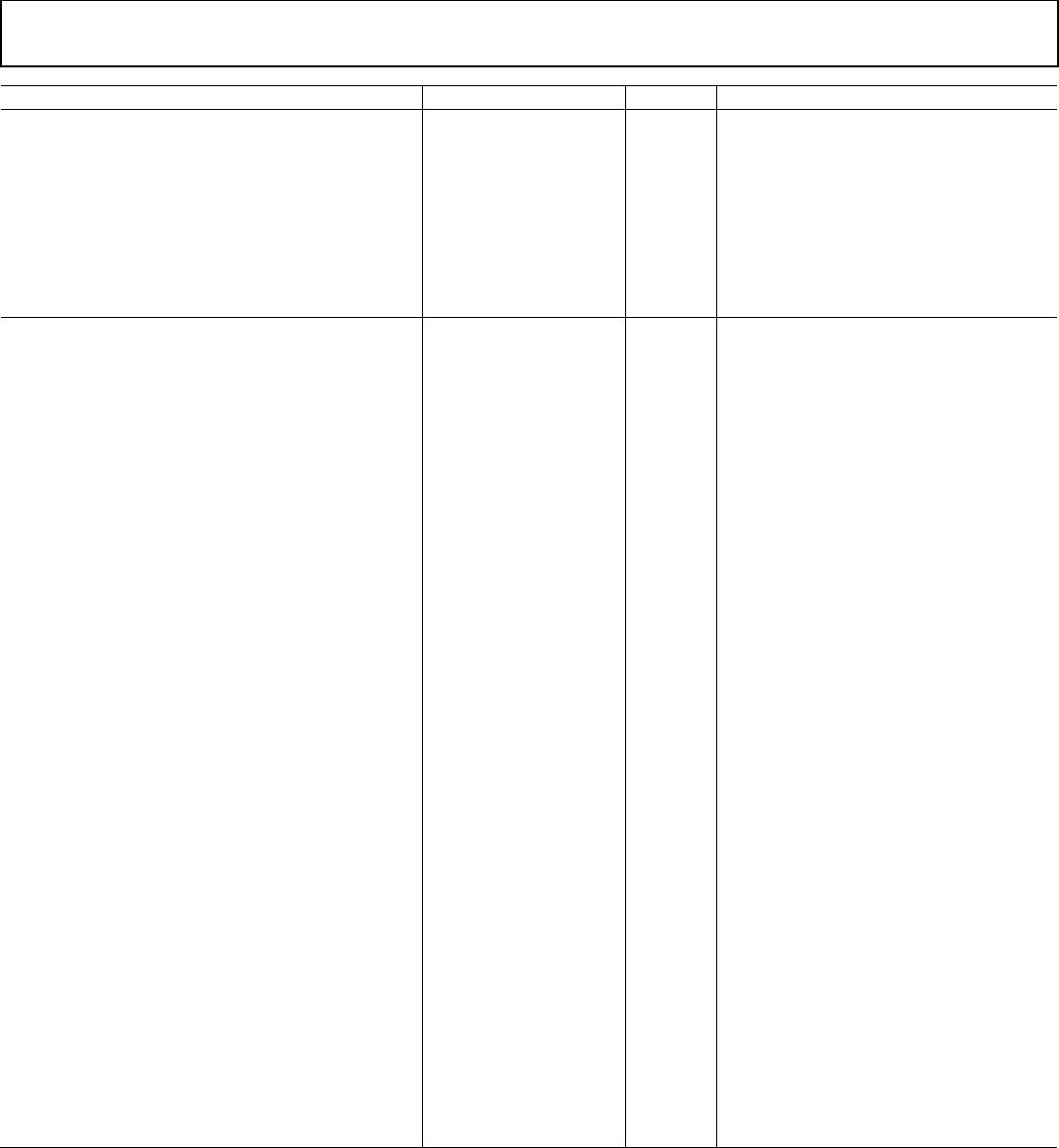

Parameter Min Typ Max Unit Test Conditions/Comments

CLK1 = 245.76 MHz, OUT = 122.88 MHz

Divide Ratio = 2

@ 10 Hz Offset −118 dBc/Hz

@ 100 Hz Offset −127 dBc/Hz

@ 1 kHz Offset −137 dBc/Hz

@ 10 kHz Offset −147 dBc/Hz

@ 100 kHz Offset −154 dBc/Hz

>10 MHz Offset −158 dBc/Hz

CLK1-TO-CMOS ADDITIVE PHASE NOISE

CLK1 = 245.76 MHz, OUT = 245.76 MHz

Divide Ratio = 1

@ 10 Hz Offset −110 dBc/Hz

@ 100 Hz Offset −121 dBc/Hz

@ 1 kHz Offset −130 dBc/Hz

@ 10 kHz Offset −140 dBc/Hz

@ 1 MHz Offset −149 dBc/Hz

> 10 MHz Offset −156 dBc/Hz

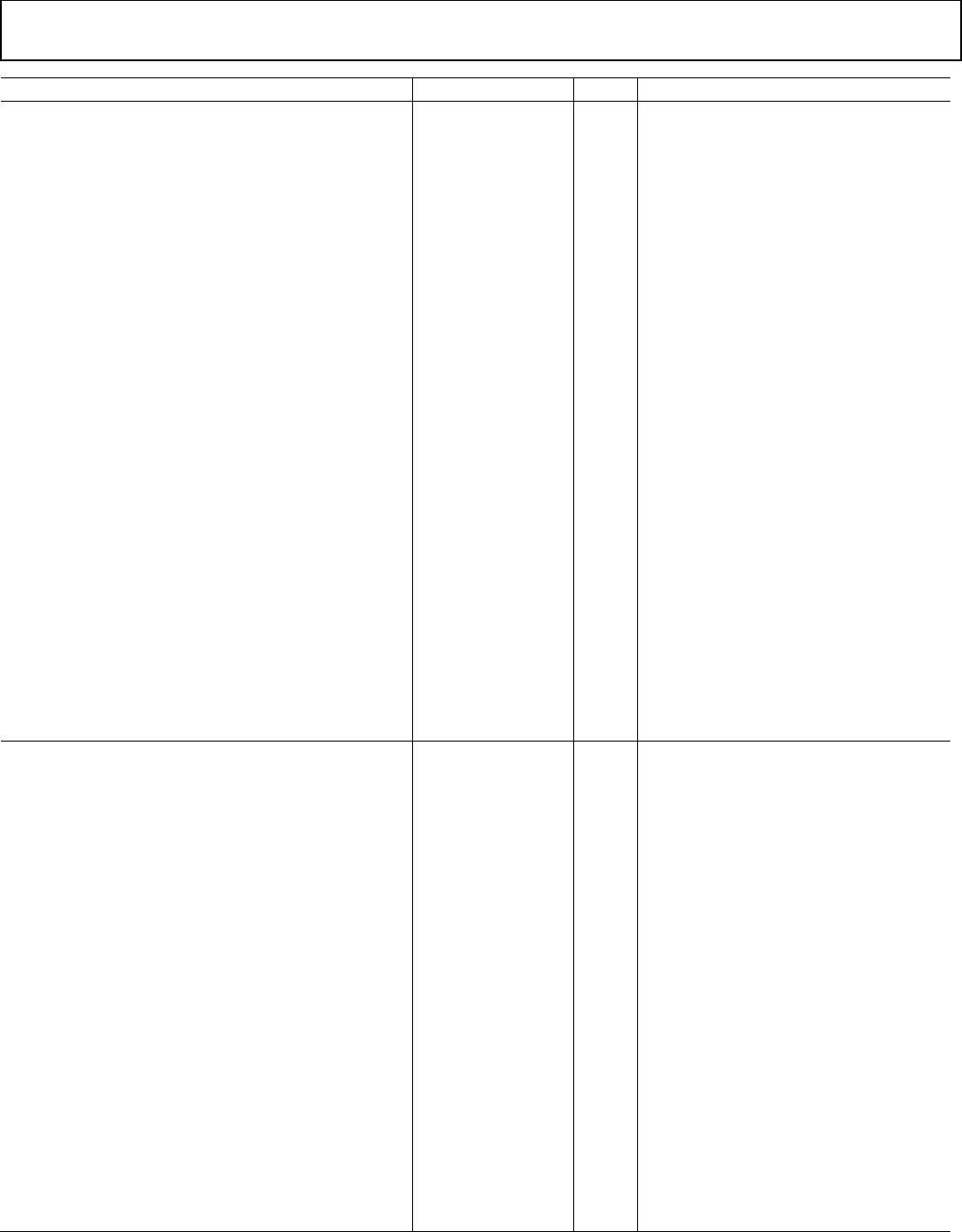

CLK1 = 245.76 MHz, OUT = 61.44 MHz

Divide Ratio = 4

@ 10 Hz Offset −122 dBc/Hz

@ 100 Hz Offset −132 dBc/Hz

@ 1 kHz Offset −143 dBc/Hz

@ 10 kHz Offset −152 dBc/Hz

@ 100 kHz Offset −158 dBc/Hz

@ 1 MHz Offset −160 dBc/Hz

>10 MHz Offset −162 dBc/Hz

CLK1 = 78.6432 MHz, OUT = 78.6432 MHz

@ 10 Hz Offset −122 dBc/Hz

@ 100 Hz Offset −132 dBc/Hz

@ 1 kHz Offset −140 dBc/Hz

@ 10 kHz Offset −150 dBc/Hz

@ 1 MHz Offset −158 dBc/Hz

>10 MHz Offset −160 dBc/Hz

CLK1 = 78.6432 MHz, OUT = 39.3216 MHz

Divide Ratio = 2

@ 10 Hz Offset −128 dBc/Hz

@ 100 Hz Offset −136 dBc/Hz

@ 1 kHz Offset −146 dBc/Hz

@ 10 kHz Offset −155 dBc/Hz

@ 100 kHz Offset −161 dBc/Hz

>1 MHz Offset −162 dBc/Hz