DS2780 Standalone Fuel Gauge IC

24 of 31

TRANSACTION SEQUENCE

The protocol for accessing the DS2780 through the 1-Wire port is as follows:

Initialization

Net Address Command

Function Command

Transaction/Data

The sections that follow describe each of these steps in detail.

All transactions of the 1-Wire bus begin with an initialization sequence consisting of a reset pulse transmitted by the

bus master followed by a presence pulse simultaneously transmitted by the DS2780 and any other slaves on the

bus. The presence pulse tells the bus master that one or more devices are on the bus and ready to operate. For

more details, see the 1-Wire Signaling section.

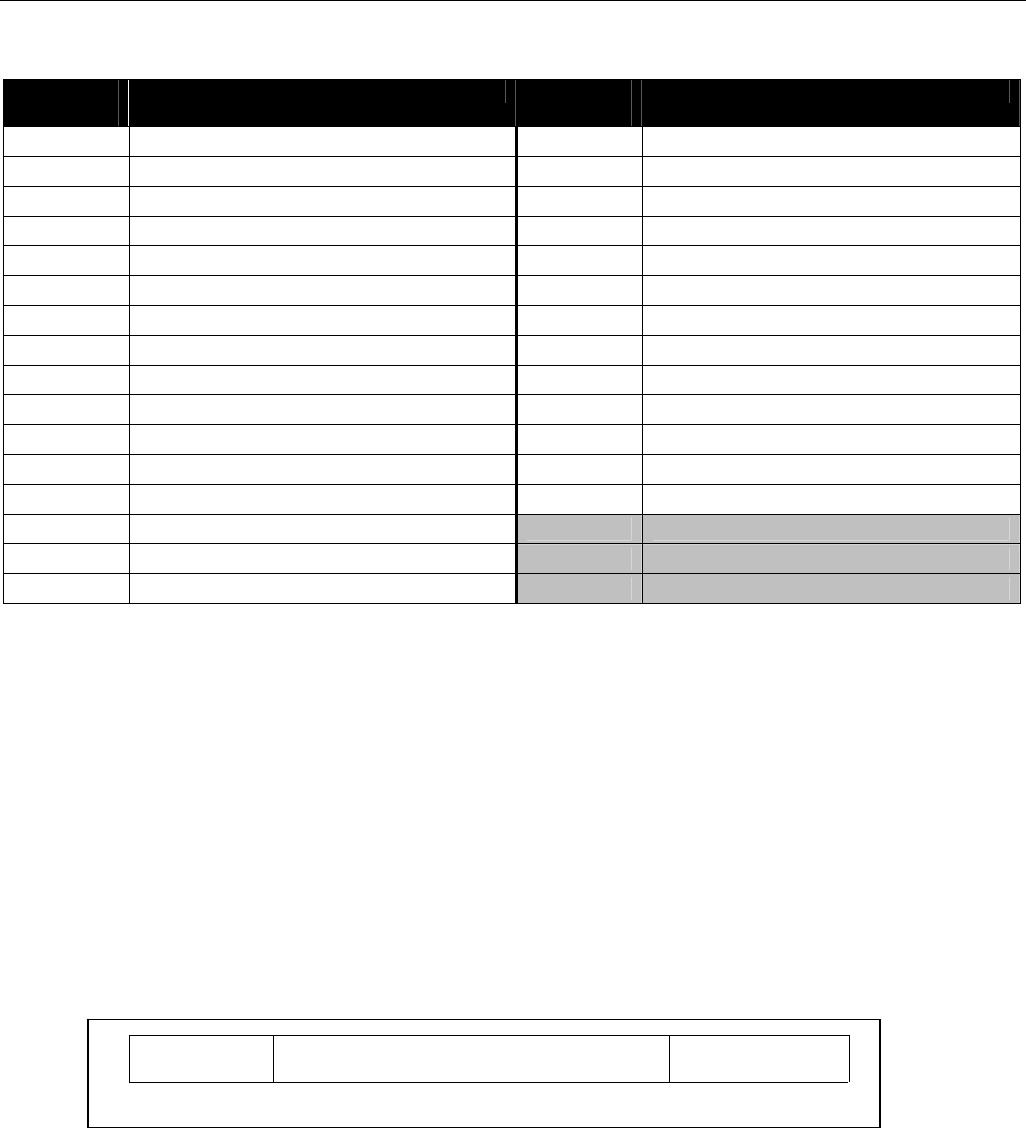

NET ADDRESS COMMANDS

Once the bus master has detected the presence of one or more slaves, it can issue one of the net address

commands described in the following paragraphs. The name of each ROM command is followed by the 8-bit

opcode for that command in square brackets. Figure 21 presents a transaction flowchart of the net address

commands.

Read Net Address [33h or 39h]. This command allows the bus master to read the DS2780’s 1-Wire net address.

This command can only be used if there is a single slave on the bus. If more than one slave is present, a data

collision occurs when all slaves try to transmit at the same time (open drain produces a wired-AND result). The

RNAOP bit in the status register selects the opcode for this command, with RNAOP = 0 indicating 33h, and

RNAOP = 1 indicating 39h.

Match Net Address [55h]. This command allows the bus master to specifically address one DS2780 on the 1-Wire

bus. Only the addressed DS2780 responds to any subsequent function command. All other slave devices ignore

the function command and wait for a reset pulse. This command can be used with one or more slave devices on

the bus.

Skip Net Address [CCh]. This command saves time when there is only one DS2780 on the bus by allowing the

bus master to issue a function command without specifying the address of the slave. If more than one slave device

is present on the bus, a subsequent function command can cause a data collision when all slaves transmit data at

the same time.

Search Net Address [F0h]. This command allows the bus master to use a process of elimination to identify the 1-

Wire net addresses of all slave devices on the bus. The search process involves the repetition of a simple three-

step routine: read a bit, read the complement of the bit, then write the desired value of that bit. The bus master

performs this simple three-step routine on each bit location of the net address. After one complete pass through all

64 bits, the bus master knows the address of one device. The remaining devices can then be identified on

additional iterations of the process. See Chapter 5 of the Book of DS19xx i

Button

®

Standards for a comprehensive

discussion of a net address search, including an actual example. (This publication can be found on the

Maxim/Dallas Semiconductor website at www.maxim-ic.com.)

Resume [A5h]. This command increases data throughput in multidrop environments where the DS2780 needs to

be accessed several times. Resume is similar to the Skip Net Address command in that the 64-bit net address

does not have to be transmitted each time the DS2780 is accessed. After successfully executing a Match Net

Address command or Search Net Address command, an internal flag is set in the DS2780. When the flag is set,

the DS2780 can be repeatedly accessed through the Resume command function. Accessing another device on the

bus clears the flag, thus preventing two or more devices from simultaneously responding to the Resume command

function.

iButton is a registered trademark of Maxim Integrated Products, Inc.