IDT 89HPES24NT24G2 Datasheet

10 of 35 December 17, 2013

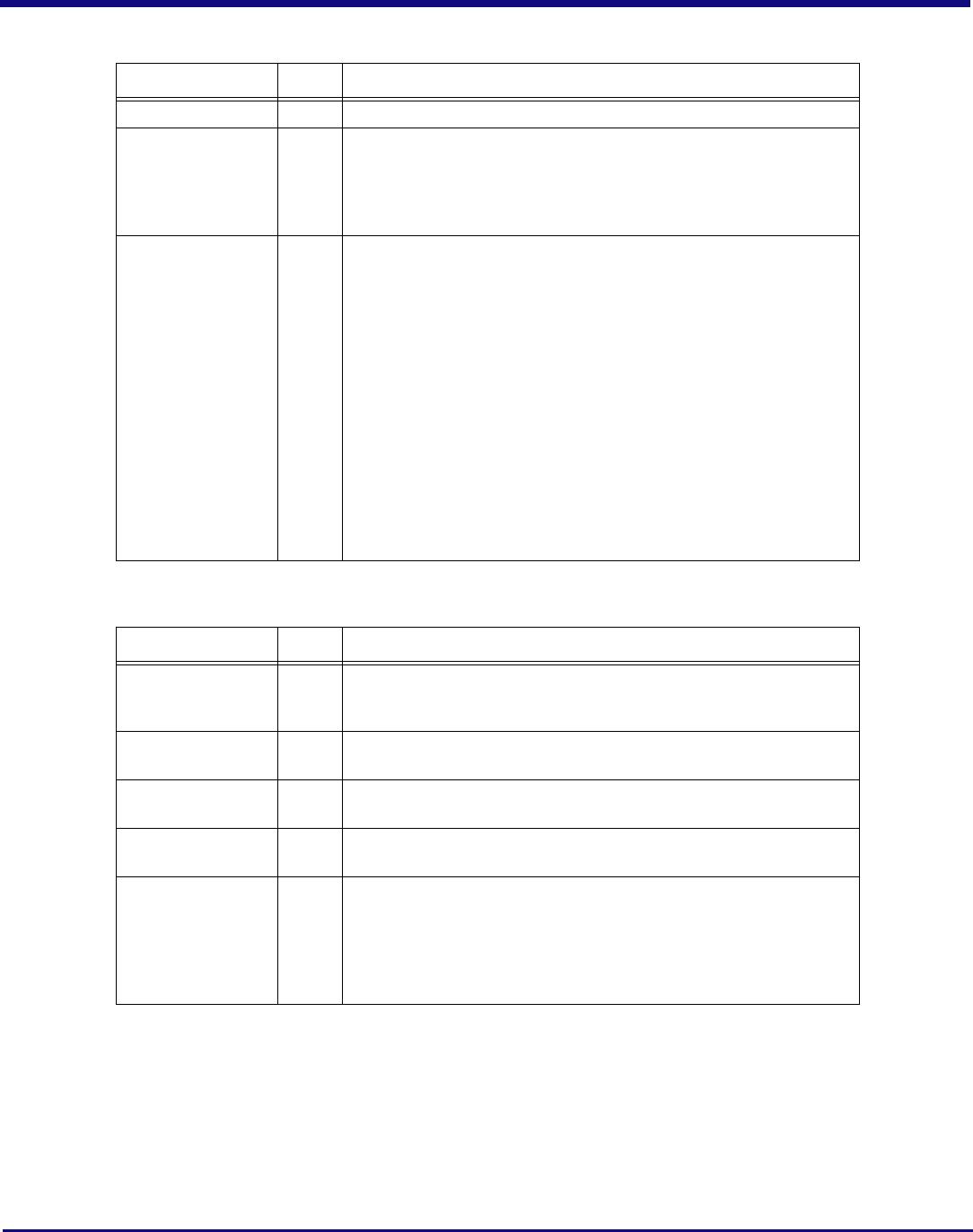

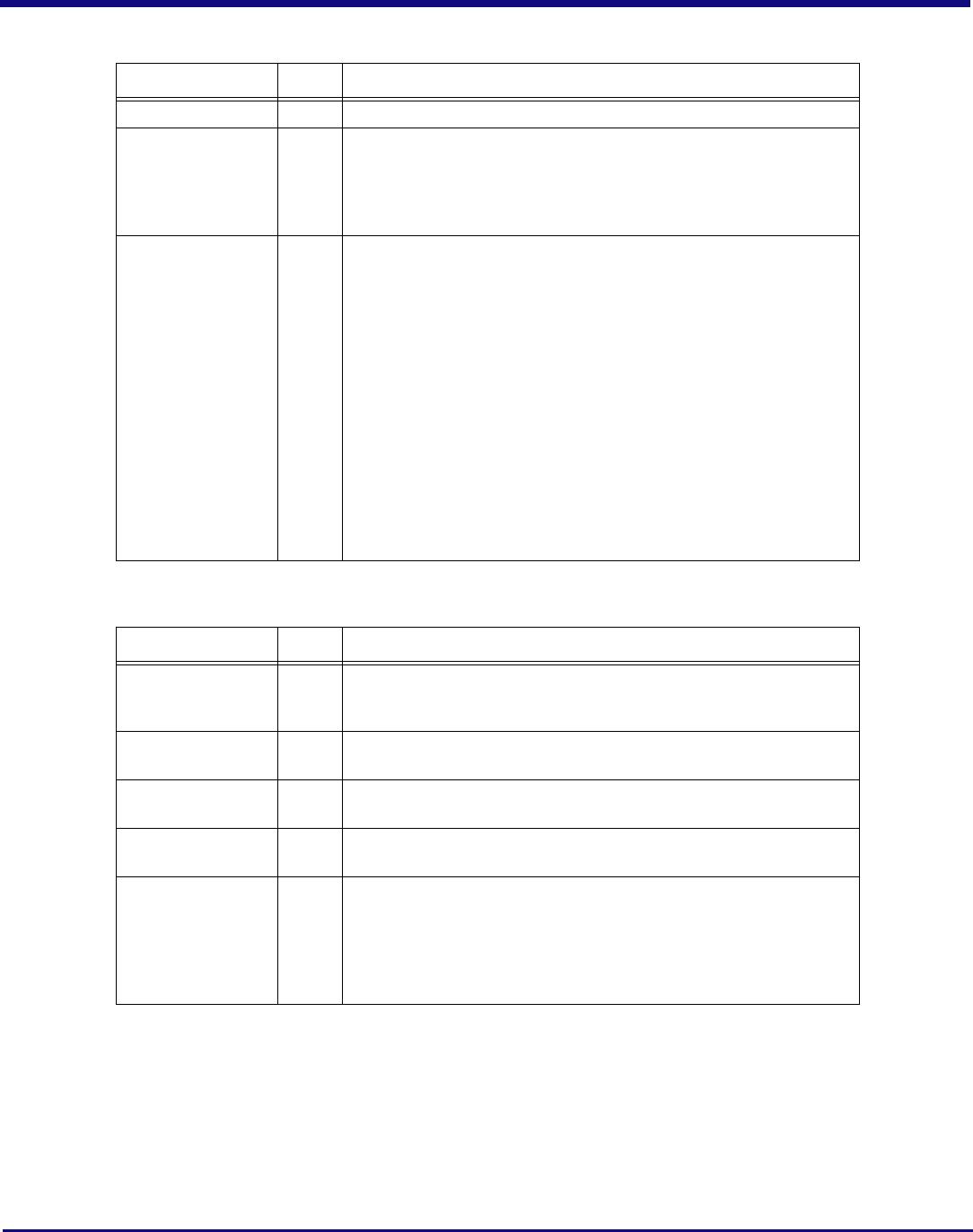

PERSTN I Fundamental Reset. Assertion of this signal resets all logic inside the device.

RSTHALT I Reset Halt. When this signal is asserted during a switch fundamental reset sequence,

the switch remains in a quasi-reset state with the Master and Slave SMBuses active.

This allows software to read and write registers internal to the device before normal

device operation begins. The device exits the quasi-reset state when the RSTHALT bit

is cleared in the SWCTL register by an SMBus master.

SWMODE[3:0] I Switch Mode. These configuration pins determine the switch operating mode.

These pins should be static and not change following the negation of PERSTN.

0x0 - Single partition

0x1 - Single partition with Serial EEPROM initialization

0x2 - Single partition with Serial EEPROM Jump 0 initialization

0x3 - Single partition with Serial EEPROM Jump 1 initialization

0x4 through 0x7 - Reserved

0x8 - Single partition with reduced latency

0x9 - Single partition with Serial EEPROM initialization and reduced latency

0xA - Multi-partition with Unattached ports

0xB - Multi-partition with Unattached ports and I

2

C Reset

0xC - Multi-partition with Unattached ports and Serial EEPROM initialization

0xD - Multi-partition with Unattached ports with I

2

C Reset and Serial EEPROM initial-

ization

0xE - Multi-partition with Disabled ports

0xF - Multi-partition with Disabled ports and Serial EEPROM initialization

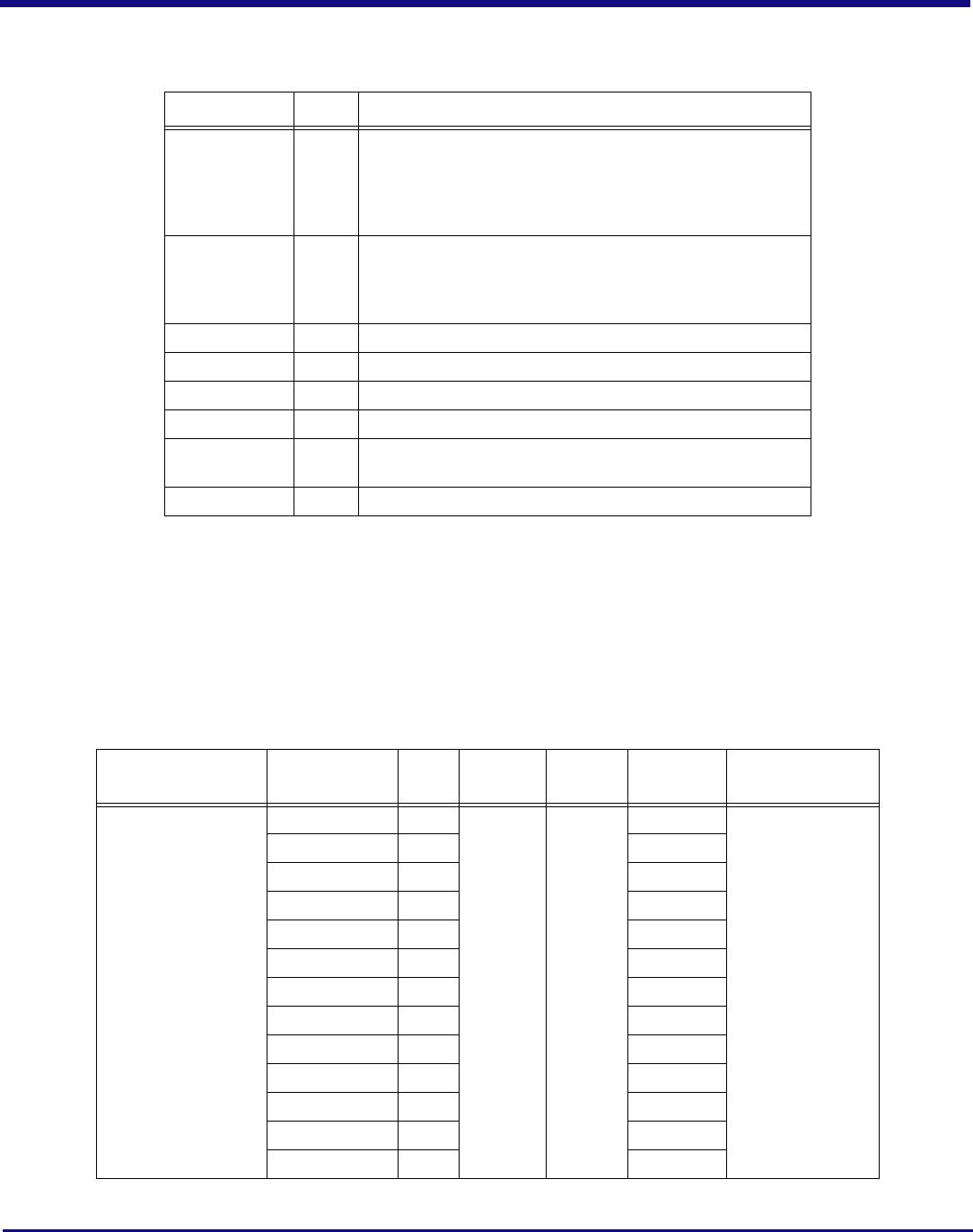

Signal Type Name/Description

JTAG_TCK I JTAG Clock. This is an input test clock used to clock the shifting of data into or out of

the boundary scan logic or JTAG Controller. JTAG_TCK is independent of the system

clock with a nominal 50% duty cycle.

JTAG_TDI I JTAG Data Input. This is the serial data input to the boundary scan logic or JTAG

Controller.

JTAG_TDO O JTAG Data Output. This is the serial data shifted out from the boundary scan logic or

JTAG Controller. When no data is being shifted out, this signal is tri-stated.

JTAG_TMS I JTAG Mode. The value on this signal controls the test mode select of the boundary

scan logic or JTAG Controller.

JTAG_TRST_N I JTAG Reset. This active low signal asynchronously resets the boundary scan logic

and JTAG TAP Controller. An external pull-up on the board is recommended to meet

the JTAG specification in cases where the tester can access this signal. However, for

systems running in functional mode, one of the following should occur:

1) actively drive this signal low with control logic

2) statically drive this signal low with an external pull-down on the board

Table 8 Test Pins

Signal Type Name/Description

Table 7 System Pins (Part 2 of 2)