IDT 89HPES24NT24G2 Datasheet

8 of 35 December 17, 2013

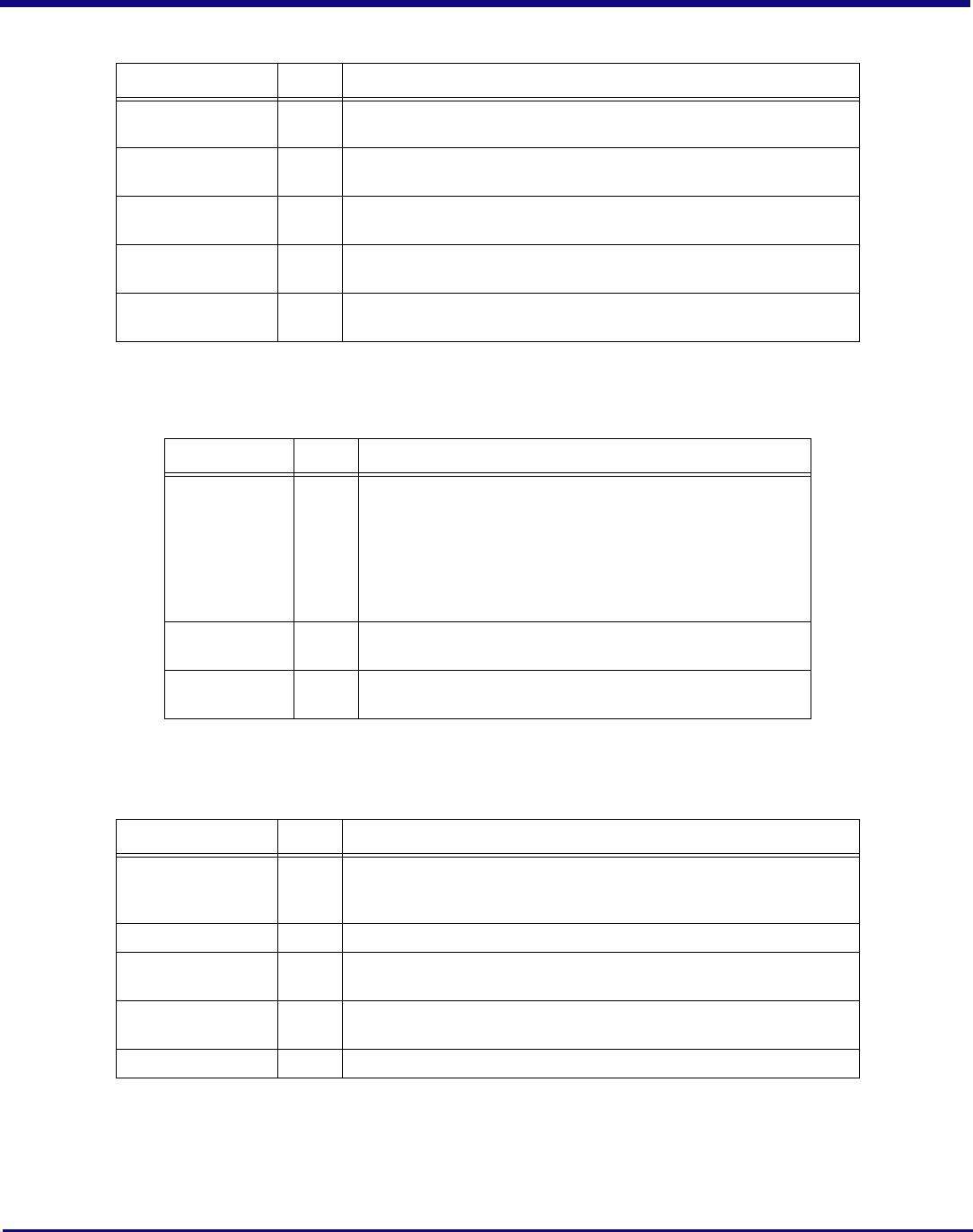

Signal Type Name/Description

GPIO[0] I/O General Purpose I/O.

This pin can be configured as a general purpose I/O pin.

1st Alternate function pin name: PART0PERSTN

1st Alternate function pin type: Input/Output

1st Alternate function: Assertion of this signal initiated a partition funda-

mental reset in the corresponding partition.

2nd Alternate function pin name: P16LINKUPN

2nd Alternate function pin type: Output

2nd Alternate function: Port 16 Link Up Status output.

GPIO[1] I/O General Purpose I/O.

This pin can be configured as a general purpose I/O pin.

1st Alternate function pin name: PART1PERSTN

1st Alternate function pin type: Input/Output

1st Alternate function: Assertion of this signal initiated a partition funda-

mental reset in the corresponding partition.

2nd Alternate function pin name: P16ACTIVEN

2nd Alternate function pin type: Output

2nd Alternate function: Port 16 Link Active Status Output.

GPIO[2] I/O General Purpose I/O.

This pin can be configured as a general purpose I/O pin.

1st Alternate function pin name: PART2PERSTN

1st Alternate function pin type: Input/Output

1st Alternate function: Assertion of this signal initiated a partition funda-

mental reset in the corresponding partition.

2nd Alternate function pin name: P4LINKUPN

2nd Alternate function pin type: Output

2nd Alternate function: Port 4 Link Up Status output.

GPIO[3] I/O General Purpose I/O.

This pin can be configured as a general purpose I/O pin.

1st Alternate function pin name: PART3PERSTN

1st Alternate function pin type: Input/Output

1st Alternate function: Assertion of this signal initiated a partition funda-

mental reset in the corresponding partition.

2nd Alternate function pin name: P4ACTIVEN

2nd Alternate function pin type: Output

2nd Alternate function: Port 4 Link Active Status Output.

GPIO[4] I/O General Purpose I/O.

This pin can be configured as a general purpose I/O pin.

1st Alternate function pin name: FAILOVER0

1st Alternate function pin type: Input

1st Alternate function: When this signal changes state and the correspond-

ing failover capability is enabled, a failover event is signaled.

2nd Alternate function pin name: P0LINKUPN

2nd Alternate function pin type: Output

2nd Alternate function: Port 0 Link Up Status output.

GPIO[5] I/O General Purpose I/O.

This pin can be configured as a general purpose I/O pin.

1st Alternate function pin name: GPEN

1st Alternate function pin type: Output

1st Alternate function: Hot-plug general purpose even output.

2nd Alternate function pin name: P0ACTIVEN

2nd Alternate function pin type: Output

2nd Alternate function: Port 0 Link Active Status Output.

Table 5 General Purpose I/O Pins (Part 1 of 2)