IDT 89HPES24NT24G2 Datasheet

26 of 35 December 17, 2013

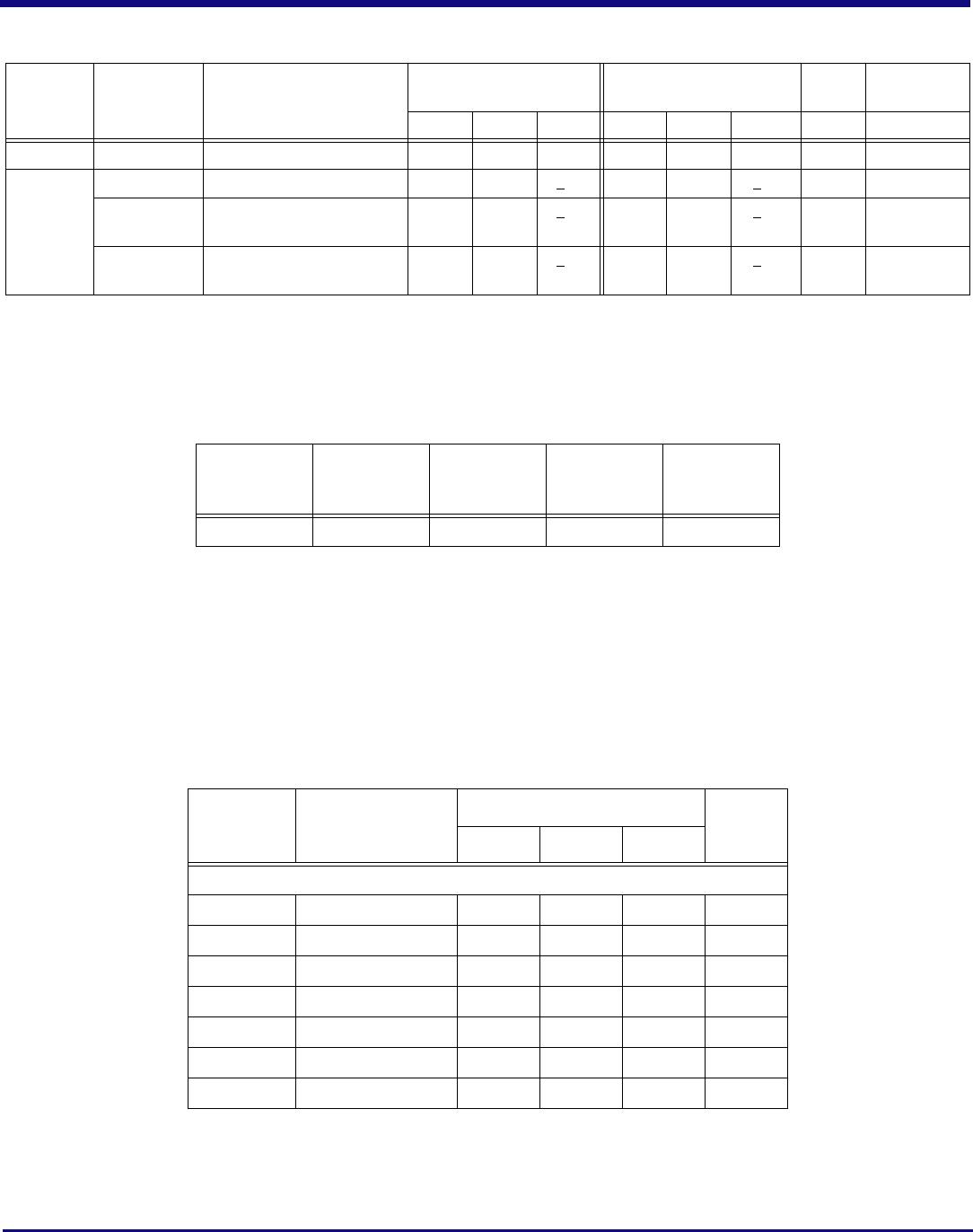

DC Parameter for SCL Pin

V

IL (V)

Input Low 1.11 1.2 1.31 V

V

IH (V)

Input High 1.54 1.65 1.76 V

I

IL_Leak

Input Low Leakage 0 0 0 A

I

IH_Leak

Input High Leakage 0 0 0 A

1.

Data at room and hot temperature.

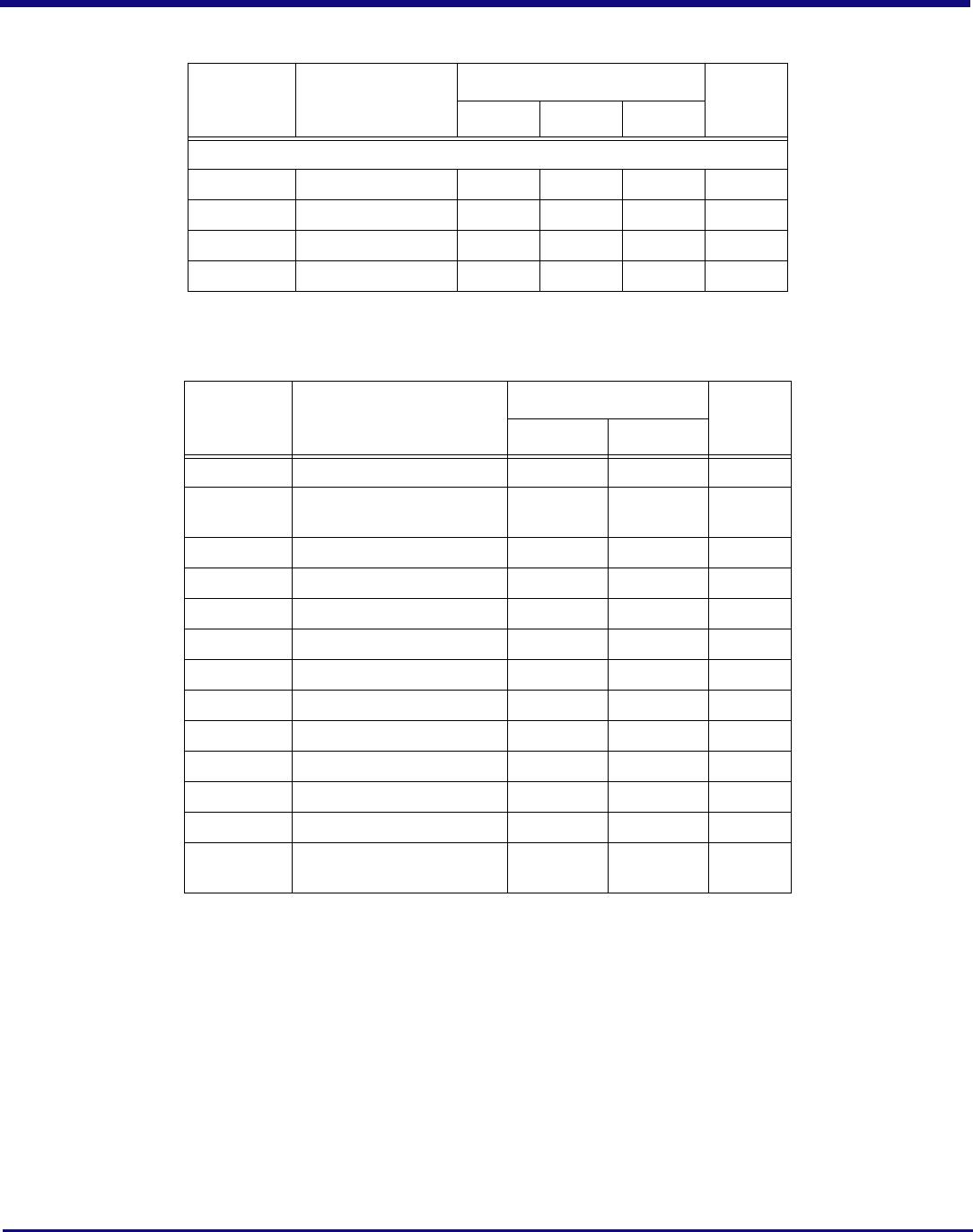

Symbol Parameter

SMBus @3.3V ±10%

1

1.

Data at room and hot temperature.

Unit

Min Max

F

SCL

Clock frequency 5 600 KHz

T

BUF

Bus free time between Stop and

Start

3.5 — s

T

HD:STA

Start condition hold time 1 — s

T

SU:STA

Start condition setup time 1 — s

T

SU:STO

Stop condition setup time 1 — s

T

HD:DAT

Data hold time 1 — ns

T

SU:DAT

Data setup time 1 — ns

T

TIMEOUT

Detect clock low time out — 74.7 ms

T

LOW

2

2.

T

LOW

and

T

HIGH

are measured at F

SCL

= 135 kHz.

Clock low period 3.7 — s

T

HIGH

2

Clock high period 3.7 — s

T

F

Clock/Data fall time — 72.2 ns

T

R

Clock/Data rise time — 68.3 ns

T

POR@10kHz

Time which a device must be

operational after power-on reset

20 — ms

Table 23 SMBus AC Timing Data

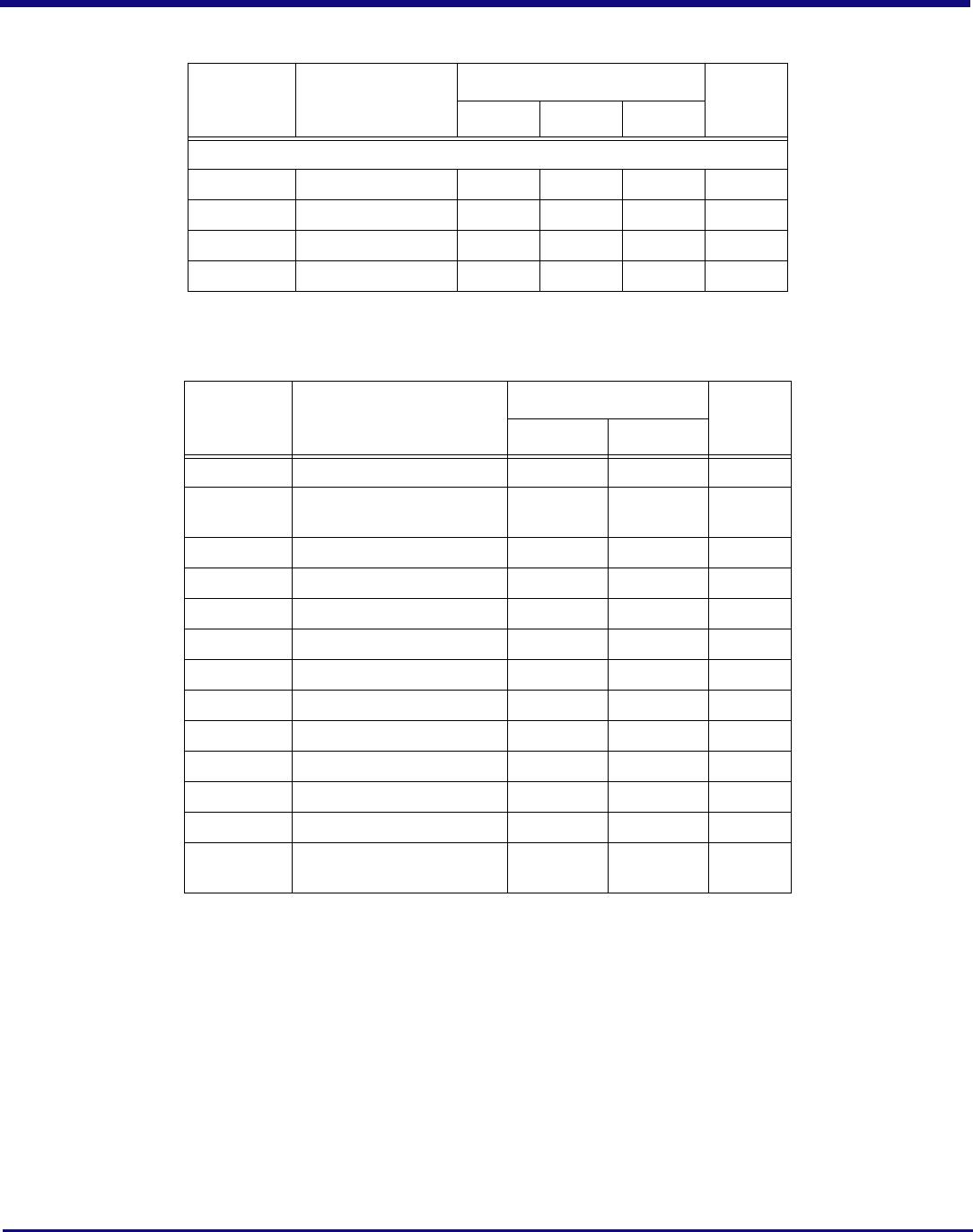

Symbol Parameter

SMBus 2.0 Char. Data

1

Unit

3V 3.3V 3.6V

Table 22 SMBus DC Characterization Data (Part 2 of 2)