LTC5569

17

5569fb

For more information www.linear.com/LTC5569

APPLICATIONS INFORMATION

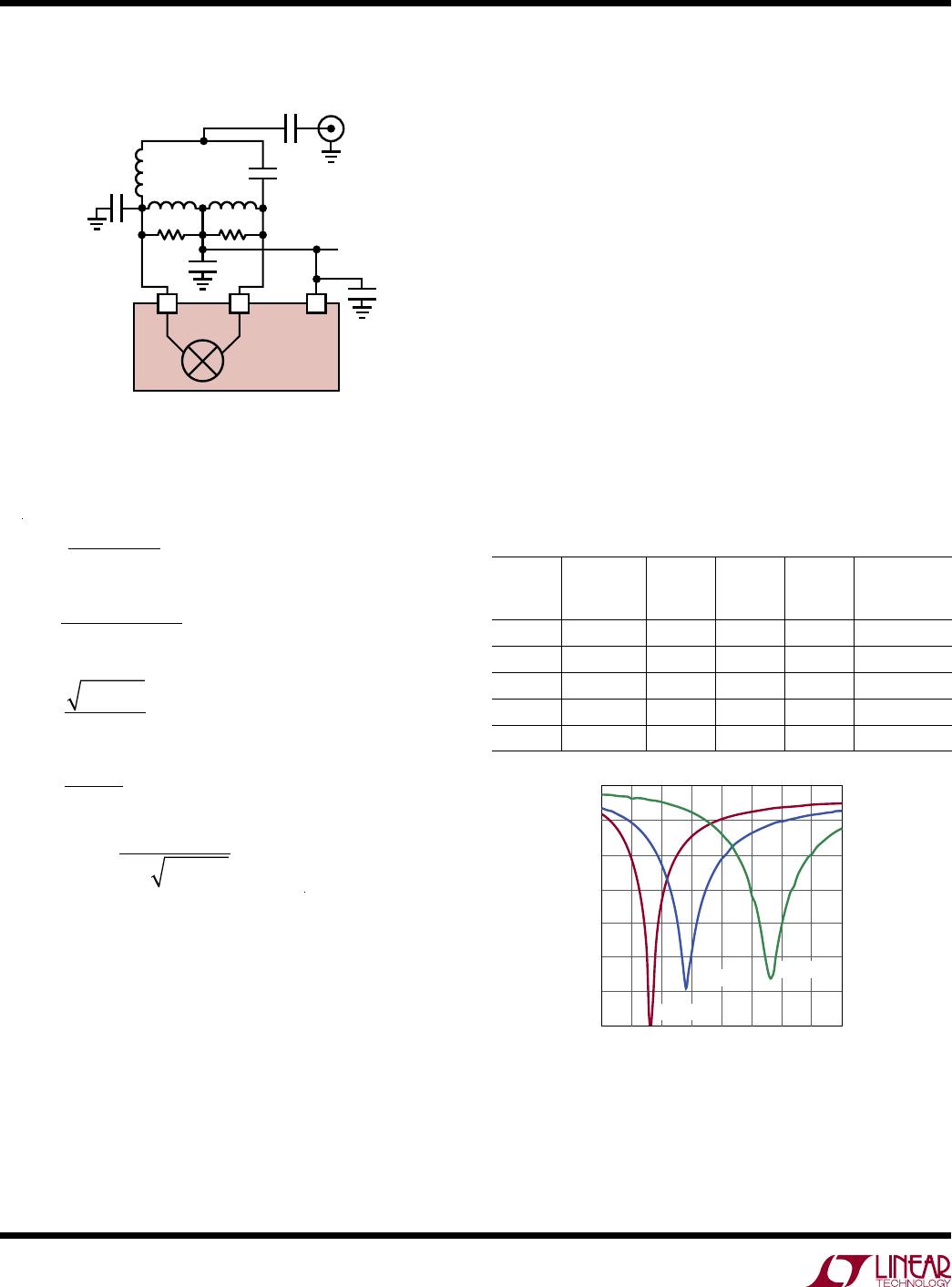

Figure 14. Conversion Gain, IIP3 and SSB NF vs IF Output

Frequency Using Discrete IF Balun Matching

15 14

IFA

–

V

CCA

V

CCA

16

BIASA

54mA

BIAS

3mA

BIAS

LTC5569

IFA

+

13

Figure 15. BIASA Interface (BIASB is Identical)

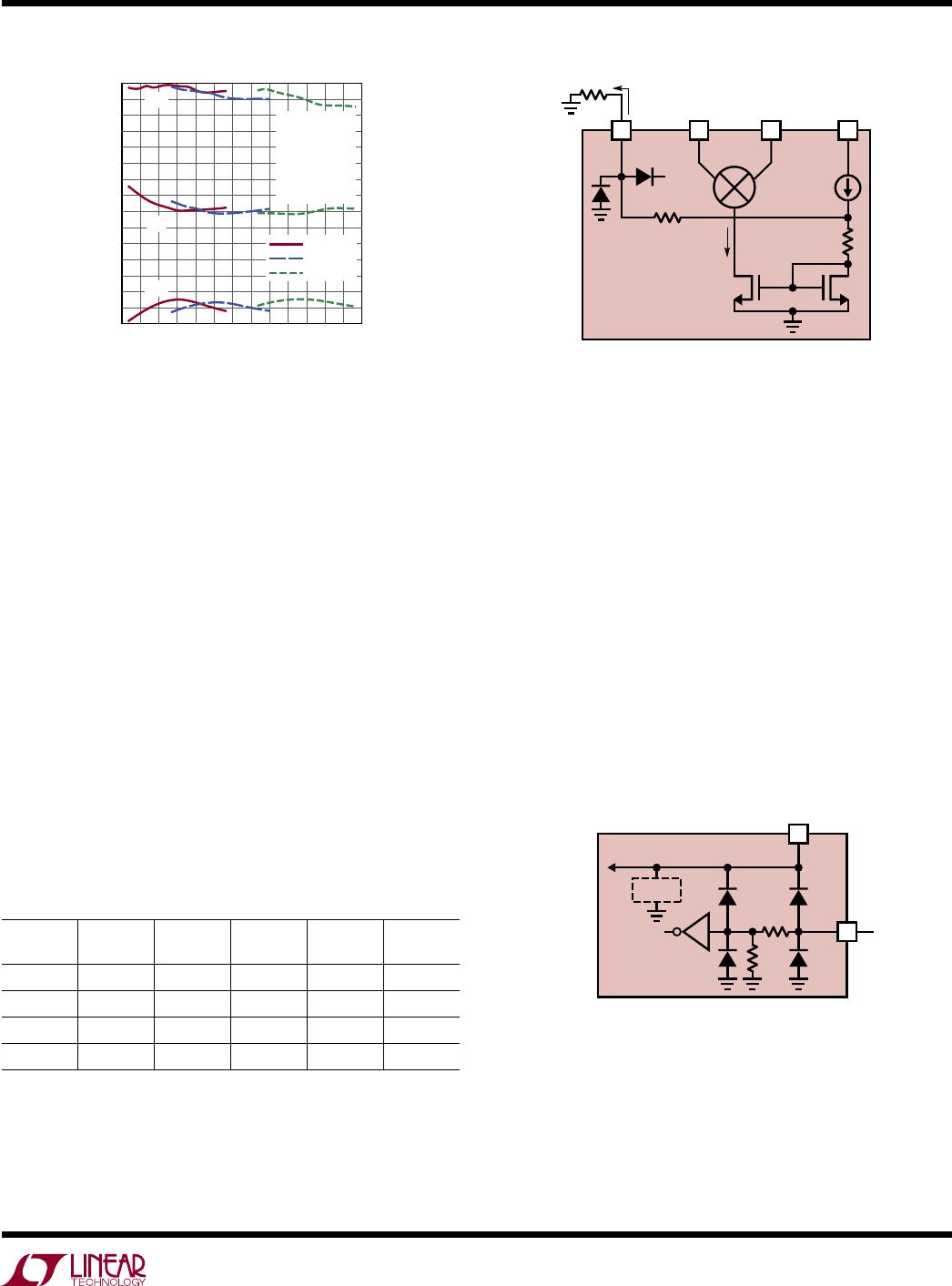

Mixer Bias Current Reduction

The BIASA and BIASB pins (Pins 16 and 5) are available

for reducing the mixer core DC current consumption, of

the A- and B-channels, respectively, at the expense of

linearity and P1dB. For the highest performance, these

pins should be left open circuit. As shown in Figure 15,

an internal bias circuit produces a 3mA reference current

for each mixer core. If a resistor is connected to Pin 16,

as shown in Figure 15, a portion of the reference current

can be shunted to ground, resulting in reduced mixer

core current. For example, R1 = 1k will shunt away 1mA

from Pin 16 and reduce the mixer core current by 33%.

The nominal, open-circuit DC voltage at the BIASA and

BIASB pins is 2.2V. Table 7 lists DC supply current and

RF performance at 1950MHz for various values of R1.

Table 7. Mixer Performance with Reduced Current

(RF = 1950MHz, Low Side LO, IF = 190MHz)

R1 (Ω) I

CC

(mA) G

C

(dB)

IIP3

(dBm)

P1dB

(dBm) NF (dB)

Open 90.0 2.0 26.8 10.2 11.7

10k 85.2 1.9 25.6 10.2 11.4

1k 71.0 1.6 21.4 10.1 10.4

100 58.6 1.1 17.9 8.9 10.0

11

13

CLAMP

300k

500Ω

LTC5569

V

CCA

ENA

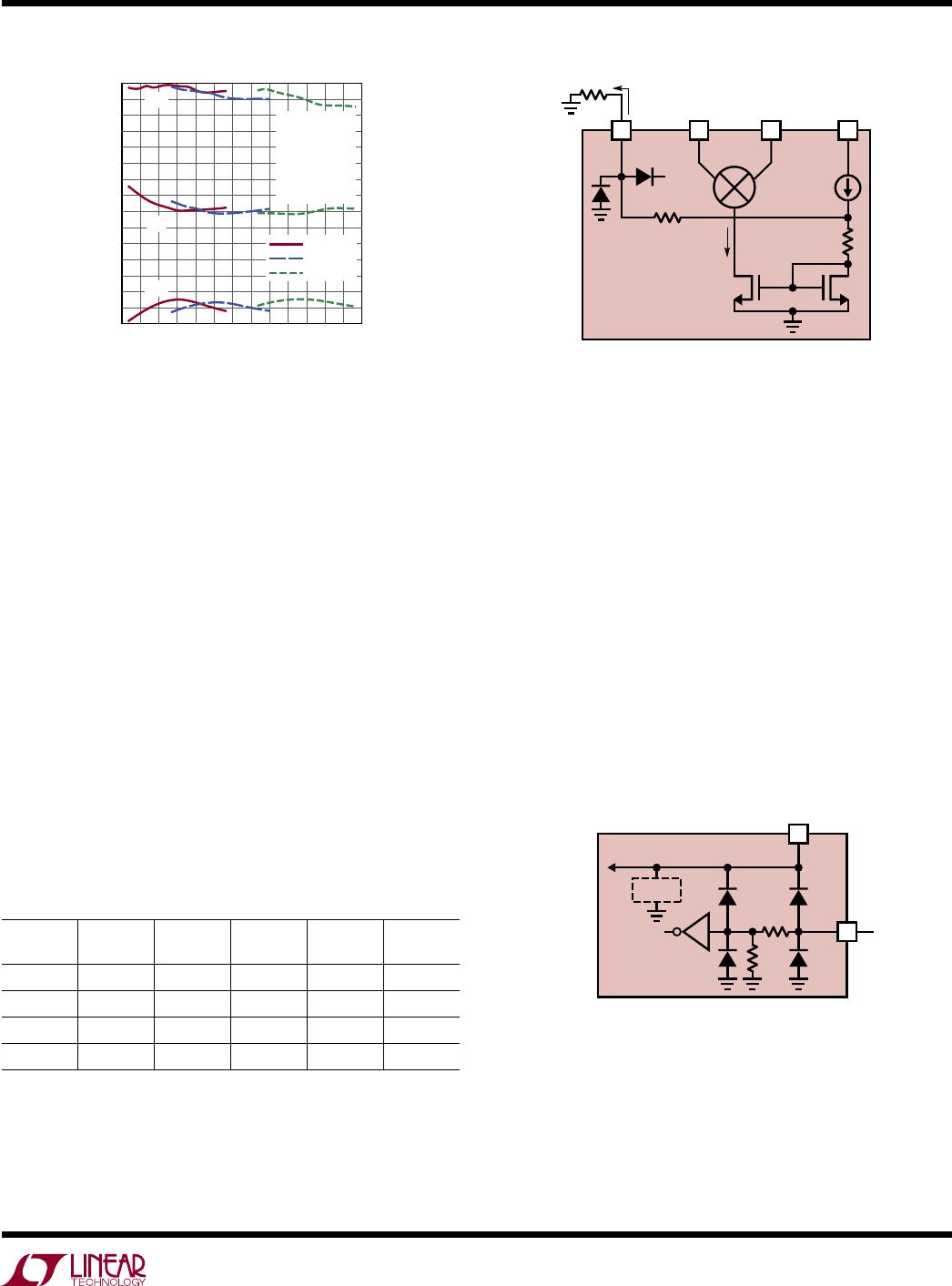

Figure 16. Enable Input Circuit

Enable Interfaces

Figure 16 shows a simplified schematic of the A-chan-

nel enable interface. The B-channel is identical, and not

shown for clarity

. T

o enable the A-channel mixer, the ENA

voltage must be higher than 2.5V. If the enable function is

not required, the pin should be connected directly to V

CC

.

The voltage at the ENA pin should never exceed the power

supply voltage (V

CC

) by more than 0.3V. If this should oc-

cur, the supply current could be sourced through the ESD

diode, potentially damaging the IC.

The ENA and ENB pins have internal 300k pull-down resis

-

tors. Therefore, an unused mixer will be disabled with its

corresponding enable pin left floating.

IF FREQUENCY (MHz)

80

C

(dB), SSB NF (dB), IIP3 (dBm)

14

22

18

26

320

10

6

2

–2

16

24

20

12

8

4

0

140 200

260

380 440

170MHz

240MHz

380MHz

IIP3

G

C

NF

RF = 1950MHz

LOW SIDE LO

P

LO

= 0dBm

Z

RF

= 50Ω

Z

IF

= 50Ω

T

C

= 25°C