MARCH 3, 2017 29 PROGRAMMABLE CLOCK GENERATOR

5P49V5914 DATASHEET

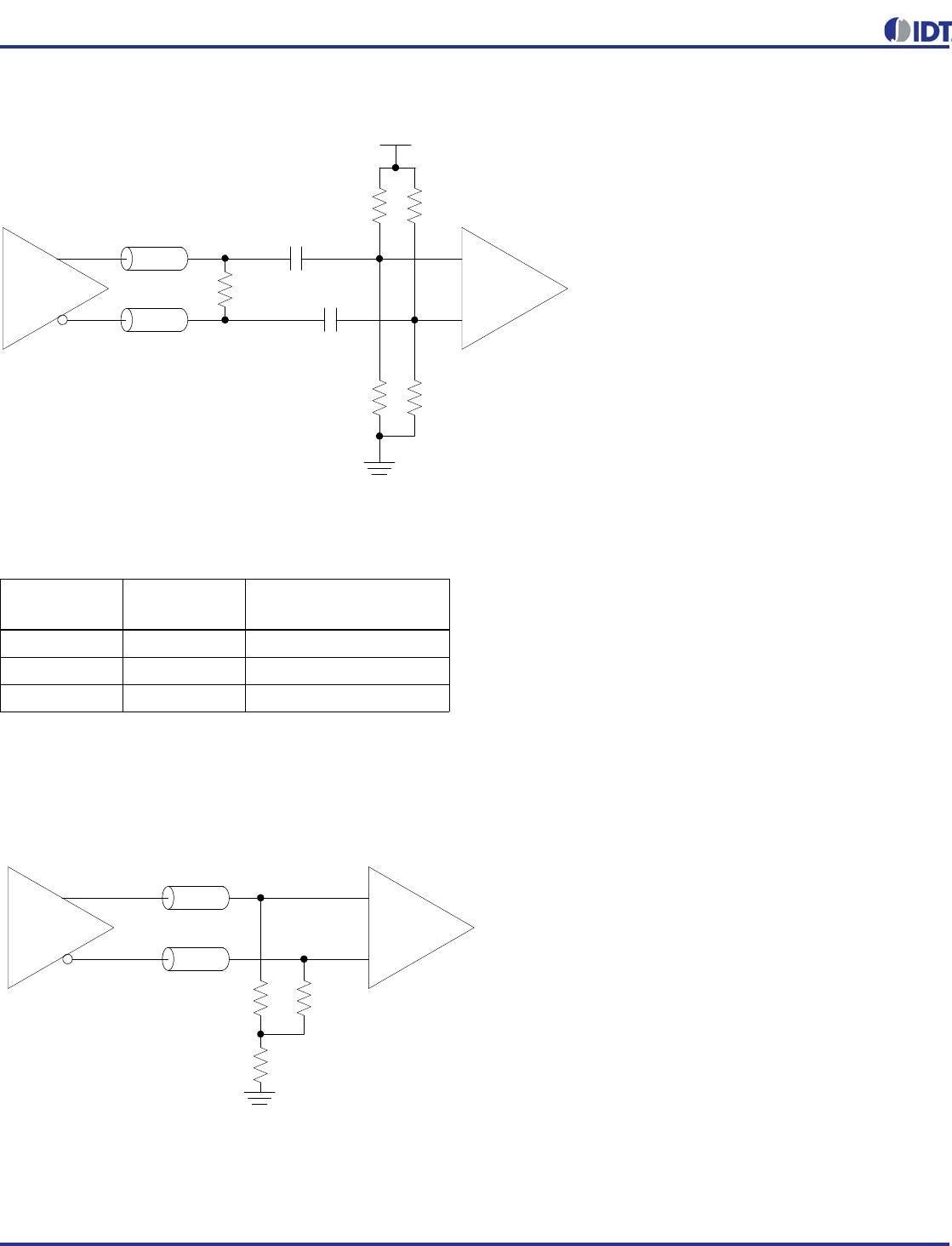

LVDS Driver Termination

For a general LVDS interface, the recommended value for the

termination impedance (Z

T

) is between 90. and 132. The

actual value should be selected to match the differential

impedance (Zo) of your transmission line. A typical

point-to-point LVDS design uses a 100

parallel resistor at the

receiver and a 100

. differential transmission-line

environment. In order to avoid any transmission-line reflection

issues, the components should be surface mounted and must

be placed as close to the receiver as possible. The standard

termination schematic as shown in figure

Standard

Termination

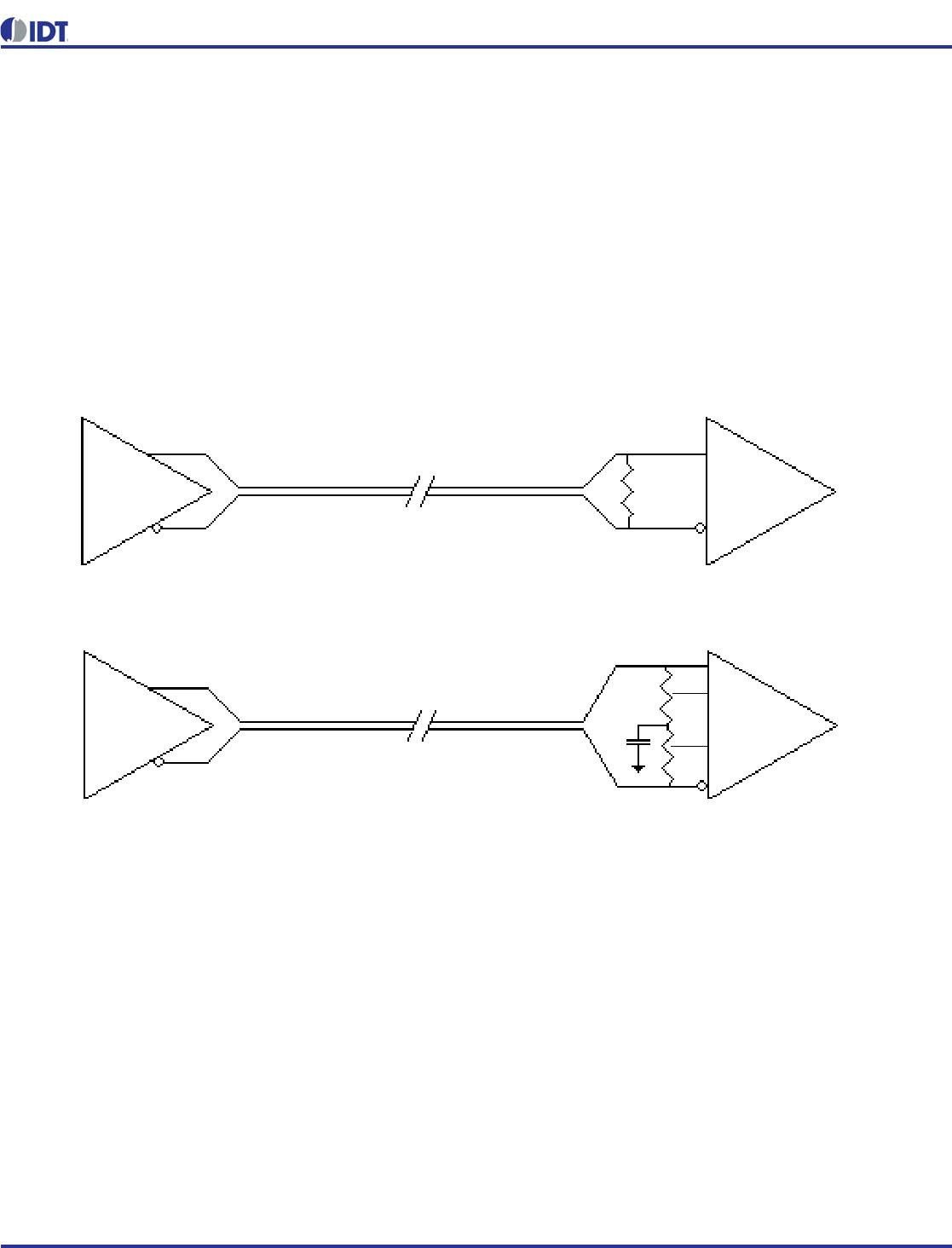

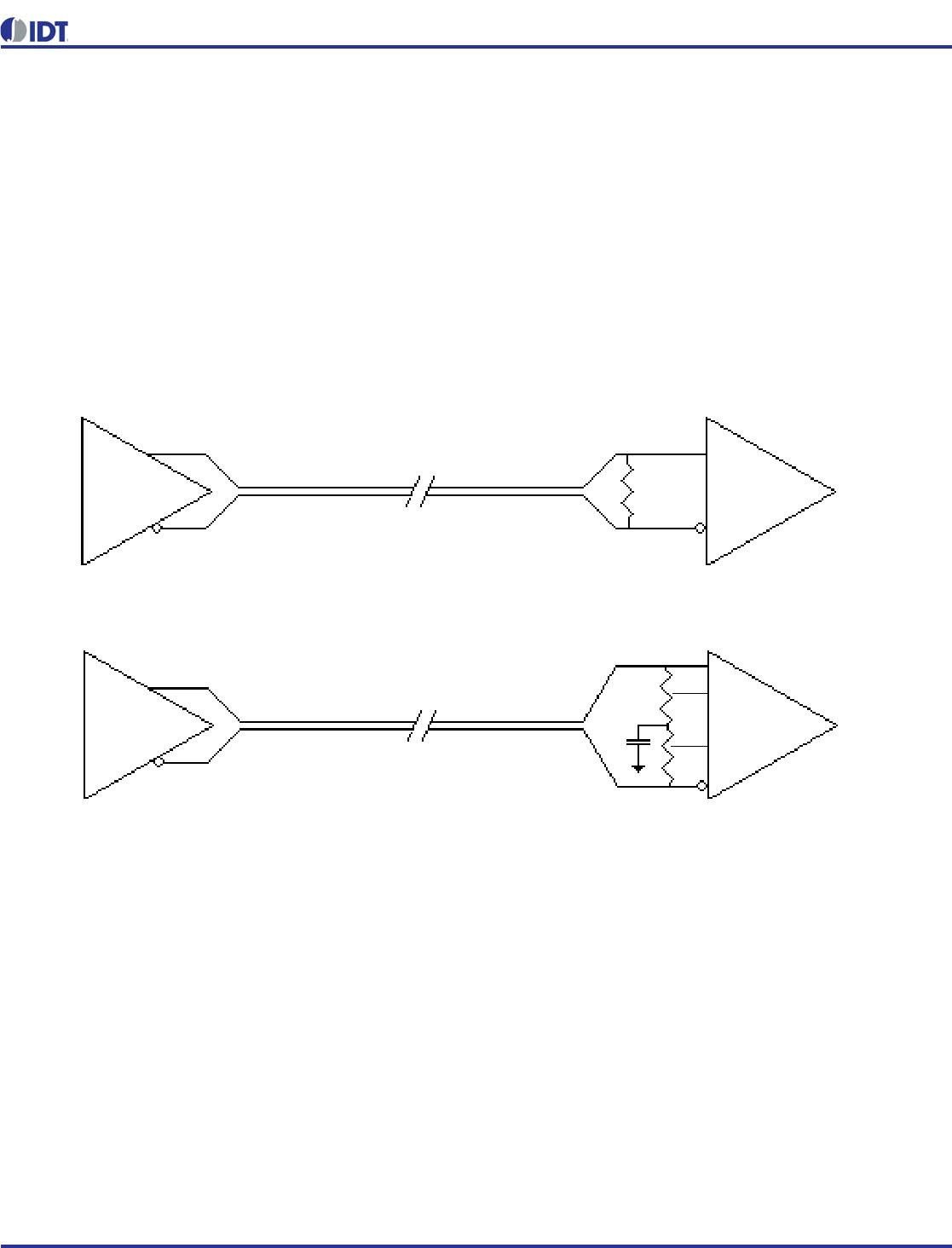

or the termination of figure Optional Termination

can be used, which uses a center tap capacitance to help filter

common mode noise. The capacitor value should be

approximately 50pF. In addition, since these outputs are LVDS

compatible, the input receiver's amplitude and common-mode

input range should be verified for compatibility with the IDT

LVDS output. If using a non-standard termination, it is

recommended to contact IDT and confirm that the termination

will function as intended. For example, the LVDS outputs

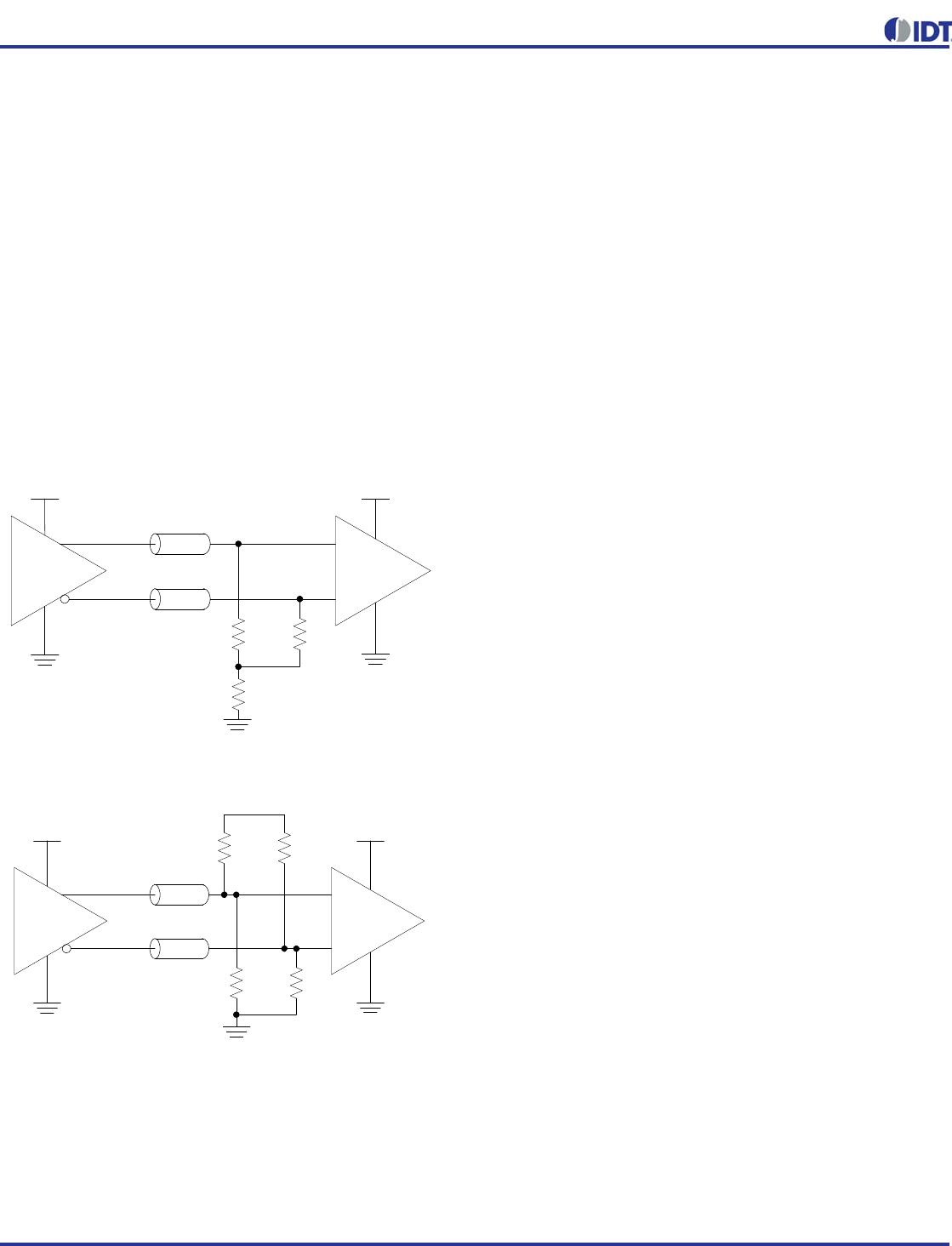

cannot be AC coupled by placing capacitors between the

LVDS outputs and the 100 ohm shunt load. If AC coupling is

required, the coupling caps must be placed between the 100

ohm shunt termination and the receiver. In this manner the

termination of the LVDS output remains DC coupled.

LVDS

Driver

LVDS

Driver

LVDS

Receiver

LVDS

Receiver

Z

T

C

Z

O

Z

T

Z

O

Z

T

Z

T

2

Z

T

2

Standard Termination

Optional Termination