20

40123fb

LTC4012-3

applicaTions inForMaTion

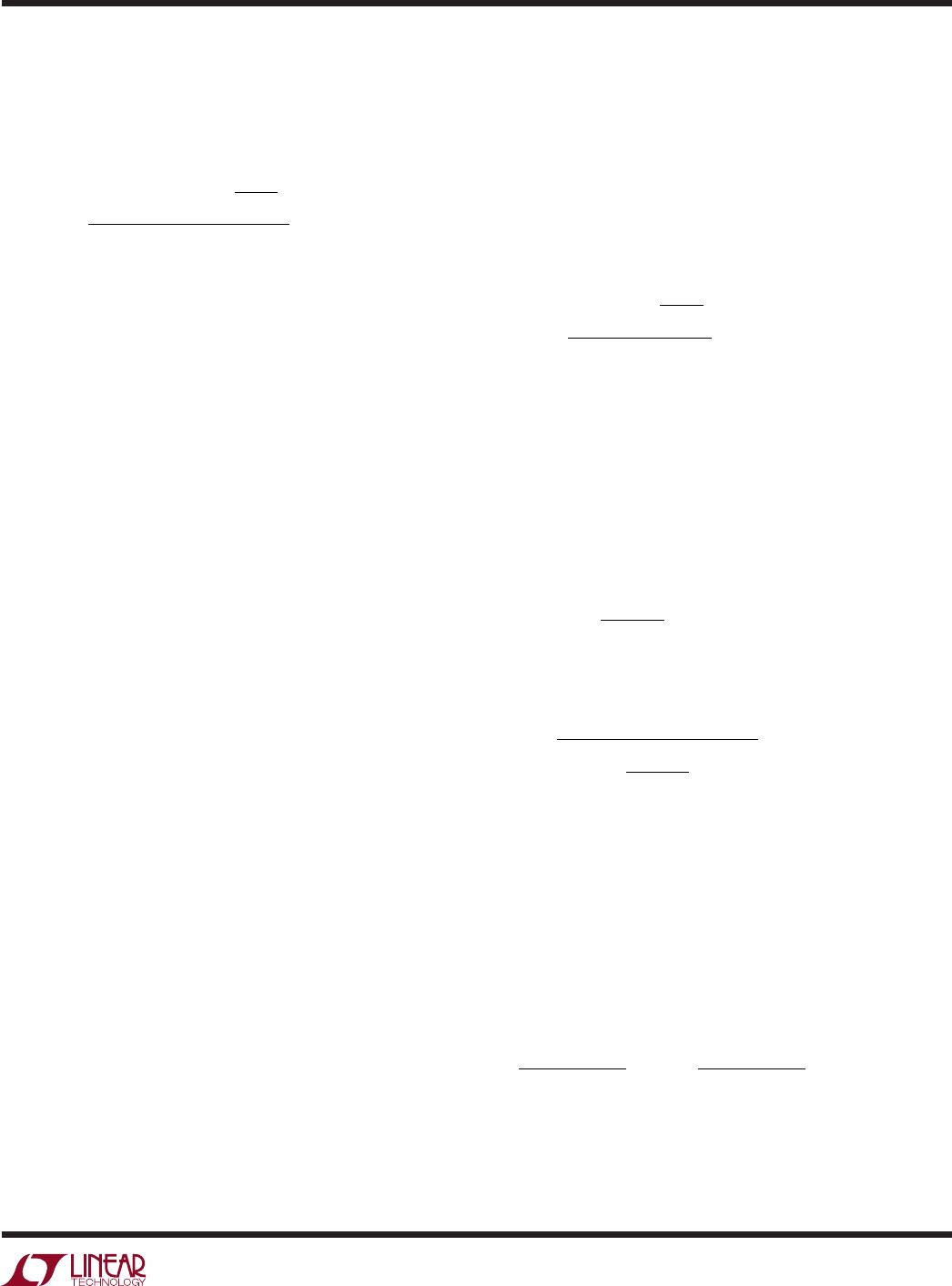

Table 4. Digital Read Back State (IN, Figure 10)

LTC4012-3

CHARGER STATE

OUT STATE

Hi-Z 1

Off 1 1

C/10 Charge 0 1

Bulk Charge 0 0

Input and Output Capacitors

In addition to typical input supply bypassing (0.1µF) on

DCIN, the relatively high ESR of aluminum electrolytic ca-

pacitors is helpful for reducing ringing when hot-plugging

the charger to the AC adapter. Refer to LTC Application

Note 88 for more information.

The input capacitor between system power (drain of top

FET, Figure 1) and GND is required to absorb all input PWM

ripple current, therefore it must have adequate ripple current

rating. Maximum RMS ripple current is typically one-half

of the average battery charge current. Actual capacitance

value is not critical, but using the highest possible voltage

rating on PWM input capacitors will minimize problems.

Consult with the manufacturer before use.

Figure 10. Microprocessor Status Interface

33k

200k

4012-3 F10

V

DD

3.3V

µP

IN

OUT

LTC4012-3

CHRG

7

C/10 CHRG Indicator

The value chosen for R

PROG

has a strong influence on

charge current monitoring and the accuracy of the C/10

charge indicator output (CHRG). The LTC4012-3 uses the

voltage on the PROG pin to determine when charge current

has dropped to the C/10 threshold. The nominal threshold

of 400mV produces an accurate low charge current indi-

cation of C/10 as long as R

PROG

= 26.7k, independent of

all other current programming considerations. However,

it may sometimes be necessary to deviate from this value

to satisfy other application design goals.

If R

PROG

is greater than 26.7k, the actual level at which

low charge current is detected will be less than C/10. The

highest value of R

PROG

that can be used while reliably

indicating low charge current before reaching final V

BAT

is 30.1k. R

PROG

can safely be set to values higher than

this, but low current indication will be lost.

If R

PROG

is less than 26.7k, low charge current detection

occurs at a level higher than C/10. More importantly, the

LTC4012-3 becomes increasingly sensitive to reverse cur-

rent. The lowest value of R

PROG

that can be used without

the risk of erroneous boost operation detection at end of

charge is 26.1k. Values of R

PROG

less than this should not

be used. See the Operation section for more information

about reverse current.

The nominal fractional value of I

MAX

at which C/10 indica-

tion occurs is given by:

I

I

mV R µA

V R

C

MAX

PROG

PROG

10

400 11 67

1 2085

=

( )

– • .

. –

•• .11 67µA

( )

Direct digital monitoring of C/10 indication is possible

with an external application circuit like the one shown in

Figure

9.

By using two different value pull-up resistors, a micro-

processor can detect three states from this pin (charging,

C/10 and not charging). See Figure 10. When a digital

output port (OUT) from the microprocessor drives one

of the resistors and a second digital input port polls the

network, the charge state can be determined as shown

in Table 4.

Figure 9. Digital C/10 Indicator

17

7

INTV

DD

CHRG

Q1

TP0610T

Q2

2N7002

100k

LTC4012-3

4012-3 F09

100k

V

LOGIC

100k

C/10

CHRG

100k

Q3

2N7002