MAX2361/MAX2363/MAX2365

Complete Dual-Band

Quadrature Transmitters

______________________________________________________________________________________ 13

Programmable Registers

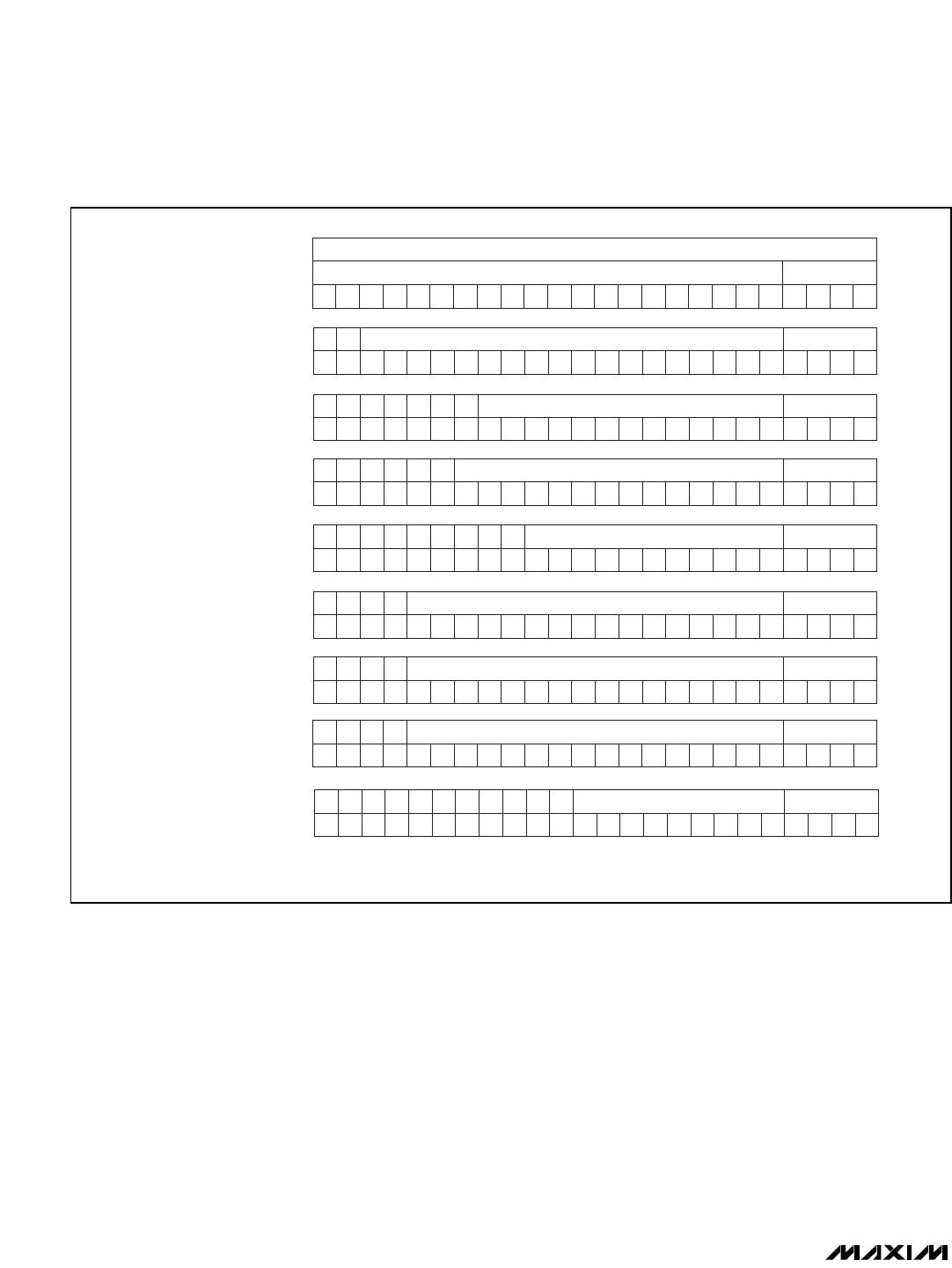

The MAX2361/MAX2363/MAX2365 include eight pro-

grammable registers consisting of four divide registers,

a configuration register, an operational control register,

a current control register, and a test register. Each reg-

ister consists of 24 bits. The 4 least significant bits

(LSBs) are the register’s address. The 20 most signifi-

cant bits (MSBs) are used for register data. All registers

contain some “don't care” bits. These can be either a

“0” or a “1” and will not affect operation (Figure 1). Data

is shifted in MSB first, followed by the 4-bit address.

When CS is low, the clock is active and data is shifted

with the rising edge of the clock. When CS transitions to

high, the shift register is latched into the register select-

ed by the contents of the address bits. Power-up

defaults for the eight registers are shown in Table 1.

The dividers and control registers are programmed

from the SPI/QSPI/MICROWIRE-compatible serial port.

The RFM register sets the main frequency divide ratio

for the RF PLL. The RFR register sets the reference fre-

quency divide ratio. The RF VCO frequency can be

determined by the following:

RF VCO frequency = f

REF

✕

(RFM / RFR)

IFM and IFR registers are similar:

IF VCO frequency = f

REF

✕

(IFM / IFR)

where f

REF

is the external reference frequency.

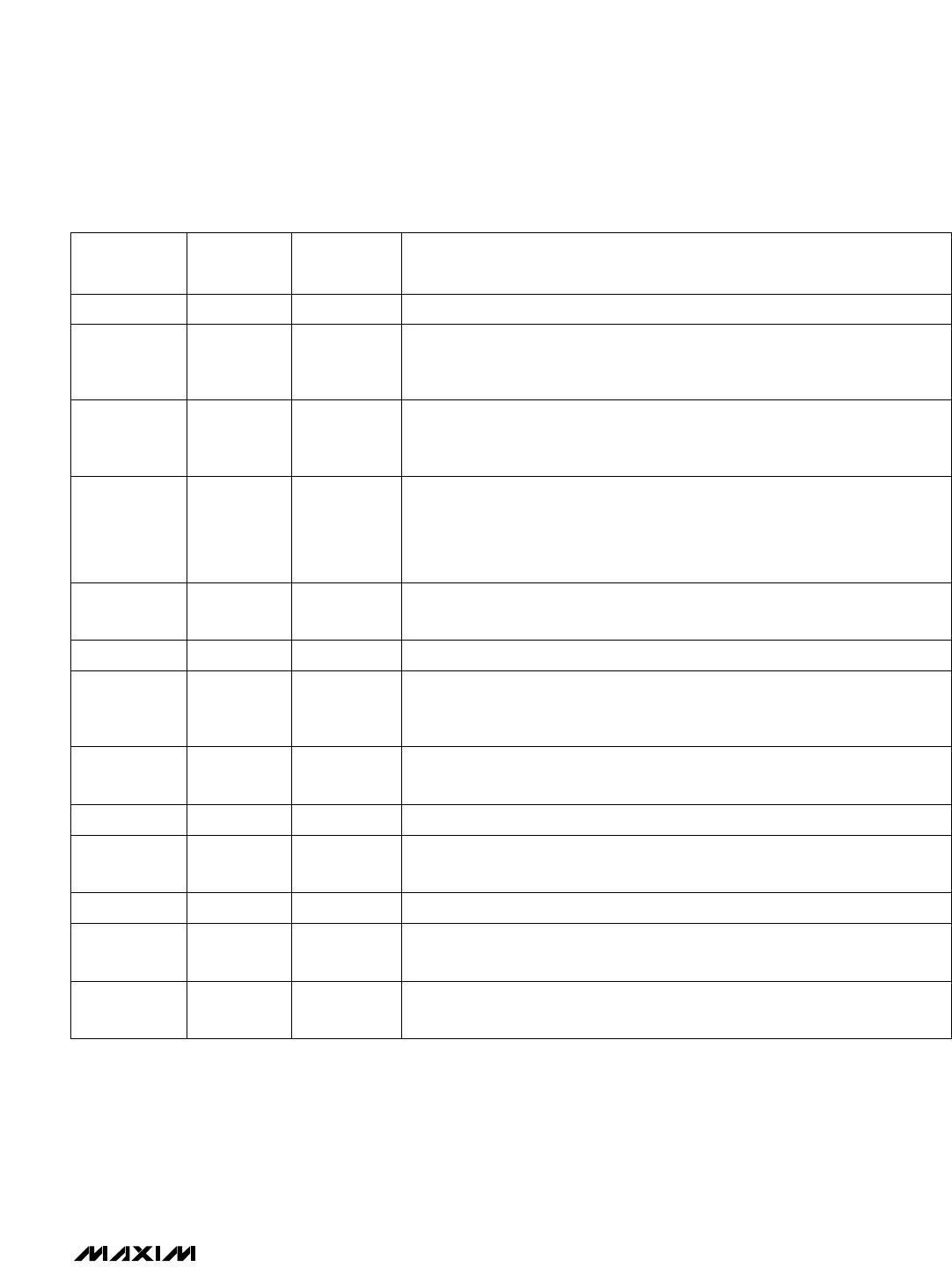

The operational control register (OPCTRL) controls the

state of the MAX2361/MAX2363/MAX2365. See Table 2

for the function of each bit.

The configuration register (CONFIG) sets the configura-

tion for the RF/IF PLL and the baseband I/Q input lev-

els. See Table 3 for a description of each bit.

The current control register modifies the bias current to

accommodate different operation modes. In the high-

power mode, MPL = 1 sets the bias current and con-

version gain to deliver a minimum of +8dBm output

power from the PA drivers. In the low-power mode,

MPL = 0 sets the bias current and conversion gain to

deliver a minimum of +5dBm output power from the PA

drivers. I_MULT sets the current multiplication factor for

the PA driver stages according to Table 5. THROT-

TLE_BACK sets the rate of bias current changes when

the output power changes according to Table 6. For

example, when THROTTLE_BACK = 011 (default), the

PA driver bias current reduces by 1dBmA for every

1dB reduction in output power. THROTTLE_BACK =

000 setting gives a more aggressive current reduction

(1.3dBmA/dB power) at the expense of linearity.

THROTTLE_BACK setting does not affect the bias cur-

rent at maximum power level.

The test register has to be 100hex for normal operation.

The best way to ensure this is to program the test regis-

er to 100hex.

Power Management

Bias control is distributed among several functional

sections and can be controlled to accommodate many

different power-down modes as shown in Table 8.

The serial interface remains active during shutdown.

Setting SHDN_BIT = 0 or SHDN = GND powers down

the device. In either case, PLL programming and regis-

ter information is retained.

Signal Flow Control

Table 9 shows an example of key registers for triple-

mode operation, assuming half-band PCS and IF fre-

quencies of 228.6MHz/263.6MHz.

Applications Information

The MAX2361 is designed for use in dual-band, triple-

mode systems. It is recommended for triple-mode hand-

sets (Figure 2). The MAX2363 is designed for use in

CDMA PCS handset or W-CDMA systems (Figure 3).

The MAX2365 is designed for use in dual-mode cellular

systems (Figure 4).

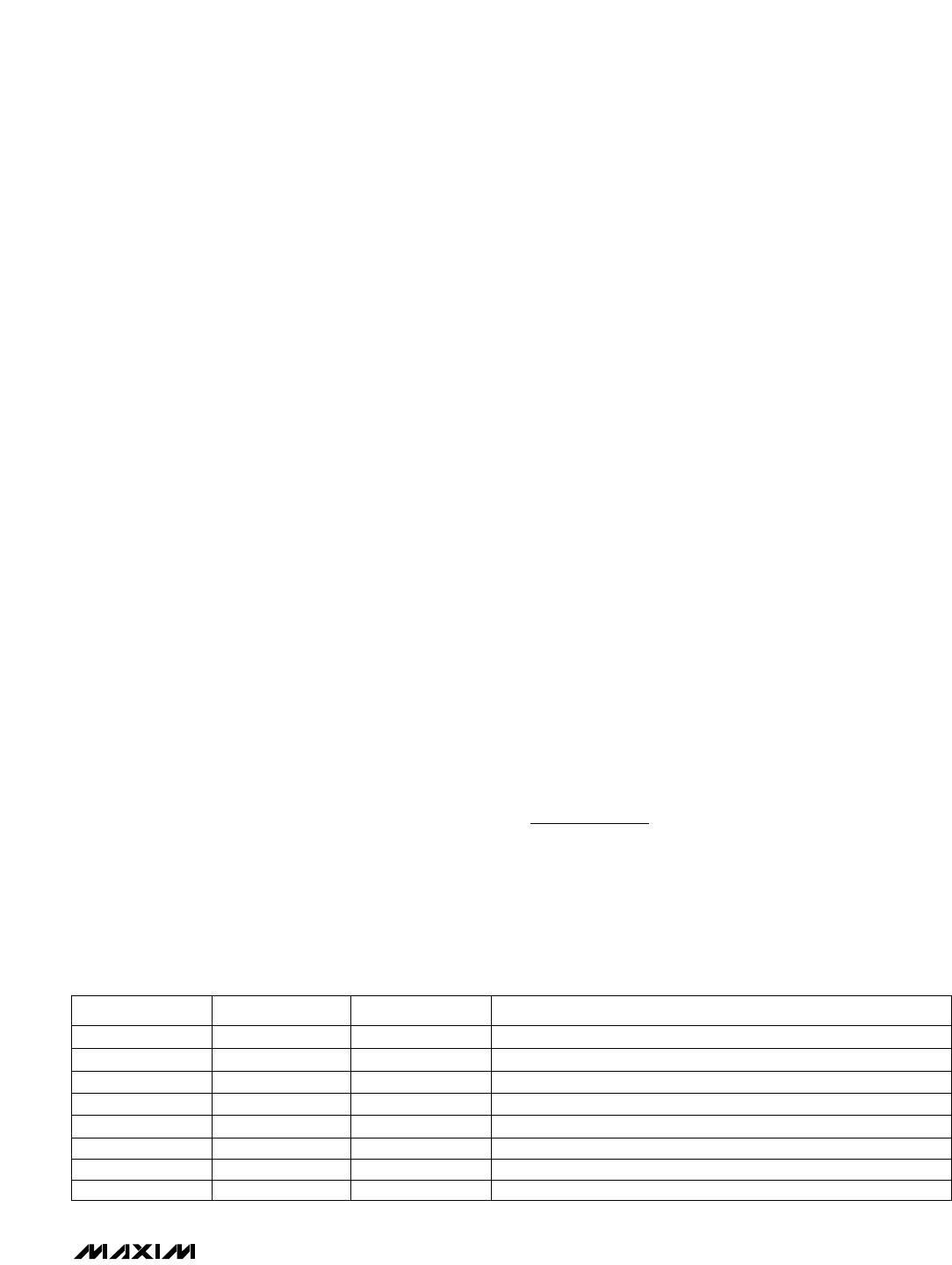

Table 1. Register Power-Up Default States

TEST 0111

b

100 hex Test-mode control

CONFIG

OPCTRL

IFR

0101

b

0100

b

0011

b

0492 dec

090F hex

D03F hex

IFM

RFR

RFM

REGISTER

0010

b

0001

b

0000

b

ADDRESSDEFAULT

32214 dec

656 dec

6519 dec

Configuration and setup control

Operational control settings

IF R divider count

IF M divider count

RF R divider count

RF M divider count

FUNCTION

I

CC

CTRL 0110

b

0038 hex Current multiplication factor, PLL band