PCA9505_9506 All information provided in this document is subject to legal disclaimers. © NXP B.V. 2010. All rights reserved.

Product data sheet Rev. 4 — 3 August 2010 13 of 34

NXP Semiconductors

PCA9505/06

40-bit I

2

C-bus I/O port with RESET, OE and INT

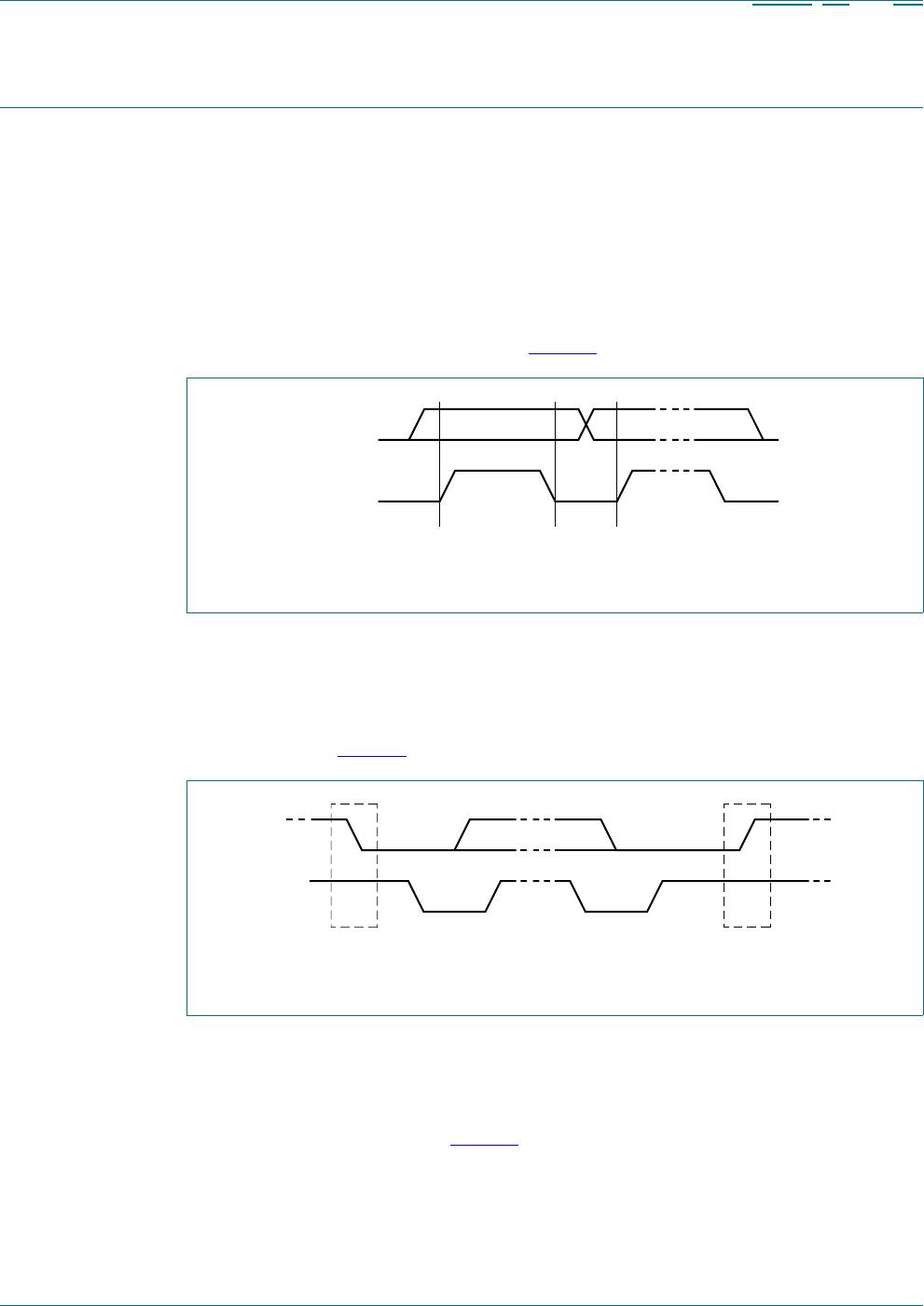

7.6 Interrupt output (INT)

The open-drain active LOW interrupt is activated when one of the port pins changes state

and the port pin is configured as an input and the interrupt on it is not masked. The

interrupt is deactivated when the port pin input returns to its previous state or the Input

Port register is read.

Remark: Changing an I/O from an output to an input may cause a false interrupt to occur

if the state of the pin does not match the contents of the Input Port register.

Only a read of the Input Port register that contains the bit(s) image of the input(s) that

generated the interrupt clears the interrupt condition.

If more than one input register changed state before a read of the Input Port register is

initiated, the interrupt is cleared when all the input registers containing all the inputs that

changed are read.

Example: If IO0_5, IO2_3, and IO3_7 change state at the same time, the interrupt is

cleared only when INREG0, INREG2, and INREG3 are read.

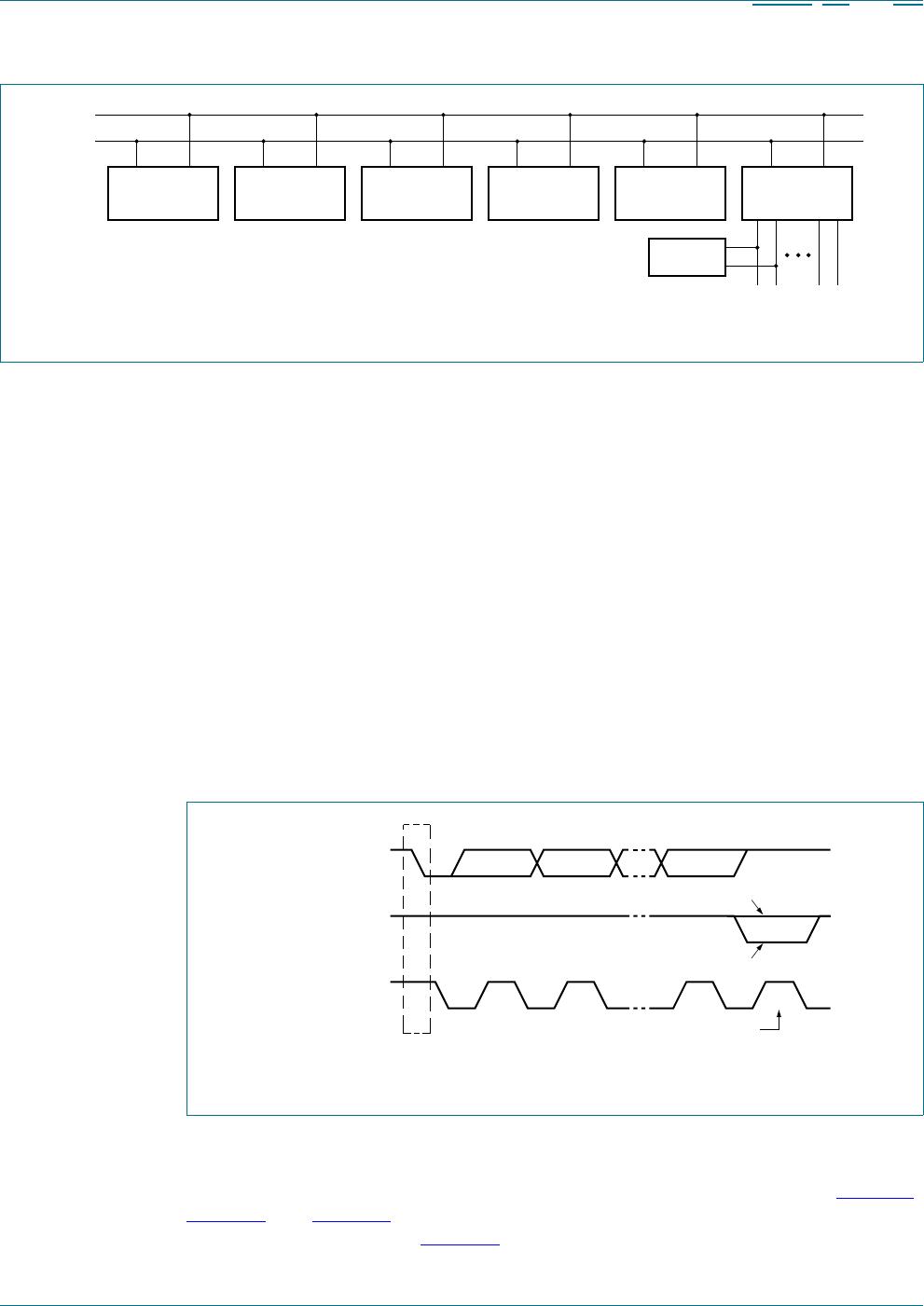

7.7 Output enable input (OE)

The active LOW output enable pin allows to enable or disable all the I/Os at the same

time. When a LOW level is applied to the OE

pin, all the I/Os configured as outputs are

enabled and the logic value programmed in their respective OP registers is applied to the

pins. When a HIGH level is applied to the OE

pin, all the I/Os configured as outputs are

3-stated.

For applications requiring LED blinking with brightness control, this pin can be used to

control the brightness by applying a high frequency PWM signal on the OE

pin. LEDs can

be blinked using the Output Port registers and can be dimmed using the PWM signal on

the OE

pin thus controlling the brightness by adjusting the duty cycle.

7.8 Live insertion

The PCA9505/06 are fully specified for live insertion applications using I

OFF

, power-up

3-states, robust state machine, and 50 ns noise filter. The I

OFF

circuitry disables the

outputs, preventing damaging current backflow through the device when it is powered

down. The power-up 3-state’s circuitry places the outputs in the high-impedance state

during power-up and power-down, which prevents driver conflict and bus contention.

The robust state machine does not respond until it sees a valid START condition and the

50 ns noise filter will filter out any insertion glitches. The PCA9505/06 will not cause

corruption of active data on the bus, nor will the device be damaged or cause damage to

devices already on the bus when similar featured devices are being used.

7.9 Standby

The PCA9505/06 goes into standby when the I

2

C-bus is idle. Standby supply current is

lower than 1 μA (typical).