PCA9505_9506 All information provided in this document is subject to legal disclaimers. © NXP B.V. 2010. All rights reserved.

Product data sheet Rev. 4 — 3 August 2010 9 of 34

NXP Semiconductors

PCA9505/06

40-bit I

2

C-bus I/O port with RESET, OE and INT

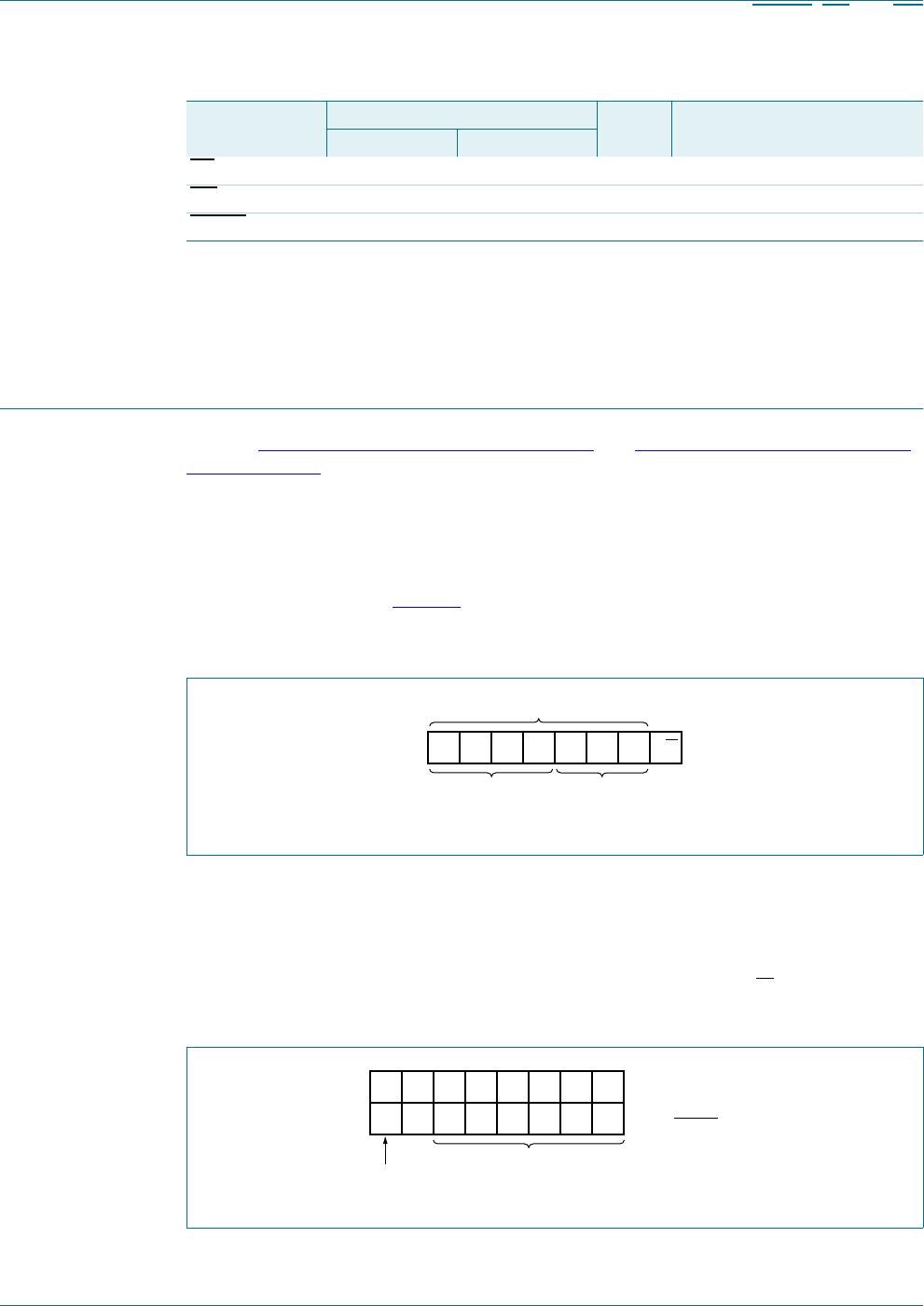

7.3 Register definitions

Table 3. Register summary

Register #

(hex)

D5 D4 D3 D2 D1 D0 Symbol Access Description

Input Port registers

00 000000IP0 read only Input Port register bank 0

01 000001IP1 read only Input Port register bank 1

02 000010IP2 read only Input Port register bank 2

03 000011IP3 read only Input Port register bank 3

04 000100IP4 read only Input Port register bank 4

05 000101- - reserved for future use

06 000110- - reserved for future use

07 000111- - reserved for future use

Output Port registers

08 001000OP0 read/writeOutput Port register bank 0

09 001001OP1 read/writeOutput Port register bank 1

0A 001010OP2 read/writeOutput Port register bank 2

0B 001011OP3 read/writeOutput Port register bank 3

0C 001100OP4 read/writeOutput Port register bank 4

0D 001101- - reserved for future use

0E 001110- - reserved for future use

0F 001111- - reserved for future use

Polarity Inversion registers

10 010000PI0 read/writePolarity Inversion register bank 0

11 010001PI1 read/writePolarity Inversion register bank 1

12 010010PI2 read/writePolarity Inversion register bank 2

13 010011PI3 read/writePolarity Inversion register bank 3

14 010100PI4 read/writePolarity Inversion register bank 4

15 010101- - reserved for future use

16 010110- - reserved for future use

17 010111- - reserved for future use

I/O Configuration registers

18 011000IOC0 read/writeI/O Configuration register bank 0

19 011001IOC1 read/writeI/O Configuration register bank 1

1A 011010IOC2 read/writeI/O Configuration register bank 2

1B 011011IOC3 read/writeI/O Configuration register bank 3

1C 011100IOC4 read/writeI/O Configuration register bank 4

1D 011101- - reserved for future use

1E 011110- - reserved for future use

1F 011111- - reserved for future use