xxxxxxxxxxxxxxxxxxxxx xxxxxxxxxxxxxxxxxxxxxxxxxx xxxxxxx x x x xxxxxxxxxxxxxxxxxxxxxxxxxxxxxx xxxxxxxxxxxxxxxxxxx xx xx xxxxx

xxxxxxxxxxxxxxxxxxxxxxxxxxx xxxxxxxxxxxxxxxxxxx xxxxxx xxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxx xxxxxxxxxxxx x x

xxxxxxxxxxxxxxxxxxxxx xxxxxxxxxxxxxxxxxxxxxxxxxxxxxx xxxxx xxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxx xxxxxxxx

xxxxxxxxxxxxxxxxxxxxxxxxx xxxxxxxxxxxxxxxxxxxx xxx

PCA9505_9506 All information provided in this document is subject to legal disclaimers. © NXP B.V. 2010. All rights reserved.

Product data sheet Rev. 4 — 3 August 2010 18 of 34

NXP Semiconductors

PCA9505/06

40-bit I

2

C-bus I/O port with RESET, OE and INT

If AI = 0, the same register is read during the whole sequence.

If AI = 1, the register value is incremented after each read. When the last register bank is read, it rolls over to the first byte of the category (see category definition in

Section 7.2 “Command register”).

The INT

signal is released only when the last register containing an input that changed has been read. For example, when IO2_4 and IO4_7 change at the same time and

an Input Port register’s read sequence is initiated, starting with IP0, INT

is released after IP4 is read (and not after IP2 is read).

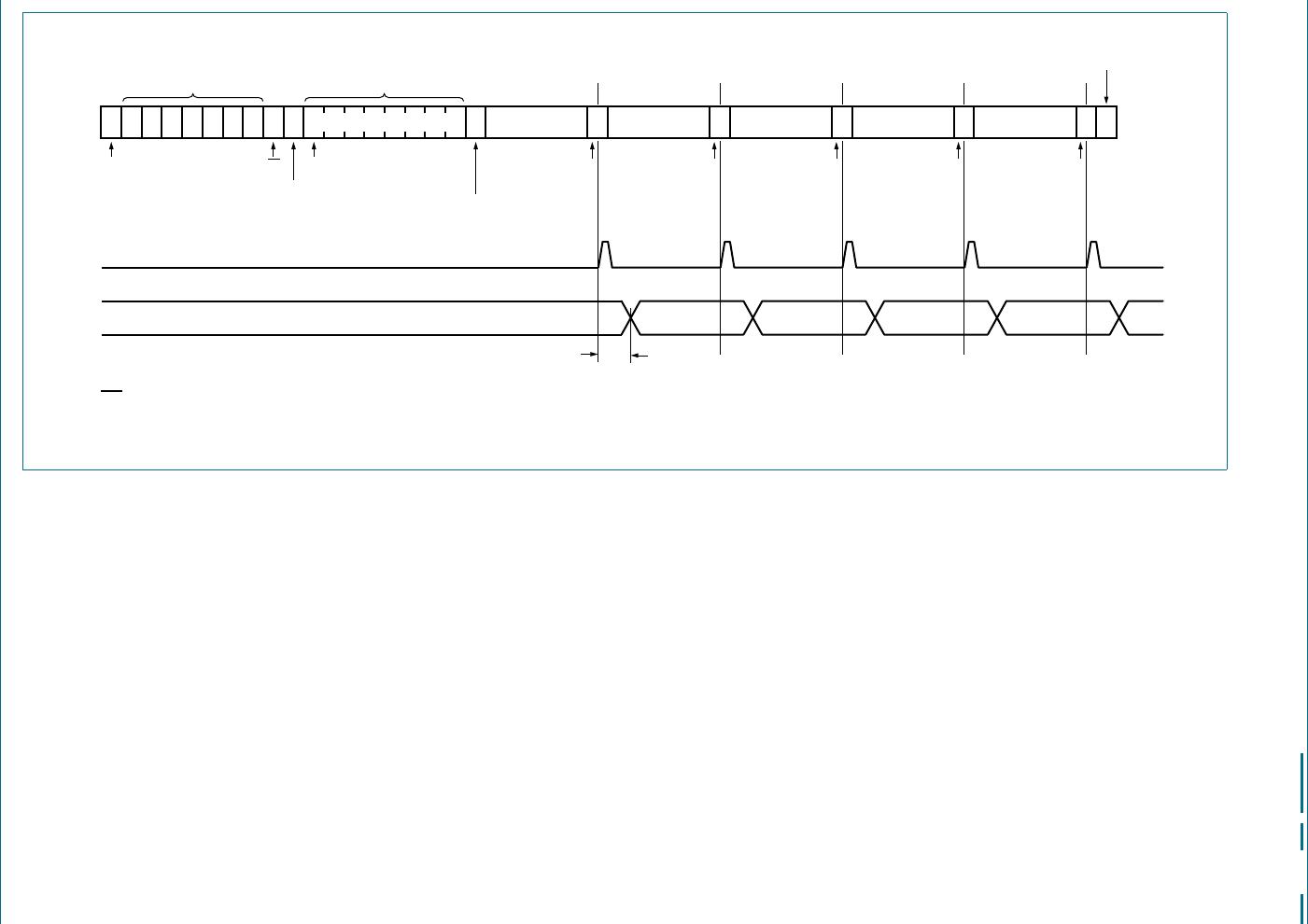

Fig 14. Read from Input Port, Output Port, I/O Configuration, Polarity Inversion or Mask Interrupt registers

002aab499

0 1 0 0 0

slave address

R/W

S

START condition

SDA A

acknowledge

from slave

1 0 D5 D4 D3 D2 D1 D0

command register

AI = 1

A

acknowledge from slave

A

P

STOP

condition

A

acknowledge from master

D[5:0] = 00 1000 for Output Port register bank 0

D[5:0] = 01 0000 for Polarity Inversion register bank 0

Sr

repeated START condition

0 1 0 0 1

slave address

R/W

A

acknowledge from slave

D[5:0] = 01 1000 for Configuration register bank 0

(cont.)

At this moment master-transmitter becomes master-receiver,

and slave-receiver becomes slave-transmitter.

DATA

data from register

first byte

register determined by D[5:0]

A

acknowledge from master

DATA

data from register

second byte

DATA

data from register

last byte

no acknowledge from master

D[5:0] = 00 0000 for Input Port register bank 0

D[5:0] = 10 0000 for Mask Interrupt register bank 0

A2 A1 A0 A2 A1 A0