AD8307 Data Sheet

Rev. E | Page 12 of 24

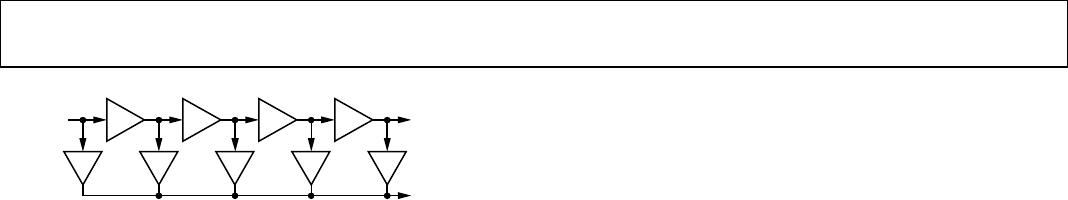

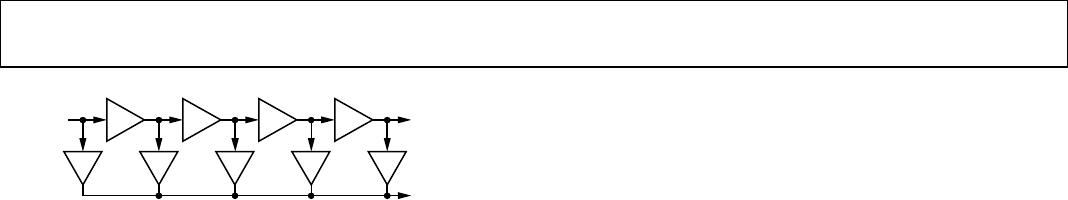

01082-026

IN

V

LIM

I

OUT

A/0

g

m

A/0

g

m

A/0

g

m

A/0

g

m

g

m

AV

IN

A

2

V

IN

A

3

V

IN

A

4

V

IN

Figure 26. Log Amp Using A/0 Stages and Auxiliary Summing Cells

The chief advantage of this approach is that the slope voltage can

now be decoupled from the knee voltage, E

K

= 2 kT/q, which is

inherently PTAT. By contrast, the simple summation of the cell

outputs results in a very high temperature coefficient of the

slope voltage given in Equation 6. To do this, the detector stages

are biased with currents (not shown), which are rendered stable

with temperature. These are derived either from the supply voltage

(as in the AD606 and AD608) or from an internal band gap

reference (as in the AD640 and AD8307). This topology affords

complete control over the magnitude and temperature behavior

of the logarithmic slope, decoupling it completely from E

K

.

A further step is needed to achieve the demodulation response,

required when the log amp converts an alternating input into a

quasi-dc baseband output. This is achieved by altering the g

m

cells used for summation purposes to also implement the rectifica-

tion function. Early discrete log amps based on the progressive

compression technique used half-wave rectifiers. This made

postdetection filtering difficult. The AD640 was the first

commercial monolithic log amp to use a full-wave rectifier, a

practice followed in all subsequent Analog Devices types.

These detectors can be modeled as essentially linear g

m

cells, but

produce an output current independent of the sign of the voltage

applied to the input of each cell; that is, they implement the

absolute value function. Because the output from the later A/0

stages closely approximates an amplitude symmetric square

wave for even moderate input levels (most stages of the amplifier

chain operate in a limiting mode), the current output from

each detector is almost constant over each period of the input.

Somewhat earlier detector stages produce a waveform having

only very brief dropouts, whereas the detectors nearest the

input produce a low level, almost sinusoidal waveform at twice

the input frequency. These aspects of the detector system result

in a signal that is easily filtered, resulting in low residual ripple

on the output.

INTERCEPT CALIBRATION

All monolithic log amps from Analog Devices include accurate

means to position the intercept voltage, V

X

(or equivalent power for

a demodulating log amp). Using the scheme shown in Figure 26,

the basic value of the intercept level departs considerably from

that predicted by the simpler analyses given earlier. However,

the intrinsic intercept voltage is still proportional to E

K

, which is

PTAT (see Equation 5). Recalling that the addition of an offset to

the output produces an effect that is indistinguishable from a

change in the position of the intercept, it is possible to cancel

the left-right motion of V

X

resulting from the temperature

variation of E

K

. Do this by adding an offset with the required

temperature behavior.

The precise temperature shaping of the intercept positioning offset

results in a log amp having stable scaling parameters, making it a

true measurement device, for example, as a calibrated received

signal strength indicator (RSSI). In this application, the user is

more interested in the value of the output for an input waveform

that is invariably sinusoidal. Although the input level can alterna-

tively be stated as an equivalent power, in dBm, be sure to work

carefully. It is essential to know the load impedance in which

this power is presumed to be measured.

In radio frequency (RF) practice, it is generally safe to assume a

reference impedance of 50 in which 0 dBm (1 mW) corresponds

to a sinusoidal amplitude of 316.2 mV (223.6 mV rms). The

intercept can likewise be specified in dBm. For the AD8307, it is

positioned at −84 dBm, corresponding to a sine amplitude of 20 µV.

It is important to bear in mind that log amps do not respond to

power, but to the voltage applied to their input.

The AD8307 presents a nominal input impedance much higher

than 50 (typically 1.1 k low frequencies). A simple input

matching network can considerably improve the sensitivity of

this type of log amp. This increases the voltage applied to the

input and thus alters the intercept. For a 50 match, the voltage

gain is 4.8 and the entire dynamic range moves down by 13.6 dB

(see Figure 35). Note that the effective intercept is a function of

waveform. For example, a square wave input reads 6 dB higher

than a sine wave of the same amplitude and a Gaussian noise

input 0.5 dB higher than a sine wave of the same rms value.

OFFSET CONTROL

In a monolithic log amp, direct coupling between the stages is

used for several reasons. First, this avoids the use of coupling

capacitors, which typically have a chip area equal to that of a

basic gain cell, thus considerably increasing die size. Second, the

capacitor values predetermine the lowest frequency at which the

log amp can operate; for moderate values, this can be as high as

30 MHz, limiting the application range. Third, the parasitic

(backplate) capacitance lowers the bandwidth of the cell, further

limiting the applications.

However, the very high dc gain of a direct-coupled amplifier

raises a practical issue. An offset voltage in the early stages of

the chain is indistinguishable from a real signal. For example, if

it were as high as 400 V, it would be 18 dB larger than the

smallest ac signal (50 V), potentially reducing the dynamic

range by this amount. This problem is averted by using a global

feedback path from the last stage to the first, which corrects this

offset in a similar fashion to the dc negative feedback applied

around an op amp. The high frequency components of the

signal must be removed to prevent a reduction of the HF gain in

the forward path.