AD7785

Rev. 0 | Page 16 of 32

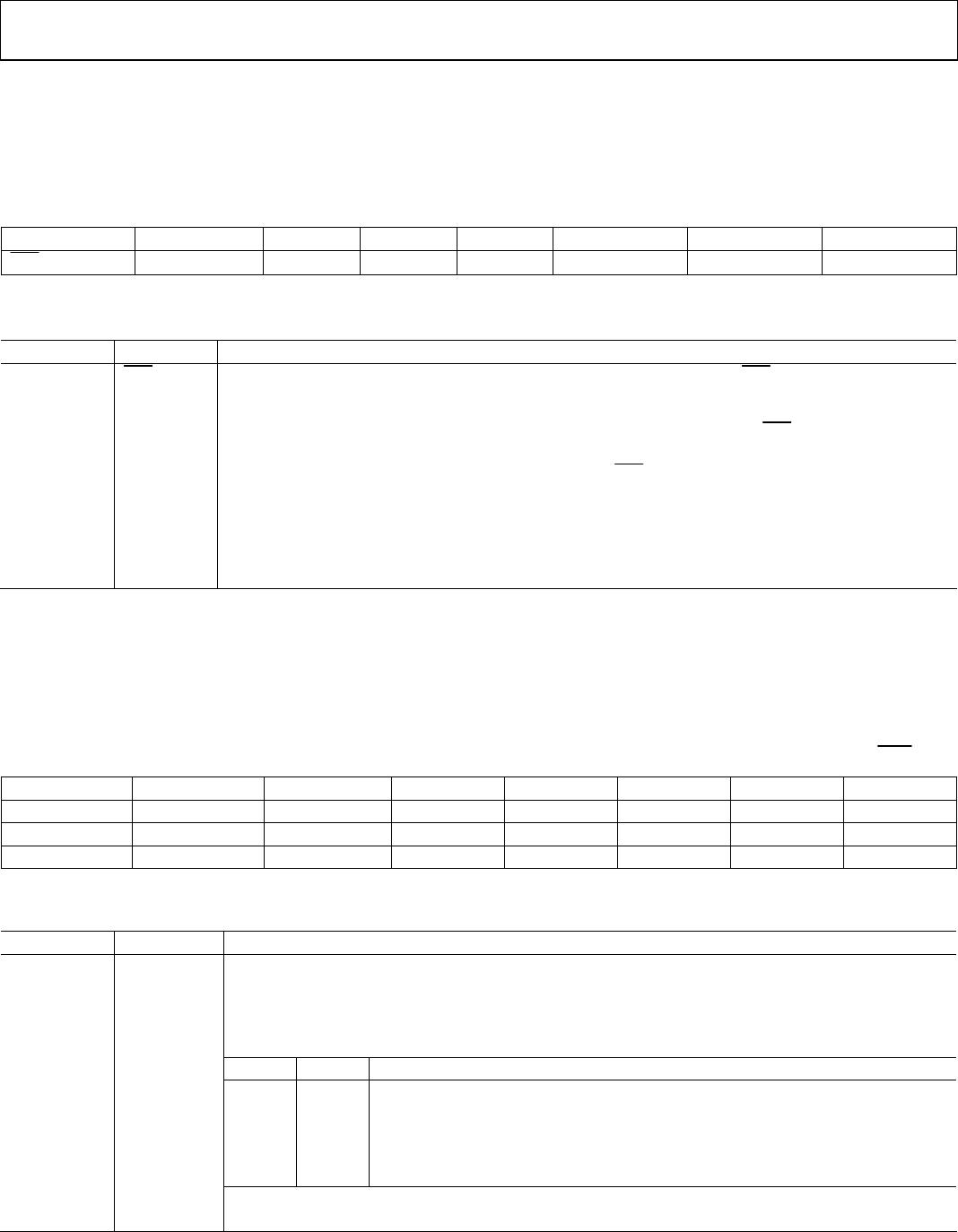

Table 13. Operating Modes

MD2 MD1 MD0 Mode

0 0 0

Continuous Conversion Mode (Default).

In continuous conversion mode, the ADC continuously performs conversions and places the result in the data

register.

RDY goes low when a conversion is complete. The user can read these conversions by placing the device in

continuous read mode, whereby the conversions are automatically placed on the DOUT line when SCLK pulses are

applied. Alternatively, the user can instruct the ADC to output the conversion by writing to the communications

register. After power-on, a channel change, or a write to the mode, configuration, or IO registers, the first conversion

is available after a period of 2/f

ADC

. Subsequent conversions are available at a frequency of f

ADC

.

0 0 1

Single Conversion Mode.

When single conversion mode is selected, the ADC powers up and performs a single conversion. The oscillator

requires 1 ms to power up and settle. The ADC then performs the conversion, which takes a time of 2/f

ADC

. The

conversion result is placed in the data register,

RDY goes low, and the ADC returns to power-down mode. The

conversion remains in the data register, and

RDY remains active low until the data is read or another conversion is

performed.

0 1 0

Idle Mode.

In idle mode, the ADC filter and modulator are held in a reset state, although the modulator clocks are still provided.

0 1 1

Power-Down Mode.

In power-down mode, all the AD7785 circuitry is powered down, including the current sources, burnout currents,

bias voltage generator, and CLKOUT circuitry.

1 0 0

Internal Zero-Scale Calibration.

An internal short is automatically connected to the enabled channel. A calibration takes 2 conversion cycles to

complete.

RDY goes high when the calibration is initiated and returns low when the calibration is complete. The

ADC is placed in idle mode following a calibration. The measured offset coefficient is placed in the offset register of

the selected channel.

1 0 1

Internal Full-Scale Calibration.

A full-scale input voltage is automatically connected to the selected analog input for this calibration.

When the gain equals 1, a calibration takes 2 conversion cycles to complete. For higher gains, 4 conversion cycles

are required to perform the full-scale calibration.

RDY goes high when the calibration is initiated and returns low when the calibration is complete. The ADC is placed

in idle mode following a calibration. The measured full-scale coefficient is placed in the full-scale register of the

selected channel.

Internal full-scale calibrations cannot be performed when the gain equals 128. With this gain setting, a system full-

scale calibration can be performed.

A full-scale calibration is required each time the gain of a channel is changed to minimize the full-scale error.

1 1 0

System Zero-Scale Calibration.

The user should connect the system zero-scale input to the channel input pins as selected by the CH2 to CH0 bits. A

system offset calibration takes 2 conversion cycles to complete.

RDY goes high when the calibration is initiated and

returns low when the calibration is complete. The ADC is placed in idle mode following a calibration. The measured

offset coefficient is placed in the offset register of the selected channel.

1 1 1

System Full-Scale Calibration.

The user should connect the system full-scale input to the channel input pins as selected by the CH2 to CH0 bits.

A calibration takes 2 conversion cycles to complete.

RDY goes high when the calibration is initiated and returns low

when the calibration is complete. The ADC is placed in idle mode following a calibration. The measured full-scale

coefficient is placed in the full-scale register of the selected channel.

A full-scale calibration is required each time the gain of a channel is changed.

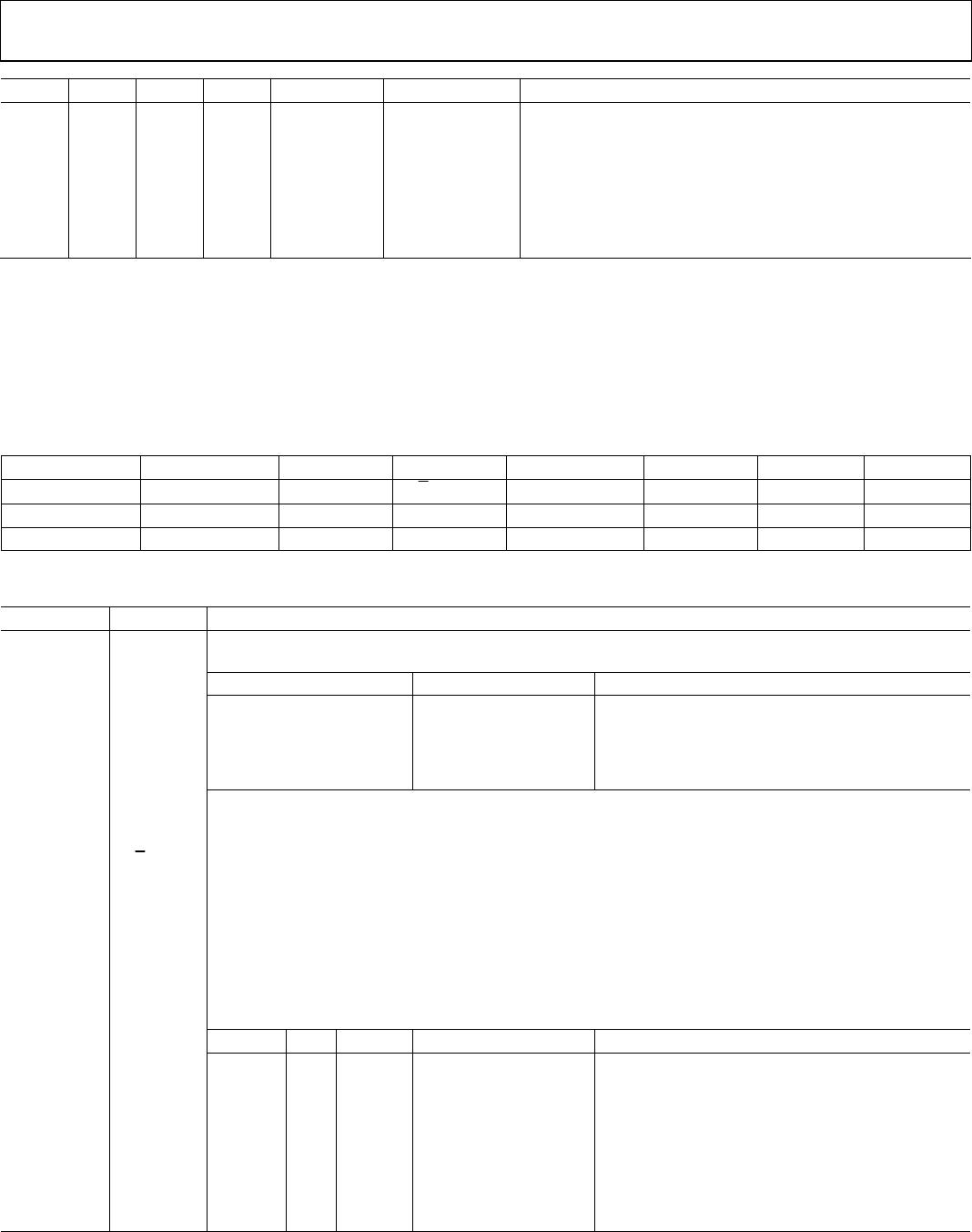

Table 14. Update Rates Available

FS3 FS2 FS1 FS0 f

ADC

(Hz) t

SETTLE

(ms) Rejection @ 50 Hz/60 Hz (Internal Clock)

0 0 0 0 x x

0 0 0 1 470 4

0 0 1 0 242 8

0 0 1 1 123 16

0 1 0 0 62 32

0 1 0 1 50 40

0 1 1 0 39 48

0 1 1 1 33.2 60

1 0 0 0 19.6 101 90 dB (60 Hz only)