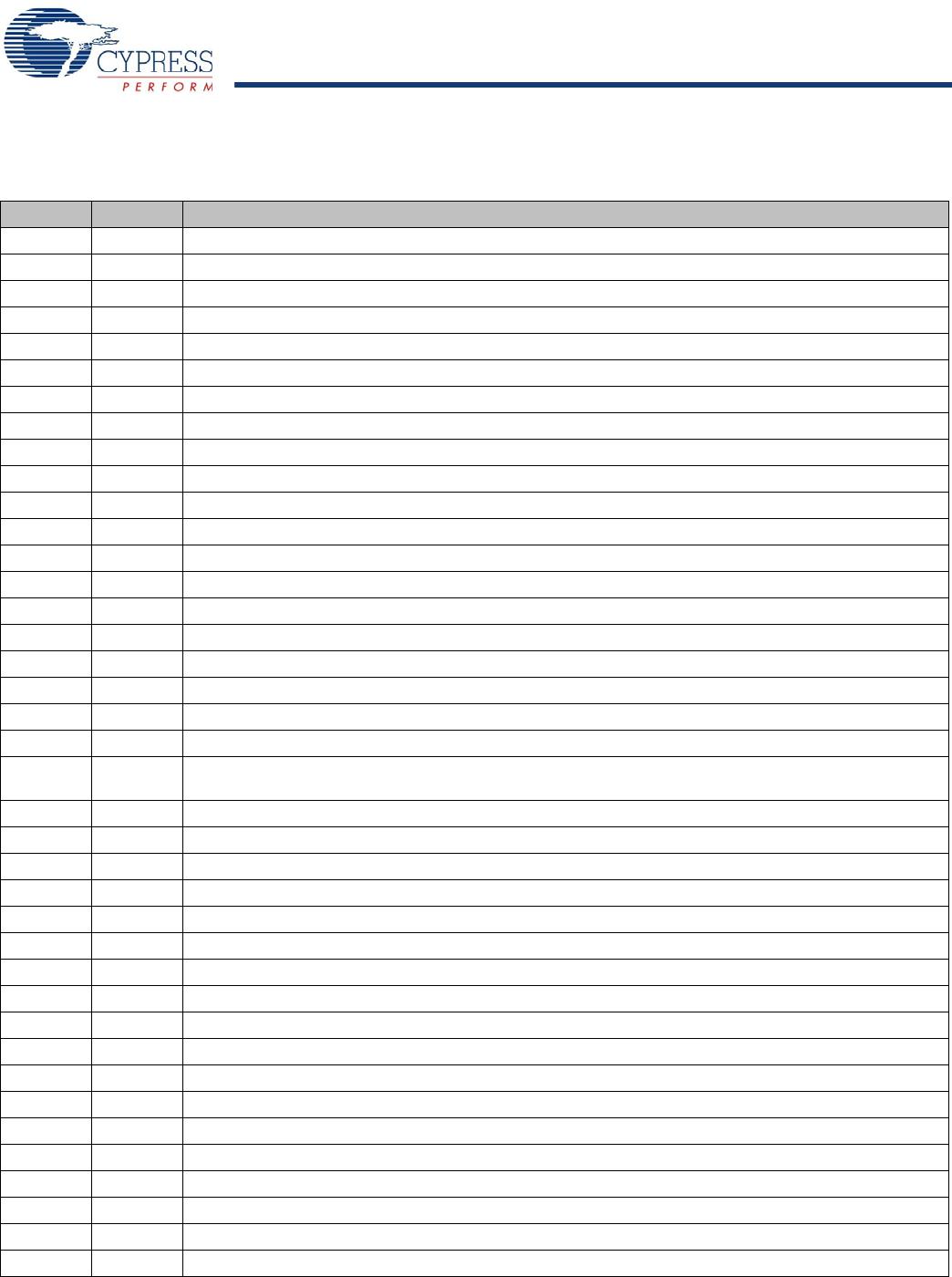

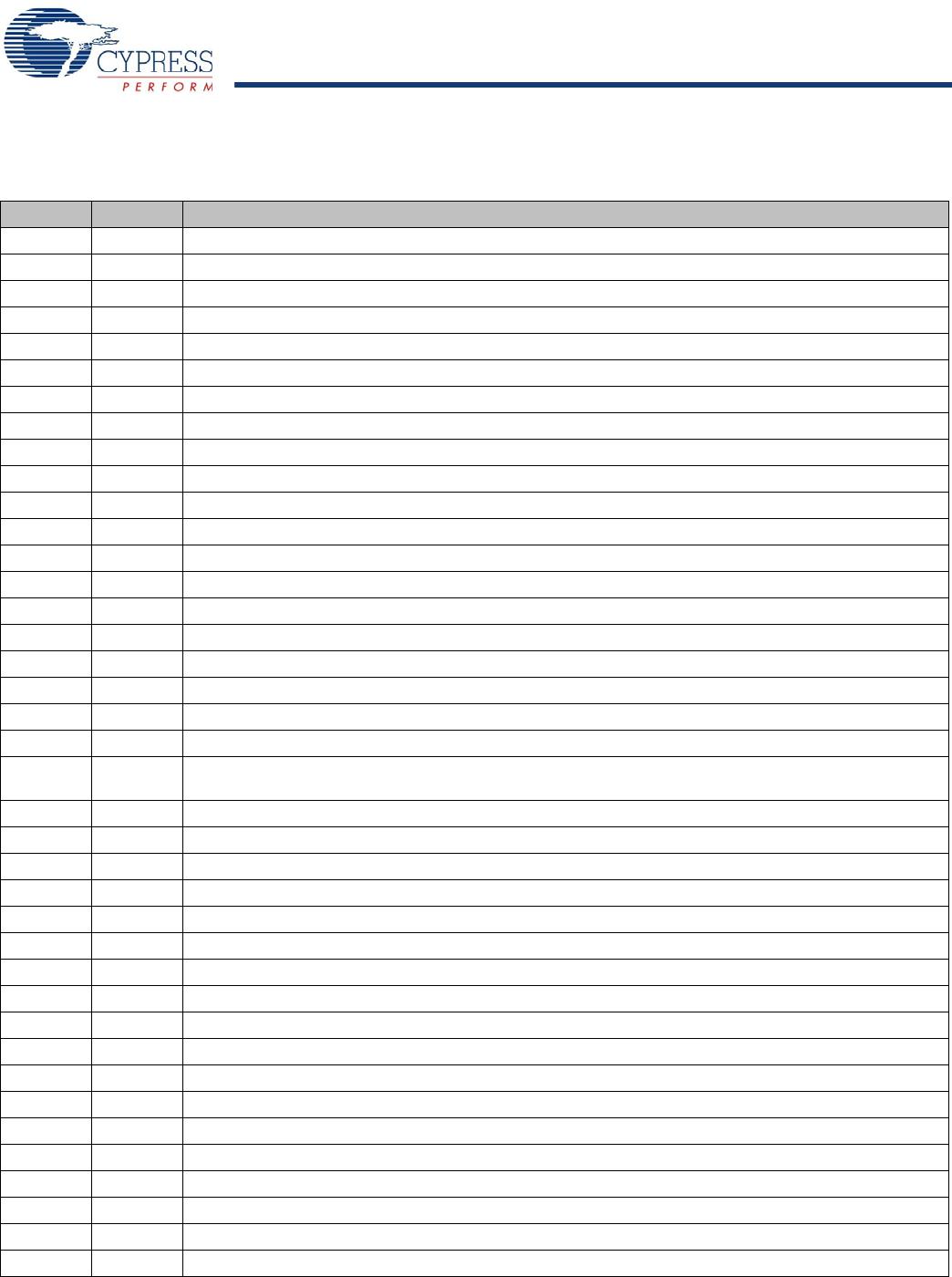

Document Number: 001-86331 Rev. ** Page 11 of 41

12 P0[3] Analog I/O, Digital I/O, Integrating input

13 FIFO FIFO status indicator bit

14 P0[1] Analog I/O, Digital I/O, Integrating input

15 VIN Unregulated input voltage to the on-chip low drop out (LDO) voltage regulator.

16 OCDOE OCD mode direction pin, NC

17 P2[7] Analog I/O, Digital I/O

18 P2[5] Analog I/O, Digital I/O, XTAL Out

19 P2[3] Analog I/O, Digital I/O, XTAL In

20 P2[1] Analog I/O, Digital I/O

21 P4[1] Analog I/O, Digital I/O

22 P3[7] Analog I/O, Digital I/O

23 SPI_SS Enable input for SPI, active low. Also used to bring device out of sleep state.

24 P3[5] Analog I/O, Digital I/O

25 P3[3] Analog I/O, Digital I/O

26 PKT Transmit/receive packet status indicator bit

27 P3[1] Analog I/O, Digital I/O

28 CLK Clock input for SPI interface

29 MOSI Data input for the SPI bus

30 MISO Data output (tristate when not active)

31 P1[7] Digital I/O, Analog I/O, I2C SCL, SPI SS

32 RST_N RST_N Low: Chip shutdown to conserve power. Register values lost

RST_N High: Turn on chip, registers restored to default value

33 P1[5] Digital I/O, Analog I/O, I2C SDA, SPI MISO

34 VDD Core power supply voltage. Connect all VDD pins to VOUT pin.

35 CCLK OCD CPU CLK OUTPUT, NC

36 HCLK OCD HIGH SPEED CLK, NC

37 VIN Unregulated input voltage to the on-chip low drop out (LDO) voltage regulator

38 P1[3] Digital I/O, Analog I/O, SPI CLK

39 VOUT 1.8 V output from on-chip LDO. Connect to all Vdd pins, do not connect to external loads.

40 P1[1] Digital I/O, Analog I/O, TC CLK, I2C SCL, SPI MOSI

41 GND Ground Pin

42 VDD Core power supply voltage. Connect all VDD pins to VOUT pin.

43 XTALO Output of the crystal oscillator gain block

44 XTALI Input to the crystal oscillator gain block

45 NC No Connect

46 TEST1 Reserved for factory test. Do not connect.

47 P1[0] Analog I/O, Digital I/O, TC DATA, I2C SDA

48 P1[2] Analog I/O, Digital I/O

49 P1[4] Analog I/O, Digital I/O, EXT CLK

50 VDD Core power supply voltage. Connect all VDD pins to VOUT pin.

Pin Definitions (continued)

This table gives the pin definitions.

[1, 2]

Pin No. Pin Name Description