Document Number: 001-86331 Rev. ** Page 27 of 41

AC I

2

C Specifications

The following table lists guaranteed maximum and minimum specifications for the entire voltage and temperature ranges.

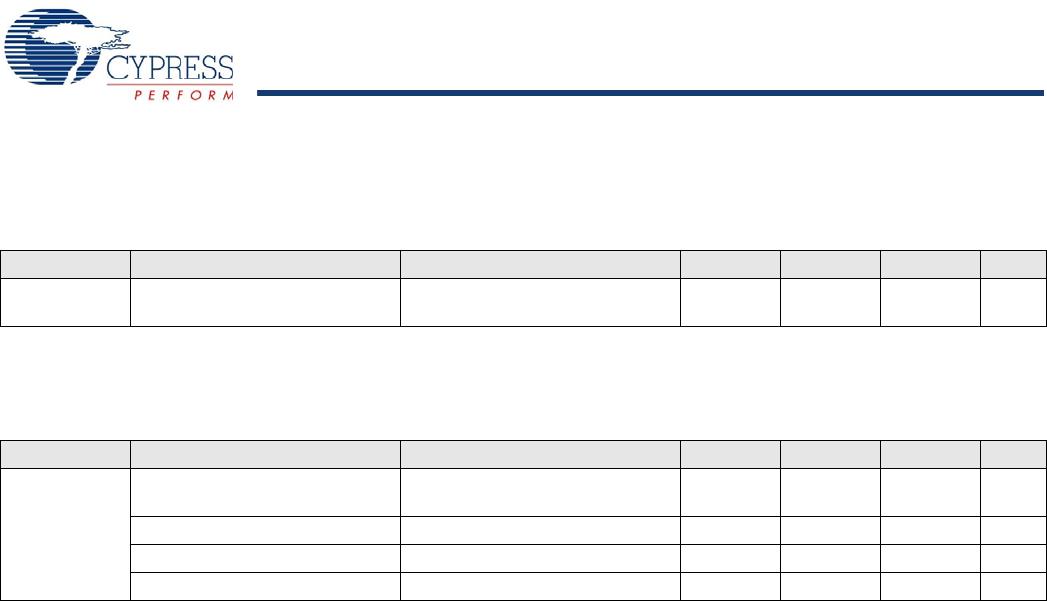

Figure 8. Definition for Timing for Fast/Standard Mode on the I

2

C Bus

Table 20. AC Characteristics of the I

2

C SDA and SCL Pins

Symbol Description

Standard Mode Fast Mode

Units

Min Max Min Max

f

SCL

SCL clock frequency 0 100 0 400 kHz

t

HD;STA

Hold time (repeated) START condition. After this period, the

first clock pulse is generated

4.0 – 0.6 – µs

t

LOW

LOW period of the SCL clock 4.7 – 1.3 – µs

t

HIGH

HIGH Period of the SCL clock 4.0 – 0.6 – µs

t

SU;STA

Setup time for a repeated START condition 4.7 – 0.6 – µs

t

HD;DAT

Data hold time 0 3.45 0 0.90 µs

t

SU;DAT

Data setup time 250 – 100

[11]

– ns

t

SU;STO

Setup time for STOP condition 4.0 – 0.6 – µs

t

BUF

Bus free time between a STOP and START condition 4.7 – 1.3 – µs

t

SP

Pulse width of spikes are suppressed by the input filter – – 0 50 ns

Note

11. A Fast-Mode I

2

C-bus device can be used in a standard mode I

2

C-bus system, but the requirement t

SU;DAT

250 ns must then be met. This automatically be the case

if the device does not stretch the LOW period of the SCL signal. If such device does stretch the LOW period of the SCL signal, it must output the next data bit to the

SDA line t

rmax

+ t

SU;DAT

= 1000 + 250 = 1250 ns (according to the Standard-Mode I

2

C-bus specification) before the SCL line is released.