13

FN8165.3

August 29, 2006

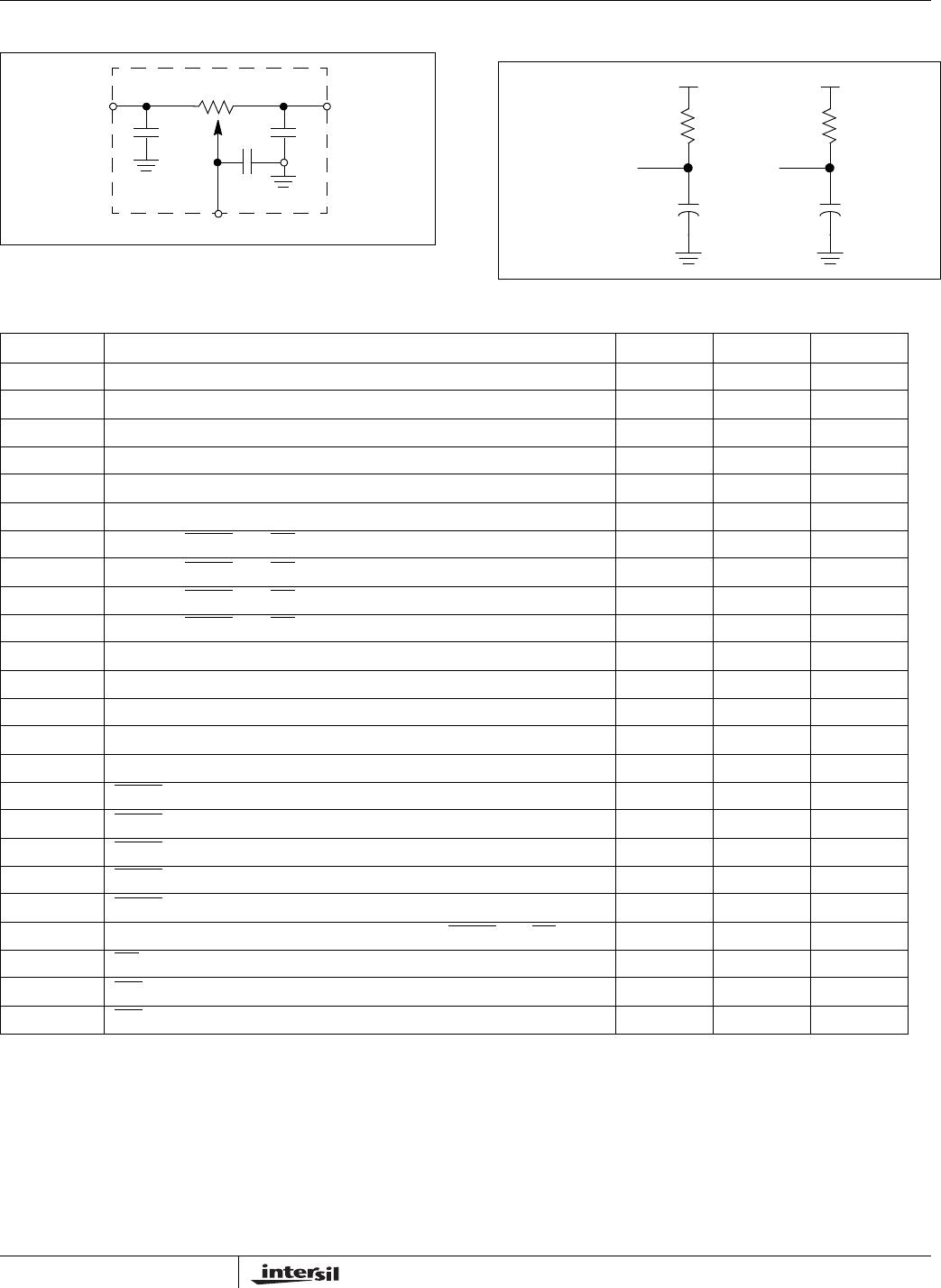

Circuit #3 SPICE Macro Model EQUIVALENT A.C. LOAD CIRCUIT

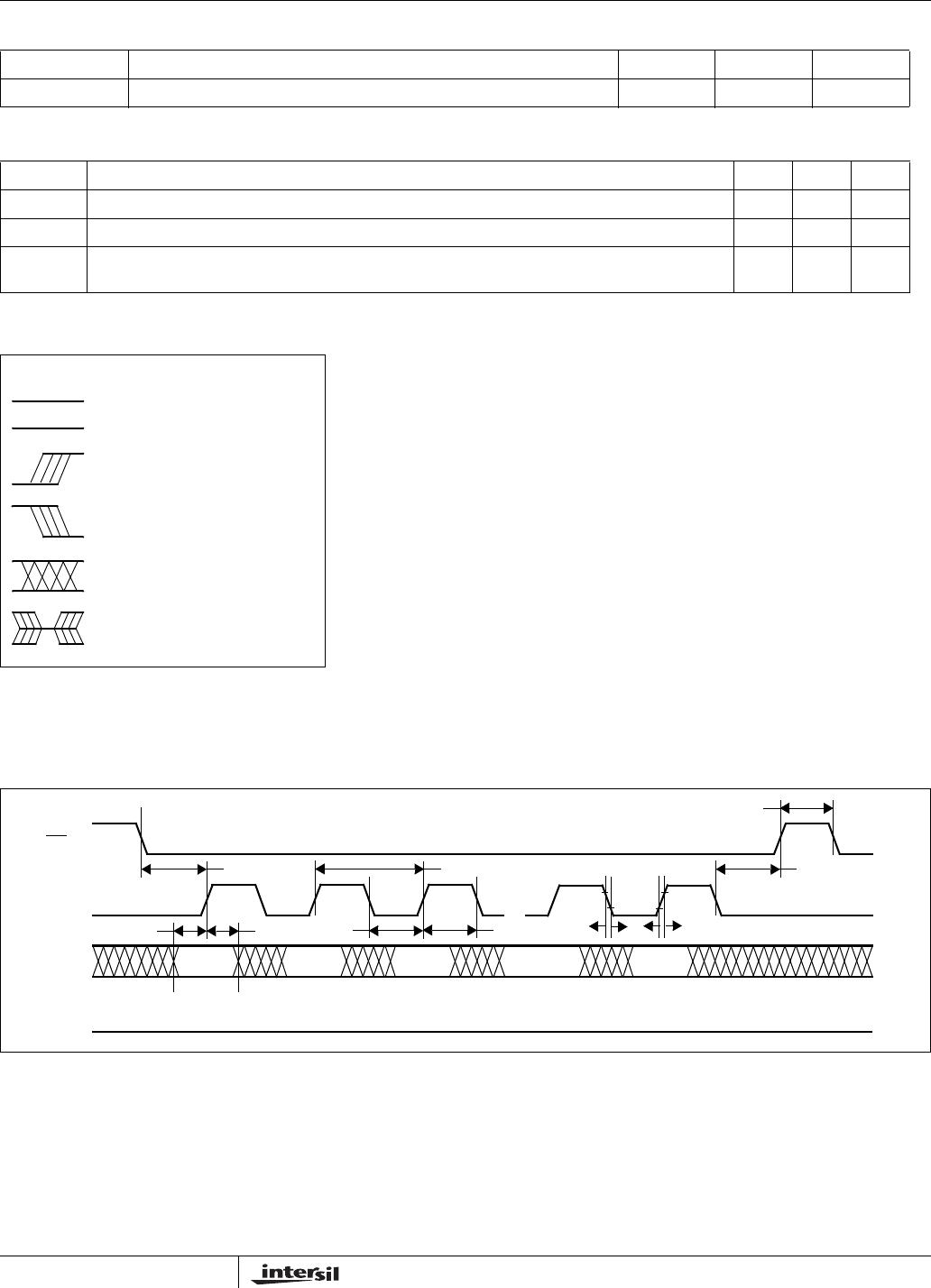

AC TIMING

10pF

R

H

R

TOTAL

C

H

25pF

C

W

C

L

10pF

R

W

R

L

5V

1533Ω

100pF

SDA Output

2.7V

100pF

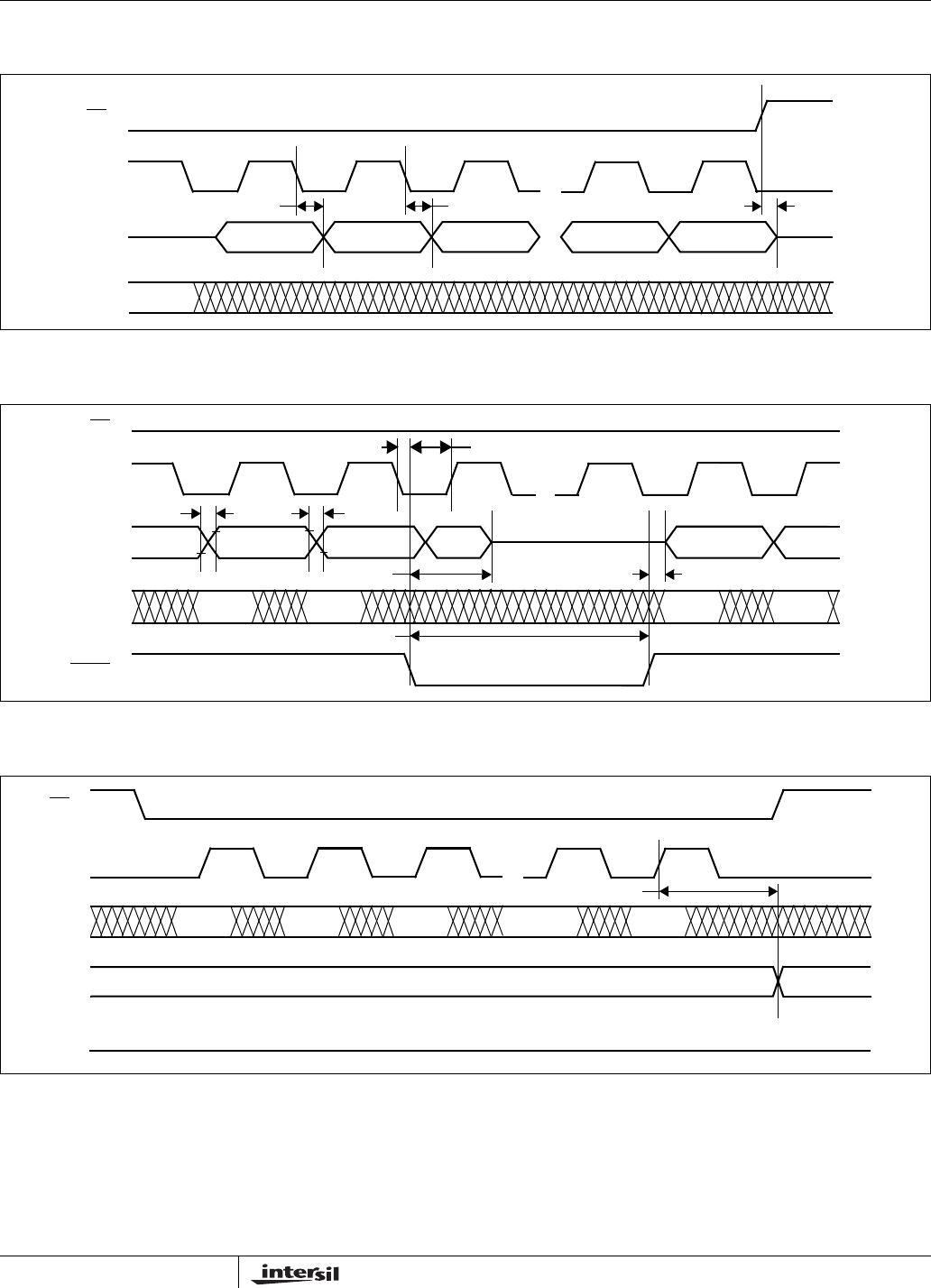

Symbol Parameter Min. Max. Unit

f

SCK

SSI/SPI clock frequency 2.0 MHz

t

CYC

SSI/SPI clock cycle time 500 ns

t

WH

SSI/SPI clock high time 200 ns

t

WL

SSI/SPI clock low time 200 ns

t

LEAD

Lead time 250 ns

t

LAG

Lag time 250 ns

t

SU

SI, SCK, HOLD and CS input setup time 50 ns

t

H

SI, SCK, HOLD and CS input hold time 75 ns

t

RI

SI, SCK, HOLD and CS input rise time 2 µs

t

FI

SI, SCK, HOLD and CS input fall time 2 µs

t

DIS

SO output disable Time 0 500 ns

t

V

SO output valid time 100 ns

t

HO

SO output hold time 0 ns

t

RO

SO output rise time 50 ns

t

FO

SO output fall time 50 ns

t

HOLD

HOLD time 400 ns

t

HSU

HOLD setup time 100 ns

t

HH

HOLD hold time 100 ns

t

HZ

HOLD low to output in high Z 100 ns

t

LZ

HOLD high to output in low Z 100 ns

T

I

Noise suppression time constant at SI, SCK, HOLD and CS inputs TBD ns

t

CS

CS deselect time 2 µs

t

WPASU

WP, A0 and A1 setup time 0 ns

t

WPAH

WP, A0 and A1 hold time 0 ns

X9250