8

FN8165.3

August 29, 2006

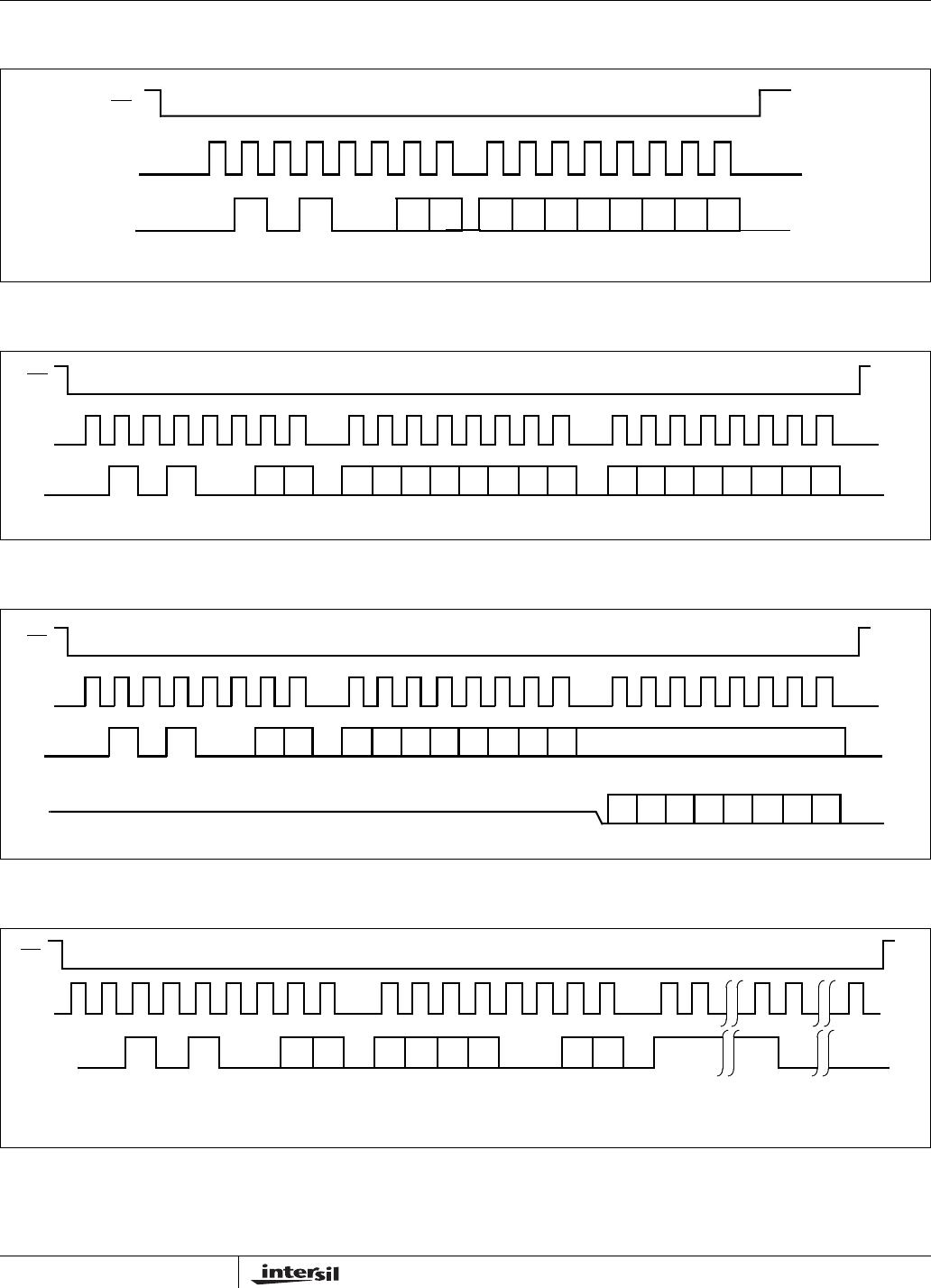

Figure 8. Increment/Decrement Timing Limits

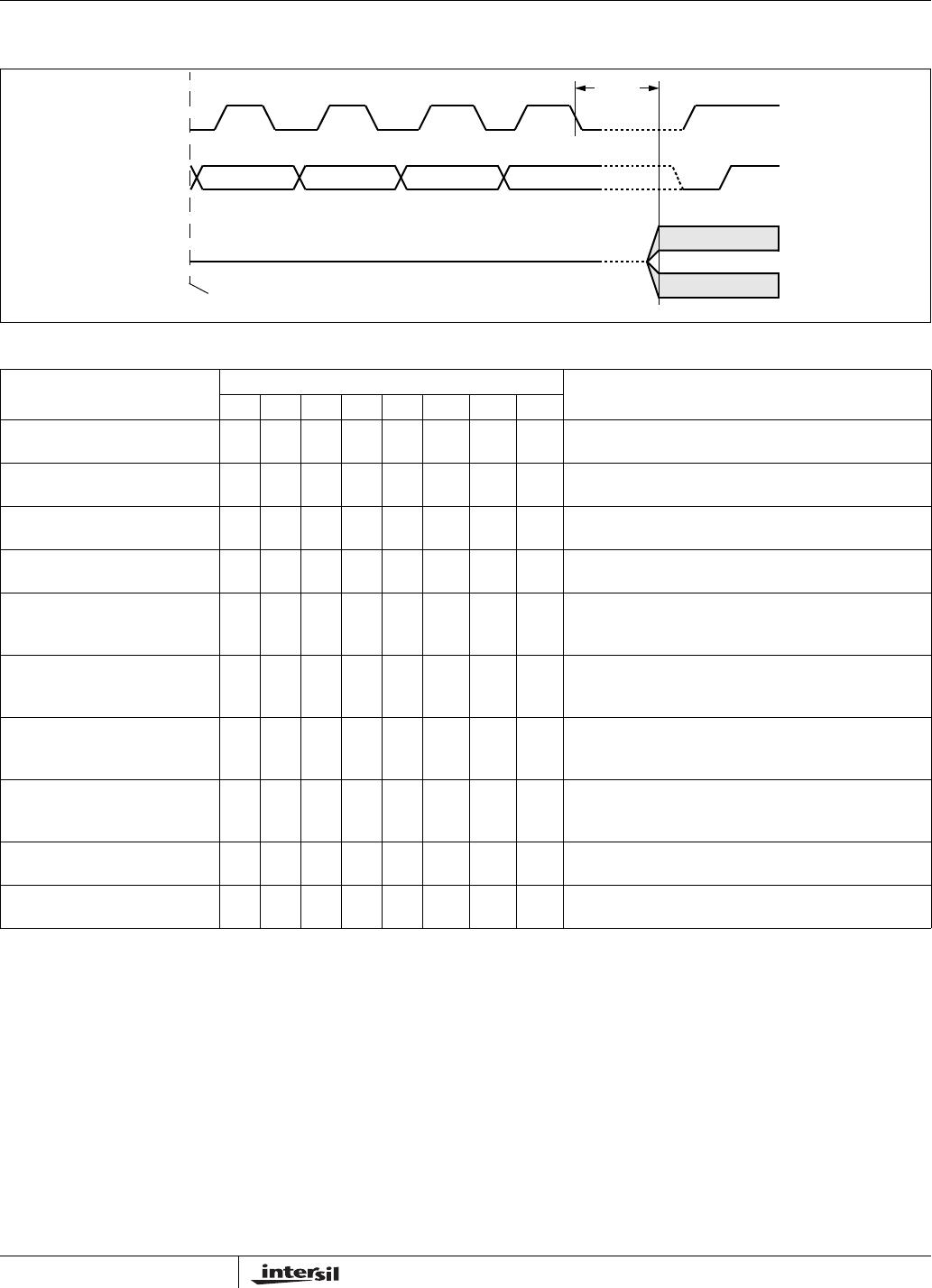

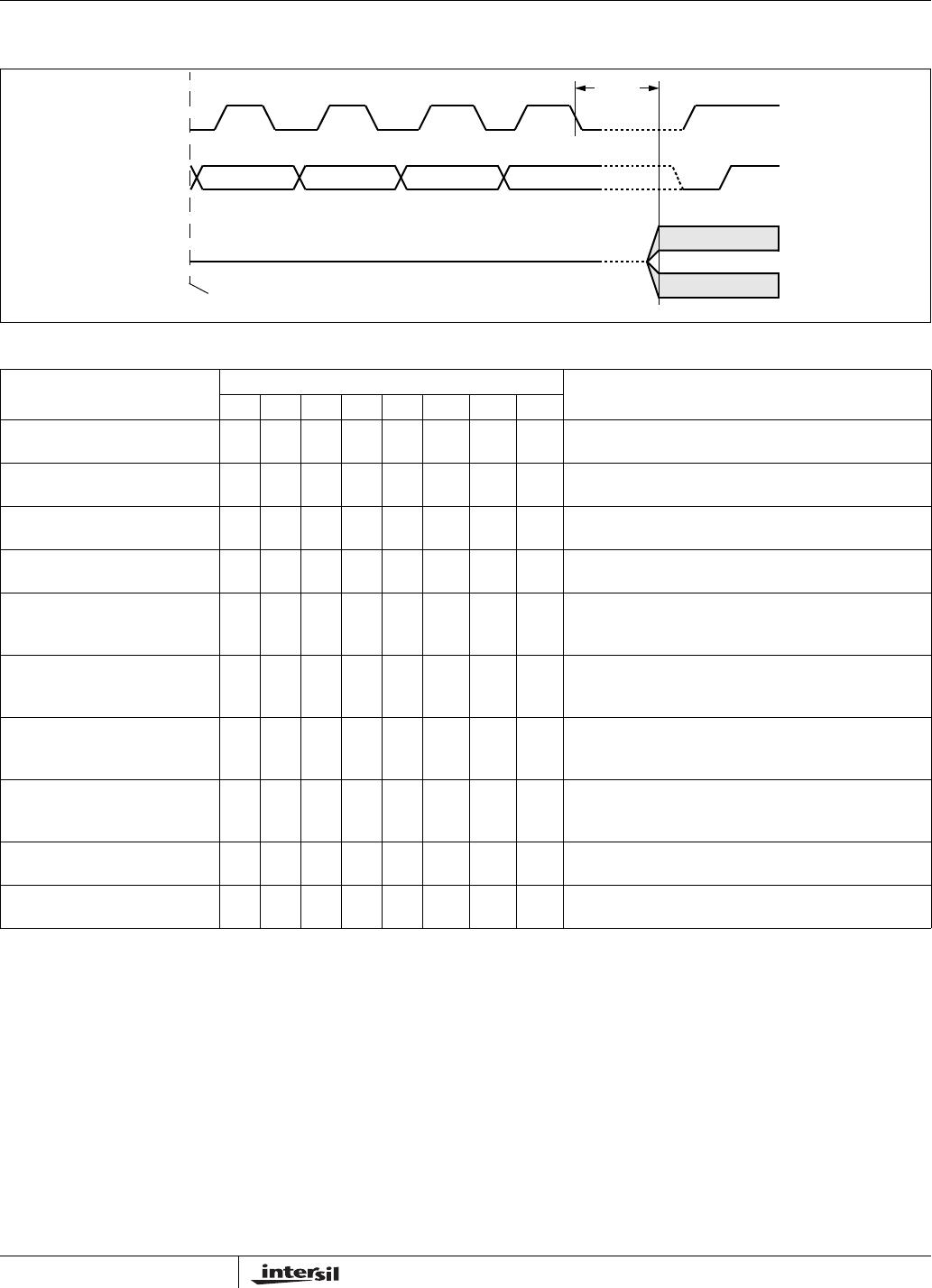

Table 1. Instruction Set

Instruction

Instruction Set

OperationI

3

I

2

I

1

I

0

R

1

R

0

P

1

P

0

Read Wiper Counter

Register

10010 0P

1

P

0

Read the contents of the Wiper Counter

Register pointed to by P

1

- P

0

Write Wiper Counter

Register

10100 0P

1

P

0

Write new value to the Wiper Counter Register

pointed to by P

1

- P

0

Read Data Register 1 0 1 1 R

1

R

0

P

1

P

0

Read the contents of the Data Register

pointed to by P

1

- P

0

and R

1

- R

0

Write Data Register 1 1 0 0 R

1

R

0

P

1

P

0

Write new value to the Data Register pointed to

by P

1

- P

0

and R

1

- R

0

XFR Data Register to

Wiper Counter Register

1101R

1

R

0

P

1

P

0

Transfer the contents of the Data Register

pointed to by R

1

- R

0

to the Wiper Counter

Register pointed to by P

1

- P

0

XFR Wiper Counter

Register to Data Register

1110R

1

R

0

P

1

P

0

Transfer the contents of the Wiper Counter

Register pointed to by P

1

- P

0

to the Register

pointed to by R

1

- R

0

Global XFR Data Register

to Wiper Counter Register

0001R

1

R

0

0 0 Transfer the contents of the Data Registers

pointed to by R

1

- R

0

of all four pots to their

respective Wiper Counter Register

Global XFR Wiper Counter

Register to Data Register

1000R

1

R

0

0 0 Transfer the contents of all Wiper Counter

Registers to their respective data Registers

pointed to by R

1

- R

0

of all four pots

Increment/Decrement

Wiper Counter Register

00100 0P

1

P

0

Enable Increment/decrement of the Wiper

Counter Register pointed to by P

1

- P

0

Read Status (WIP bit) 0 1010 0 0 1Read the status of the internal write cycle, by

checking the WIP bit.

SCK

SI

V

W

/R

W

INC/DEC CMD Issued

t

WRID

Voltage Out

X9250