20

All Intersil U.S. products are manufactured, assembled and tested utilizing ISO9000 quality systems.

Intersil Corporation’s quality certifications can be viewed at www.intersil.com/design/quality

Intersil products are sold by description only. Intersil Corporation reserves the right to make changes in circuit design, software and/or specifications at any time without

notice. Accordingly, the reader is cautioned to verify that data sheets are current before placing orders. Information furnished by Intersil is believed to be accurate and

reliable. However, no responsibility is assumed by Intersil or its subsidiaries for its use; nor for any infringements of patents or other rights of third parties which may result

from its use. No license is granted by implication or otherwise under any patent or patent rights of Intersil or its subsidiaries.

For information regarding Intersil Corporation and its products, see www.intersil.com

FN8165.3

August 29, 2006

X9250

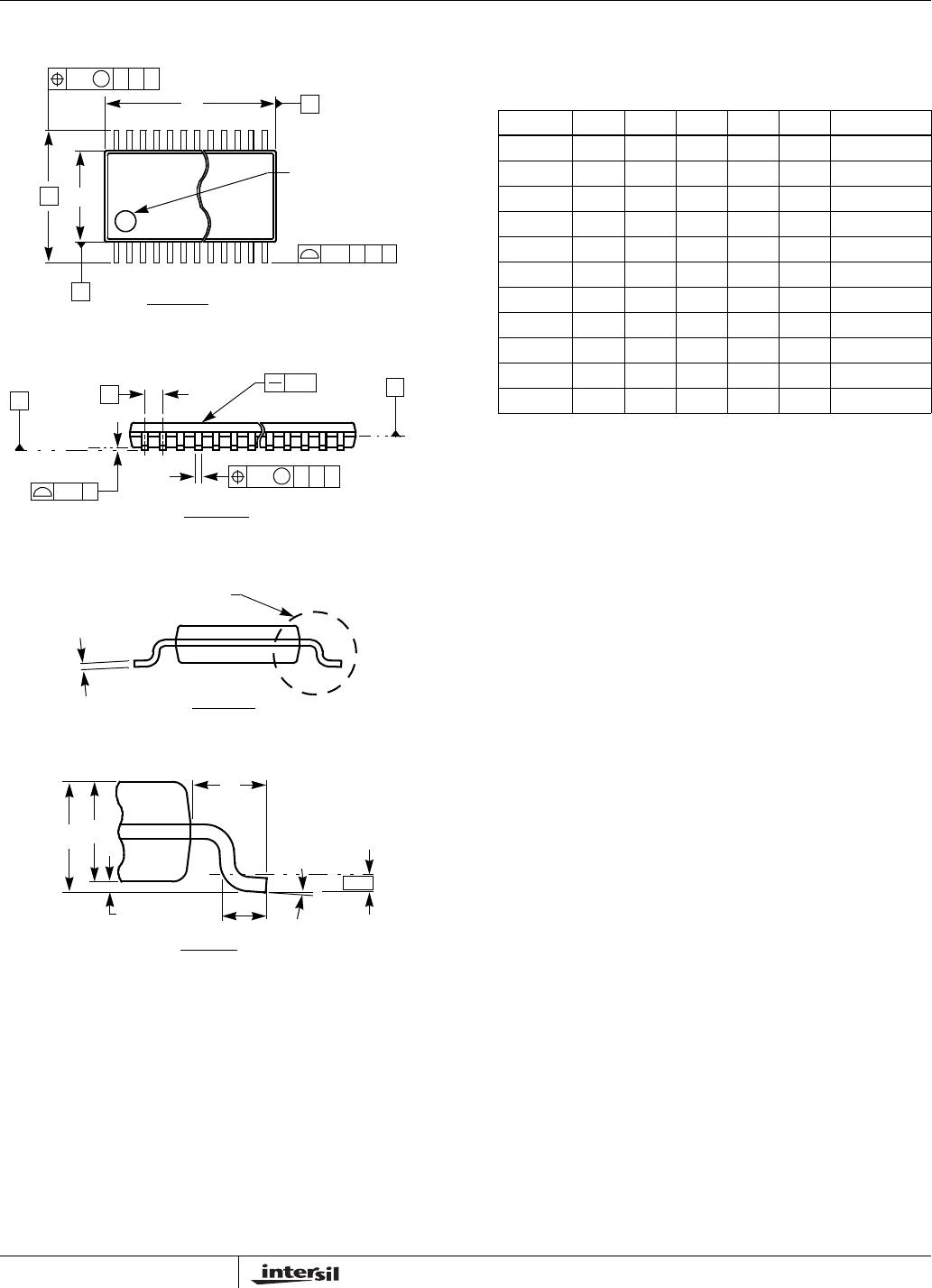

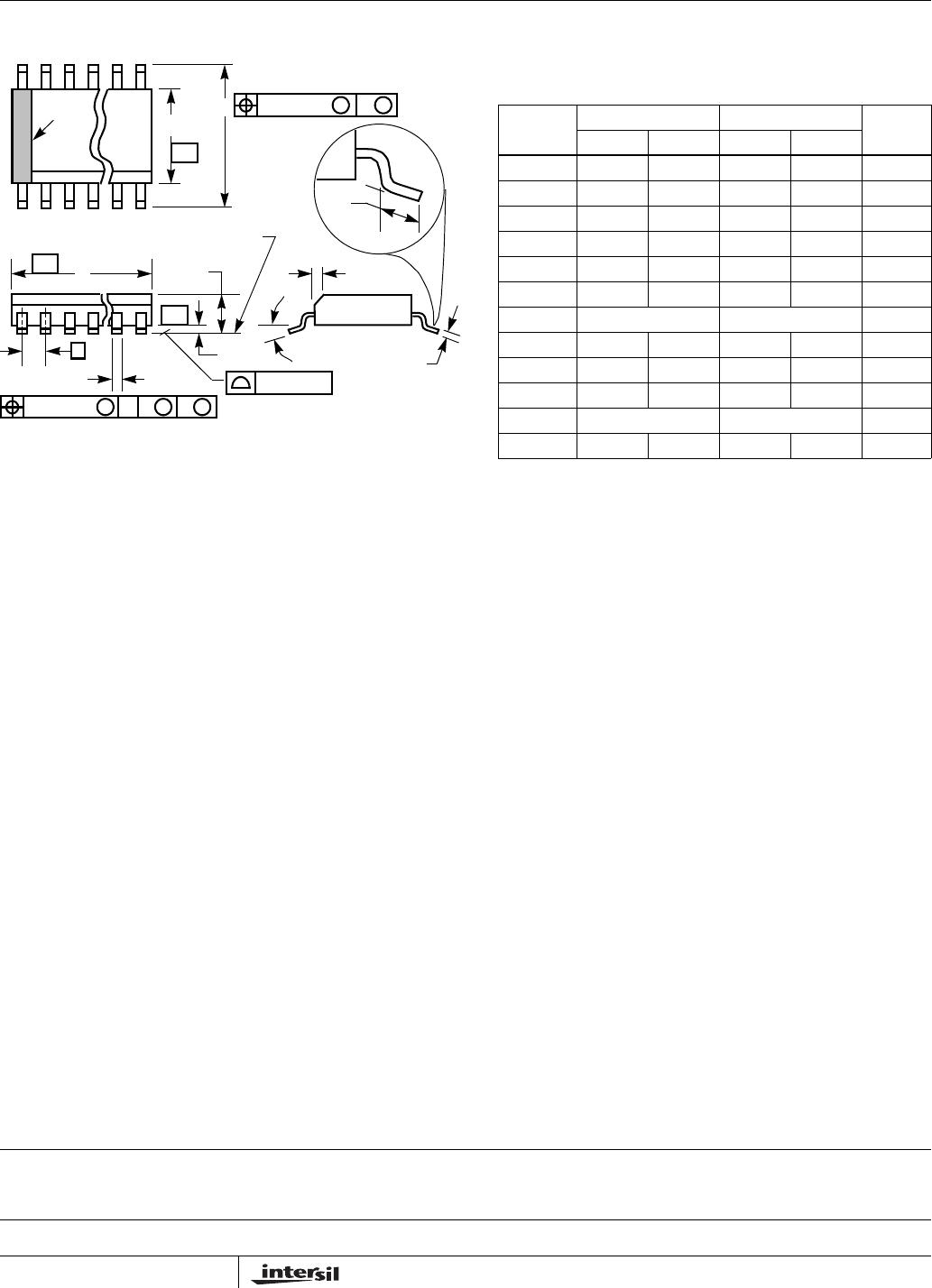

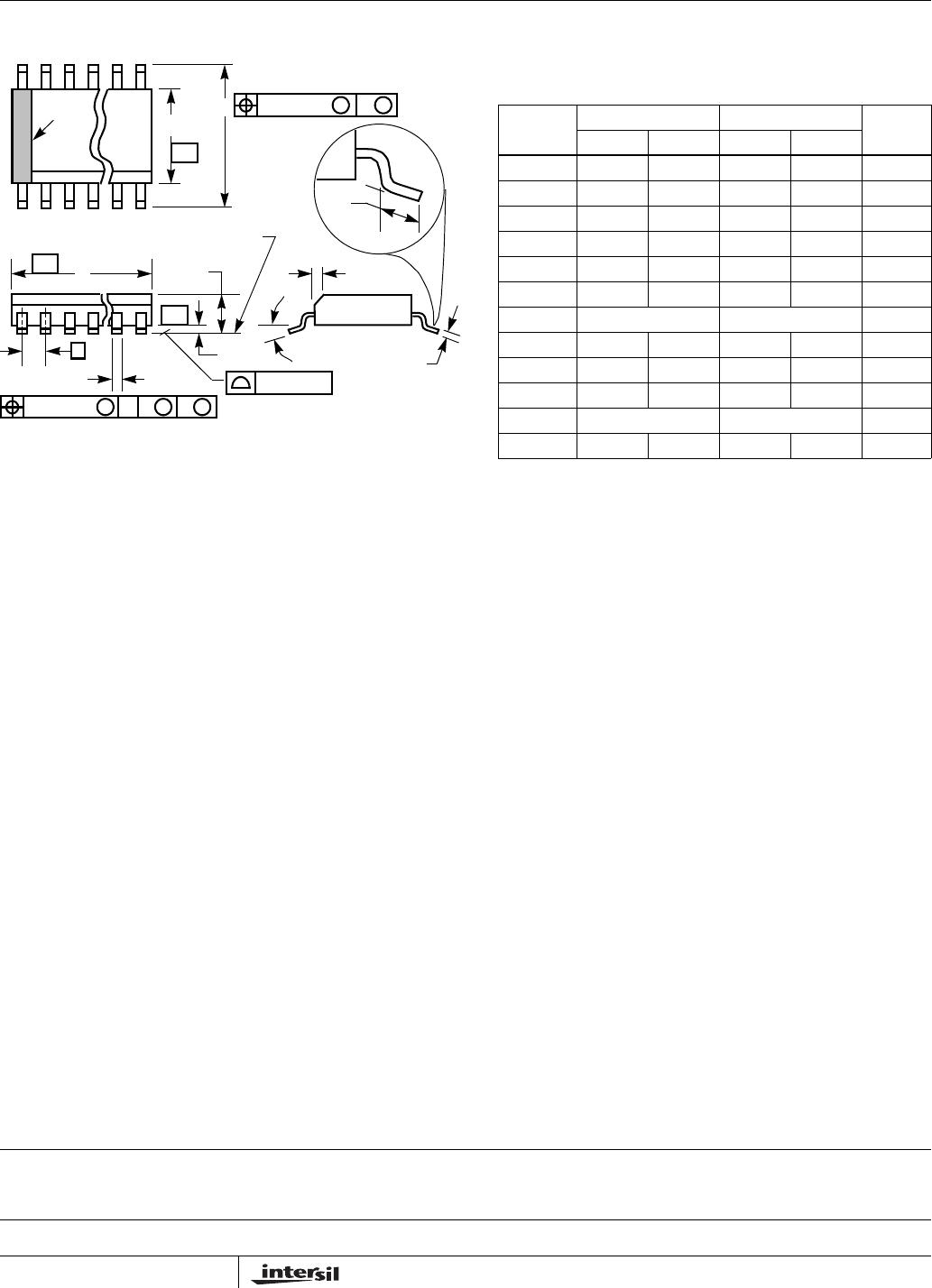

Small Outline Plastic Packages (SOIC)

NOTES:

1. Symbols are defined in the “MO Series Symbol List” in Section 2.2 of

Publication Number 95.

2. Dimensioning and tolerancing per ANSI Y14.5M-1982.

3. Dimension “D” does not include mold flash, protrusions or gate burrs.

Mold flash, protrusion and gate burrs shall not exceed 0.15mm

(0.006 inch) per side.

4. Dimension “E” does not include interlead flash or protrusions. Inter-

lead flash and protrusions shall not exceed 0.25mm (0.010 inch) per

side.

5. The chamfer on the body is optional. If it is not present, a visual index

feature must be located within the crosshatched area.

6. “L” is the length of terminal for soldering to a substrate.

7. “N” is the number of terminal positions.

8. Terminal numbers are shown for reference only.

9. The lead width “B”, as measured 0.36mm (0.014 inch) or greater

above the seating plane, shall not exceed a maximum value of

0.61mm (0.024 inch)

10. Controlling dimension: MILLIMETER. Converted inch dimensions

are not necessarily exact.

INDEX

AREA

E

D

N

123

-B-

0.25(0.010) C AM BS

e

-A-

L

B

M

-C-

A1

A

SEATING PLANE

0.10(0.004)

h x 45°

C

H

0.25(0.010) BM M

α

M24.3 (JEDEC MS-013-AD ISSUE C)

24 LEAD WIDE BODY SMALL OUTLINE PLASTIC PACKAGE

SYMBOL

INCHES MILLIMETERS

NOTESMIN MAX MIN MAX

A 0.0926 0.1043 2.35 2.65 -

A1 0.0040 0.0118 0.10 0.30 -

B 0.013 0.020 0.33 0.51 9

C 0.0091 0.0125 0.23 0.32 -

D 0.5985 0.6141 15.20 15.60 3

E 0.2914 0.2992 7.40 7.60 4

e 0.05 BSC 1.27 BSC -

H 0.394 0.419 10.00 10.65 -

h 0.010 0.029 0.25 0.75 5

L 0.016 0.050 0.40 1.27 6

N24 247

α

0° 8° 0° 8° -

Rev. 1 4/06