LTC4245

13

4245fa

OPERATIO

U

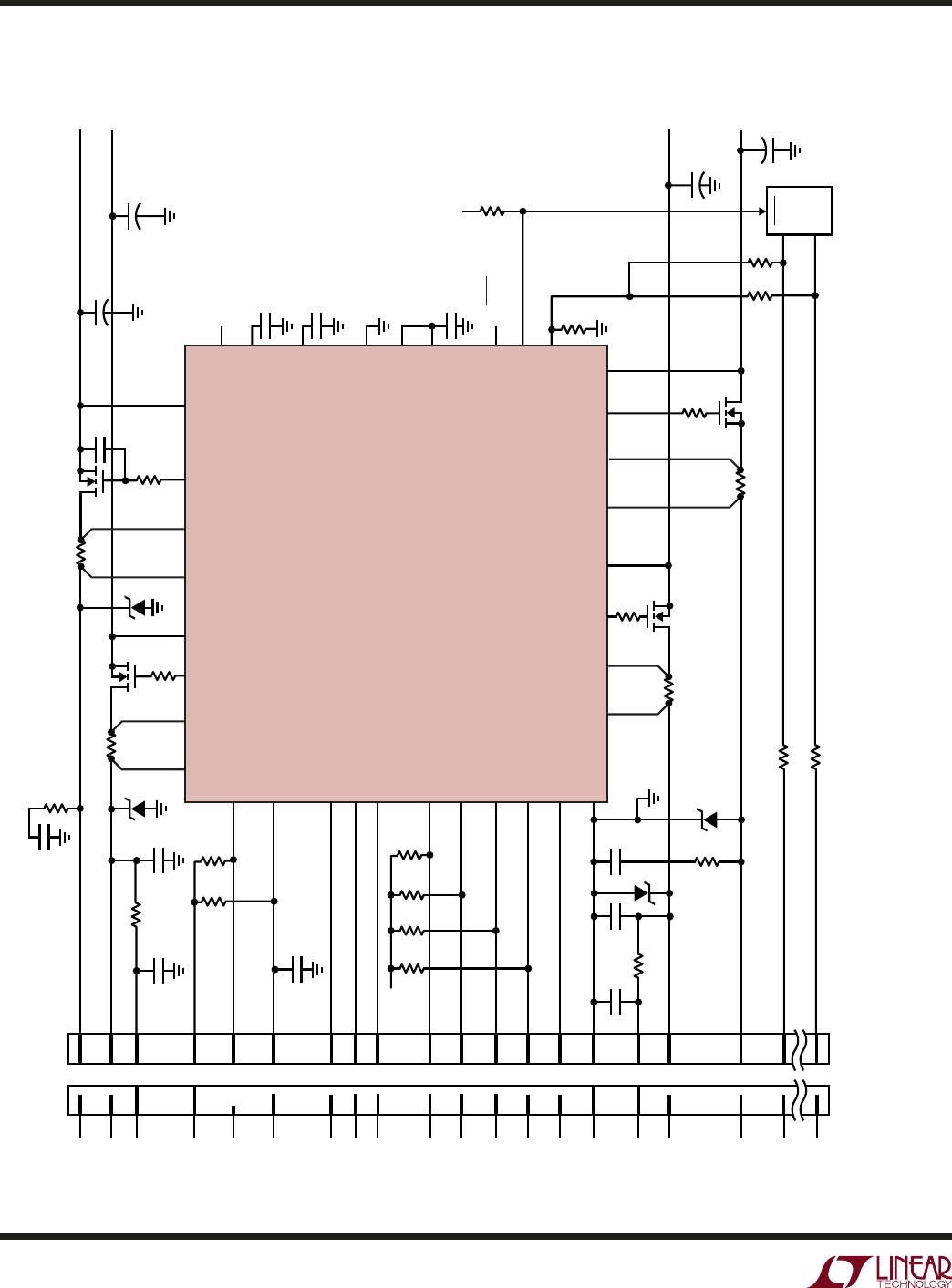

Start-Up

The LTC4245 is designed to turn a board’s supply voltages

on and off in a controlled manner, allowing the board to be

safely inserted or removed from a live backplane slot. When

a supply turn-on command is received, current sources

start pulling up the TIMER and SS pins. The 100μA I

TMR

current and the external TIMER capacitor determine the

time a supply can be in current limit during start-up. The

gate of a supply’s external N-channel MOSFET is servoed

by an amplifer (ACL

n

) so that the current, as indicated by

the sense resistor voltage drop, never exceeds an internal

current limit. This current limit rises at a rate determined

by I

SS

and the capacitor at the SS pin. A foldback circuit

determines the maximum value of the current limit and

reduces it to 30% of the maximum when a supply’s output

is shorted to ground. When the TIMER pin crosses 2.56V

it is reset to ground and the start-up timing cycle ends. If

a supply is still in current limit all gates are turned off, an

overcurrent fault is logged and the TIMER goes through

a cool-down timing cycle using 2μA for I

TMR

. Otherwise,

its circuit breaker (ECB

n

) is armed and the current limit

is raised to 3 times the circuit breaker threshold. The SS

pin is then reset by switch M2.

Any combination of the four supplies can be turned on

together or one after another. Whenever a supply is ramp-

ing up, its output voltage will affect, through the foldback

circuit, where the internal current limit ramp stops. The

default confi guration turns on all supplies together. If

sequence control bit C6 (Table 9) is set, the supplies turn

on in a 12V, 5V, 3.3V, –12V sequence. With this bit set,

the end of a supply ramp-up triggers the start of the next

one in the sequence. The I

2

C interface allows independent

on and off control for each supply through its On control

bit. Turn-off is simultaneous under fault conditions and

when using the ON or BD_SEL# pins.

At the end of the last start-up timing cycle, HEALTHY#

is pulled low by M3 if all supply outputs are above their

power bad thresholds. LOCAL_PCI_RST# which was held

low (M4), now follows PCI_RST#. The TIMER pin goes

through a PGI timeout cycle using 10μA for I

TMR

. The PGI

pin is sampled at the end of the cycle. If it is low, then

all external MOSFETs are shut-off, a PGI fault is logged

and TIMER goes through a cool-down cycle using 2μA

for I

TMR

. If PGI is high, the part enters the normal mode

of operation.

Normal Operation

During normal operation, the gates of the MOSFETs are

clamped about 6.2V above their sources. The 12V gate

driver uses a charge pump, the 5V and 3.3V gate drive is

derived from 12V

IN

and the –12V gate drive from INTV

CC

.

Each supply is continuously monitored for undervoltage,

overcurrent and power bad conditions. Overcurrent moni-

toring consists of an electronic circuit breaker comparator

(ECB

n

) and an active current limit circuit (ACL

n

) set at 3x the

ECB threshold. Undervoltage and overcurrent faults cause

all MOSFETs to be shut off. A power bad condition causes

HEALTHY# to go high impedance and LOCAL_PCI_RST#

to pull low, without shutting off the MOSFETs. If the PGI

pin is not disabled (register bit C3 not set), then PGI pin

going low will also shut off all MOSFETs.

ADC

Included in the LTC4245 is an 8-bit A/D converter. The

converter has a 13-input multiplexer to select between

input, output and current sense voltage of each supply,

and the GPIO channel. The ADC can either cycle through

all channels or measure a channel on-demand.

Serial Interface

An I

2

C interface is provided to read from or write to the

status, control and A/D registers. It allows the host to poll

the device and determine if faults have occurred. If the

ALERT# line is used as an interrupt, the host can respond

to a fault in real time. The LTC4245 I

2

C interface slave ad-

dress is decoded using the ADR0 to ADR3 pins.

Confi guration, GPIO and Precharge

The three-state CFG pin can be used to disable the V

EE

undervoltage lockout, power bad and foldback functions.

It can also convert the 5V undervoltage, power bad and

ADC levels to 3.3V levels. The GPIO1 to GPIO3 pins can

be used as general purpose inputs or outputs (M5 to

M7). One of the pins can also be multiplexed to the GPIO

channel of the ADC. A 1V reference voltage derived from

3V

IN

is provided at the PRECHARGE pin. This can be used

to pre-charge I/O lines on the board so as not to corrupt

the backplane bus.